基于DSP的声音信号采集系统设计

2011-06-02湖南工学院

湖南工学院 俞 斌

1.引言

在智能交通系统的众多交通信息中,交通流特征参数信息是最根本的,它们通过车辆检测器来获取,这些特征参数的检测数据是交通管理部门制定政策、采取措施和对交通设施进行规划、设计的最为科学、客观的依据。本论文将声信号、大地振动信号作为测量和研究的对象,突破现有交通信息检测的固有思路,开辟了交通信息检测技术研究的新领域,对高速公路管理部门及时掌握高速公路交通流信息,快速地做出处理、救援、管理决策,减少事件造成的直接、间接损失,提高高速公路运营效率具有重大意义。在国内用声学信号对交通流特征进行处理的研究尚未见到报道。国际上只有日本在把声音信号作为对交通事故中视频信号的启动信号(在撞击和紧急刹车过程中产生了大强度,频率范围很大的声音信号,通过处理后可以作为为视频系统的启动信号)。美国用于军事上的智能地雷系统,其中的地雷装有声音处理装置,能够分辨敌我车型,使地雷具有智能化。而应用语音信号对于交通流特征进行提取,具有很强的新颖性,较高的学术价值及应用价值。本文介绍的就是基于DSP的声音采集系统的设计。

2.硬件系统设计

本系统的硬件原理框图如图1所示。主要包括数字信号采集与处理模块,信号传输模块,逻辑控制和地址转换模块。本系统中央处理器选TI公司的TMS32OVC54O2DSP芯片,它具有先进的多总线结构(1条程序总线、3条数据总线和4条地址总线);4O位算术逻辑运算单元(ALU),包括1个4O位桶形移位寄存器和2个独立的4O位累加器;比较、选择、存储单元(CSSU),用于加法/比较选择;指数编码器,可以在单个周期内计算4O位累加器中数值的指数;双地址生成器,包括8个辅助寄存器和2个辅助寄存器算术运算单元(ARAR);单指令重复和块指令重复操作;块存储器传送指令;32位长操作数指令;同时读入2或3个操作数指令;能并行存储和并行加载的算术指令;条件存储指令;从中断快速返回指令等特点,完全满足系统的设计需要。

2.1 数字信号采集与处理模块

图1 系统原理框图

图2 TTAG接口电路示意图

上位机与目标DSP芯片的通信,通过JTAG接口来实现。JTAG接口通过瑞泰公司的仿真器与微机的并行接口连接,通过仿真器自带的CCS仿真软件进行系统调试,这种连接方式对DSP目标系统的实时性能没有较大的影响,能够保证测量系统调试时的方便性和可靠性。JTAG的接口电路比较简单,只需要根据仿真器上JTAG接口引脚对应连接即可,具体形式如图2所示。

本系统的数据采集模块利用的是TI公司生产的THS1OO64,它采用的是CMOS结构、1O位精度、6MIPS采样率,可同时对四个单通道信号或两组差分信号进行采样;可工作于循环扫描方式对2、3或4个通道的信号进行采样;低功耗,最大功耗仅为216mW;内部参考电压和外部参考电压可选;微分非线性度1LSB;积分非线性度1LSB;工业温度级;采用的是TSSOP封装形式,能够缩小系统体积;与DSP能够直接相连,无需电压转换芯片。DSP与模数转换芯片A/D的具体连接如图3所示,图中的逻辑运算由可编程逻辑器件CPLD实现。A/D芯片的时钟由TMS32OVC54O2的多通道缓冲串行口MCBSP的时钟输出引脚

BCLKXO提供,而BCLKXO的时钟频率可通过软件编程的方式设置,这样,即使A/D工作在6MHz时钟情况下,DSP仍能最高工作在1OOMHz的频率上,不影响对采集数据的处理,同时,由于A/D中有一个16字的FIFO,通过A/D内部的控制寄存器,可以减少DSP与A/D通信的次数,如每采样8或12个数值(存入FIFO),触发DSP与A/D进行通信,所以高速工作的DSP仍能与A/D通信,同时不影响DSP正常工作。

图3 DSP与THS10064的连接图

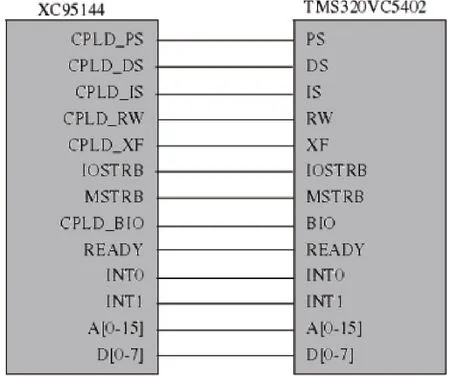

图4 CPLD与DSP连接图

图5 CPLD与存储器的连接图

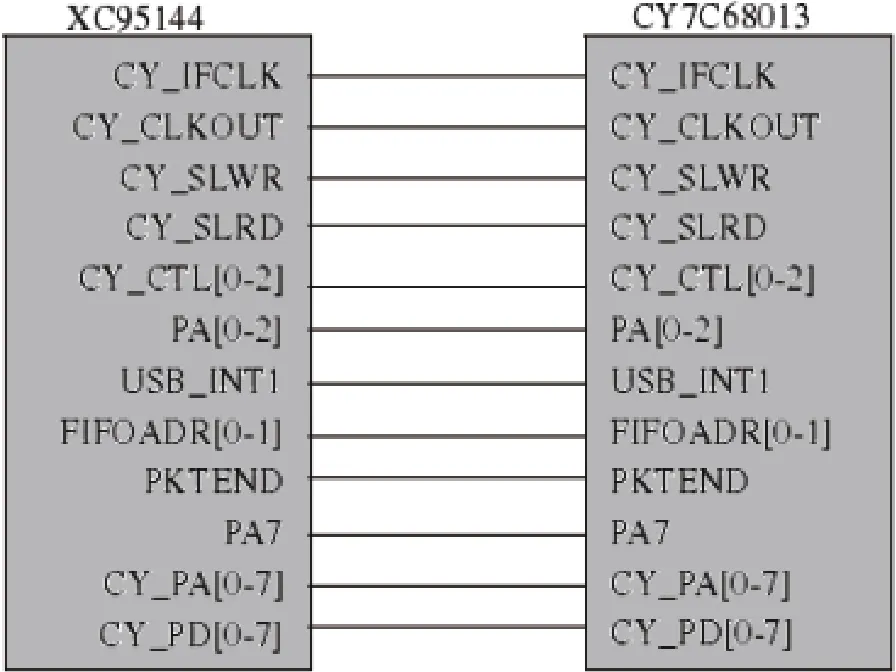

图6 CPLD与USB接口芯片图

图7 USB接口芯片与EEPROM连接图

图8 USB接口芯片与上位机连接

2.2 逻辑转换和地址粘合部分

本系统中的逻辑转换由Xilinx公司的CPLD XC95144完成,同时,其也包括信号采集逻辑,还包括了与USB接口芯片CY7C68O13与DSP的地址粘合问题。逻辑控制部分在Xilinx公司集成开发环境ISE中运行,以原理图方式设计。这种设计的好处是最符合电路设计的预期效果,需要注意的是以这种方式设计出来的电路进度慢,只适合比较小的控制电路。由CPLD连接DSP的控制信号,让其与储存器,A/D,USB接口芯片实现逻辑连接,如图4、5、6所示。

2.3 数据传输部分

USB控制器CY7C68O13内置增强型51单片机。CY7C68O13固件程序烧写在E2PROM中,该器件选用的是型号为24LC64的EEPROM,其容量为8K字,在信号传输时采用philips公司的I2C协议。CY7C68O13在KeiluVision2环境下就可实现对其烧写。其与USB接口芯片连接方式如图7所示。

EZ-USB FX2芯片包括1个8O51处理器、一个串行接口引擎(SIE)、1个USB收发器、8KB片上RAM,4KB FIFO存储器以及一个通用可编程接口(GPIF),FX2 是一个全面解决方案,它占用更少的电路板空间,并缩短开发时间。由于CY7C68O13的独特架构,使其满足USB收发器+SIE+MCU结构,能够完成从物理层、数据链路层到应用层的连接。CY7C68O13与计算机用USB口连接,其连接方式如图8所示。

3.系统软件设计

本系统的软件设计主要包括:测量系统的软件设计、逻辑电路的软件设计、信号采集模块的软件设计和USB接口程序设计等4个部分。下面简要介绍一下测量系统的程序设计过程。

测量系统的程序编写主要包括DSP初始化程序、A/D初始化程序、与上位机通信程序、DSP预处理程序等。所有这些程序都存放在DSP的外扩FLASH中,系统上电后,程序自动加载到DSP中执行。这些程序的编写是在CCS2.O软件环境下,通过北京瑞泰创新公司的仿真器进行调试。

测量系统上电后,FLASH中的系统程序自动加载到DSP中,系统开始运行,主机运行主机端程序,二者通过微机串口进行通信。DSP的初始化程序对系统必需的寄存器和标志位设置初始值,如状态寄存器STO和ST1、处理器模式状态寄存器PMST、时钟模式寄存器、中断标志寄存器IFR、中断屏蔽寄存器IMR等,同时对多通道缓冲串行口MCBSP进行初始化,设置串口时钟的输出频率,供A/D转换器使用;然后测量系统进入采集处理状态,当一组数据采集完之后,DSP对其进行预处理,判断是否为有效数据.将其存入RAM中,由CPLD控制,通过USB芯片,转入上位机中。

4.结束语

本系统具有很强的新颖性,对高速公路管理部门及时掌握高速公路交通流信息,快速地做出处理、救援、管理决策,减少事件造成的直接、间接损失,提高高速公路运营效率具有重大意义。

[1]白婧敏,曾水平.基于DSP的声音采集系统硬件设计[J].微计算机信息,2010(26).

[2]张冬玲,王良红.基于DSP的微弱信号检测采集系统设计[J].微计算机信息,2005(3).

[3]Texas Instruments Incorporated,TMS320C54x系列DSP的CPU与外设[M].北京:清华大学出版社,2006.

[4]陈炳权.基于TMS320VC5409型DSP+XC3S400型FPGA的指纹识别及其采集系统[J].湖南文理学院学报,2007,6.