一种基于FPGA的旋转机械非接触双向红外信号传输系统的实现

2011-05-06隆志远陈仁文朱莉娅

隆志远,陈仁文,朱莉娅

(南京航空航天大学航空宇航学院,南京210016)

在对旋转机械上的各种电气参数进行测量时,需要将测量数据在旋转机械的转动部件(转子)和固定部分(基座)之间进行传递。传统的旋转件上信号测量大都采用接触式方案,这种方案普遍使用集流器实现,存在着体积笨重、易受干扰、精度低、速度慢等缺点[1];而采用以红外、射频、激光为媒介的非接触式测量方法则克服了上述缺陷,因而愈来愈受到重视。其中,采用专用芯片作为射频收发模块进行长距离传输被应用较多。例如,CC24系列的射频芯片在无线传感器的构建中得到应用;利用nRF2401射频收发芯片的旋转件无线数据采集系统已用于航空发动机转子叶片的动态压力测量中[2]。

红外通信因其结构简单,价格低廉、性能稳定,在近距离、小角度、无障碍的中低速非接触式测量系统中获得了广泛应用。目前,根据 IrDA(Infrared Data Association,红外数据协会)规范,红外通信协议主要包括 SIR(Serial Infrared,串行红外传输)、FIR(Fast Infrared,高速红外传输)等方式。其中SIR方式通常需要在发送时对数据位进行3/16编码调制,接收时再解调解码还原出数据位,然后通过UART接口与上位机相连接以进行数据的传输,由于UART的极限速率为115 200 bit/s,所以限制了SIR方式的应用范围,因而多用在遥控或者低速率场合。FIR方式则放弃了对UART的依赖,采用4PPM(Pulse Position Modulation,脉冲位置调制)编解码方式进行红外传输,将传输的速率提高到4 Mbit/s,使得它可以被应用到较高速的场合。

本文介绍一种利用红外器件与FPGA进行多路信号非接触双向传输的方案。它借鉴数字同步通信的原理,通过在FPGA内部综合出性能出色的同步数字接收电路实现了数据在2 Mbit/s速率下的稳定双向传输,大幅提升了传输速率,满足了中低速情形下多路信号同步测量的需要,从而扩展了红外通信在旋转件测量领域的应用范围。

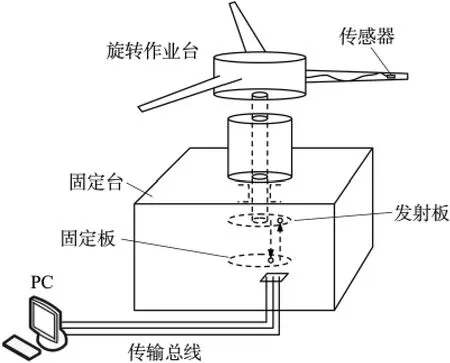

1 系统整体结构

整个系统包含两部分:①位于旋转侧的红外数据发射/接收电路板,实现对旋转件上各路数据的采集、发送以及接收来自于固定侧控制数据;②位于固定侧的红外数据发射/接收电路板,实现数据的接收和发送以及与PCI总线的接口控制。为了便于叙述,将数据从旋转侧传输到PC机这一流向称为上行通道;反之,称为下行通道。由于双向传输的对称性特点,下文将着重描述上行通道各环节的实现。

图1 系统整体示意图

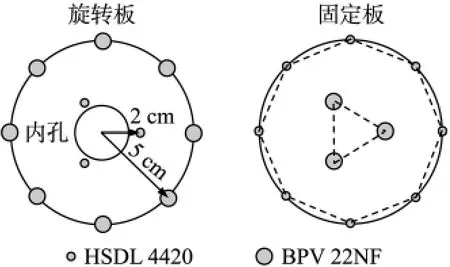

为了保证数据的双向传输,在旋转板和固定板上都同轴、对称地布置了红外发射管HSDL 4420和红外接收头BPV22NF。在HSDL 4420受三极管驱动输出情形下,红外接收头在0~9 cm,倾角小于24°的范围内可以有效接收光信号。由于实验平台旋转侧与固定侧的间距为6 cm左右,在考虑到红外接收的距离和角度因素后,对它们在板上进行了如图2所示的布置。内孔附近呈正三角形分布的器件对构成了数据上行通道;外圈则采用正八边形分布的器件对构成数据下行通道,各圈内的器件都以并联方式进行连接。内圈器件与外圈器件的间距为3 cm,在倾角为24°的范围内可以避免同时传输时红外光线间的相互干扰。这时,红外信号就可以在旋转侧与固定侧之间双向传输,避免了相互间的干扰。

图2 发射侧和接收侧的器件布置

值得一提的是,在高度一定的情况下,内圈与外圈的间距和各自所含的器件数目可以灵活地安排,这取决于红外接收器件的接收角度以及对干扰的承受能力,甚至BPV22NF的数量可以减少到一个。

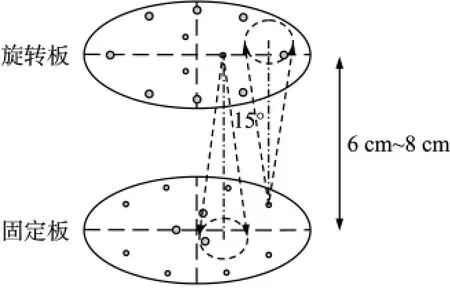

图3示意了处于最危险位置时的发射管仍位于接收管的有效接收范围内,故双向传输时不会相互影响。

图3 危险位置的情形

2 上行通道数据发送模块

2.1 数据采集模块

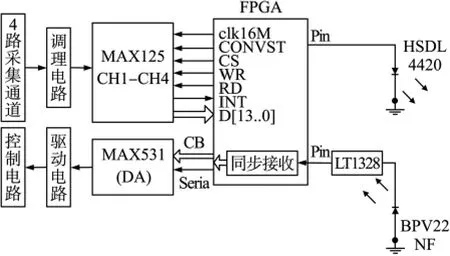

旋转板上主要有信号采集和发送电路,主要是由FPGA来控制AD和数据并串转换。它的作用是将从AD芯片MAX125进来的14 bit并行数据转换为2 Mbit/s的串行数据流输出,驱动红外发光管HSDL 4400发送数据。

图4 旋转板上电路原理框图

MAX125是一款支持多达4通道同步采集的AD芯片,具有14 bit精度,允许双极性输入,并行输出,单通道最高采样频率为250 ksample/s。4通道同步采集时,每通道最高采样速率为76 ksample/s[3]。

根据MAX125的器件手册,它在第一次进行模数转换前,需要事先进行配置以确定采样的通道数目,默认情况下,MAX125只对通道1(CH1)信号进行转换。在配置期间,CONVST保持高电平,在 CS、WR信号由低变高的同时,通过DATA引脚送出配置数据即可完成对MAX125工作方式的设置。此后,每次CONVST信号的由高变低都将启动一次模数转换。对于单通道采集工作方式,在3 μs后,MAX125将INT信号拉低,预示着此次转换的结束。FPGA可以通过检测INT信号的下降沿来对转换好的数据进行读取操作,数据将在RD的上升沿输出。如果是多通道采集,则最多经过4次读脉冲就可将4个通道的转换数据全部取走。

2.2 数据封装和发送

由于在接收侧采用数字锁相环[4]对数据流进行同步接收,所以在发送电路模块,必须将采集到的数据按照一定的帧格式来串行发送,这样才能在接收侧经过帧同步电路的检测判别出有效数据的起始位置。如果将一帧的长度设计得过长,在FPGA综合时将使帧同步输出信号进位延迟加大,可能造成锁存该信号时存在保持时间违规,导致帧同步失败;同时也会影响锁相环进入锁定状态和退入捕获状态的时间。时序分析报告表明,合适的帧长度显著减少了违规路径的数量。

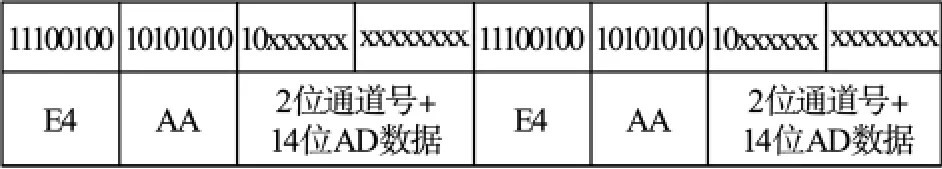

综合考虑后,本设计中将发送帧的长度定为32 bit,即4 byte。第1个字节为巴克码字“E4”,作为帧同步码[5];第2 字节为填充字节“10101010”;第3、4字节的高两位表示通道号(例如“00”表示通道1,“11”表示通道4),低14 bit为MAX125转换输出某通道的14 bit数据。之所以采用1和0交替是为了使锁相环处于交替调整状态,避免当全0和全1时锁相环出现失步的情形,这样就可以确保PLL在判别后面的16 bit数据时不出现误判。帧格式见下面图5。

图5 帧格式

值得指出的是,为了提高HSDL4400它的发射功率,可在FPGA输出引脚加由三极管构成的驱动电路来提高光发射功率,进而可以增加红外接收的距离。

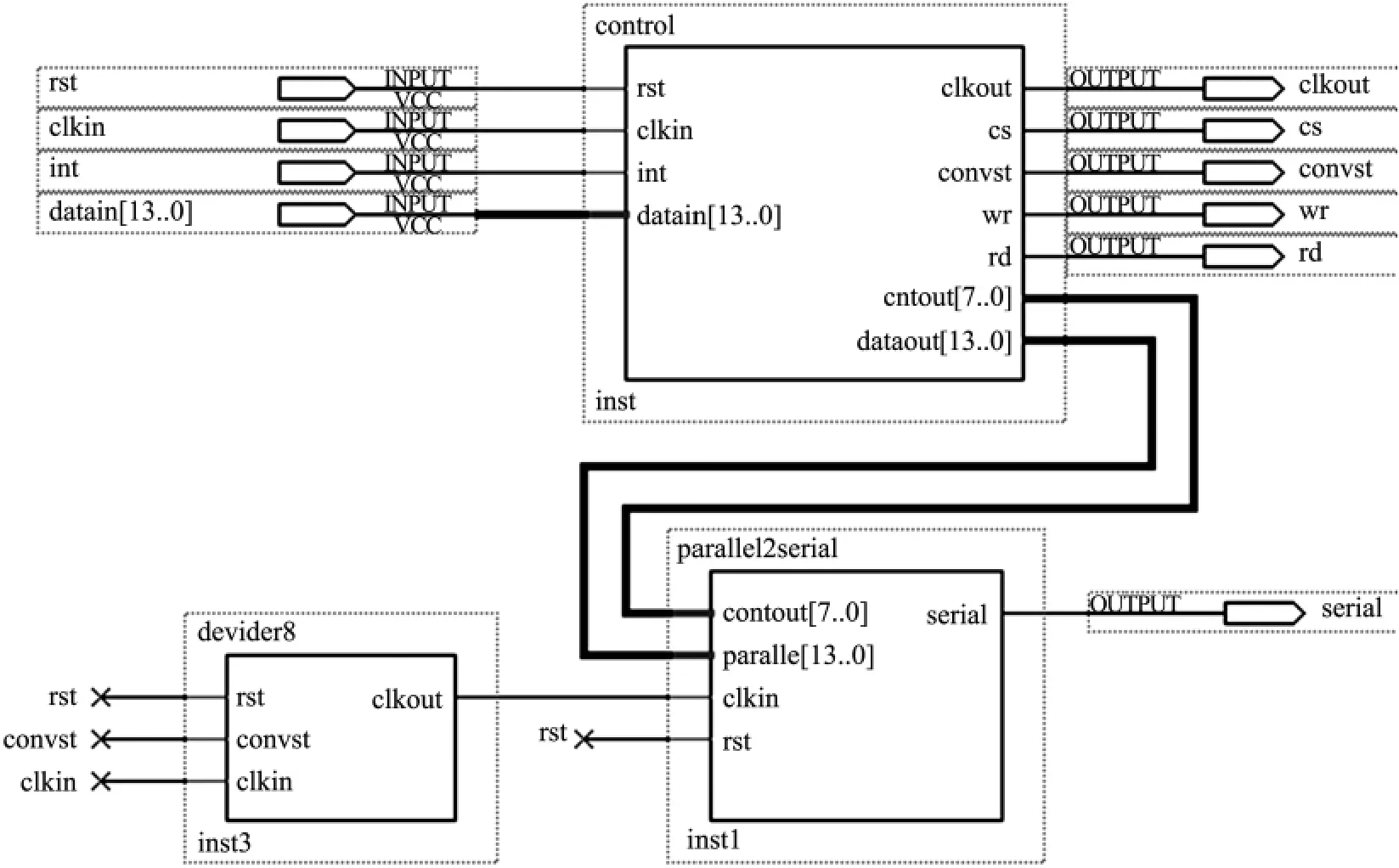

2.3 FPGA内部原理框图

由于接收侧数字锁相环的锁定频率为2 MHz,也就是可以捕捉2 Mbit/s的数字信号。为了适配2 Mbit/s的发送速率,在旋转板上用 FPGA控制MAX125的采样速率为64 ksample/s(2M/32=64 K)。由于发送板上的FPGA系统时钟为16 MHz,所以需要对它进行分频以得到2 M的时钟。最后,通过serial引脚输出串行数据。

图6中control模块内部含有一个状态机,它依据AD的工作时序操纵MAX125进行64 ksample/s的连续采样。parellel2serial模块则实现了对14 bit量化数据封装成帧及并串转换的功能,其中cntout输入信号用于与control模块之间进行同步,以确保2 M时钟对64 K时钟的数据进行锁存。devider8模块实现8分频功能,向parallel2serial模块提供2 M时钟。

图6 FPGA内部AD控制和并串转换原理框图

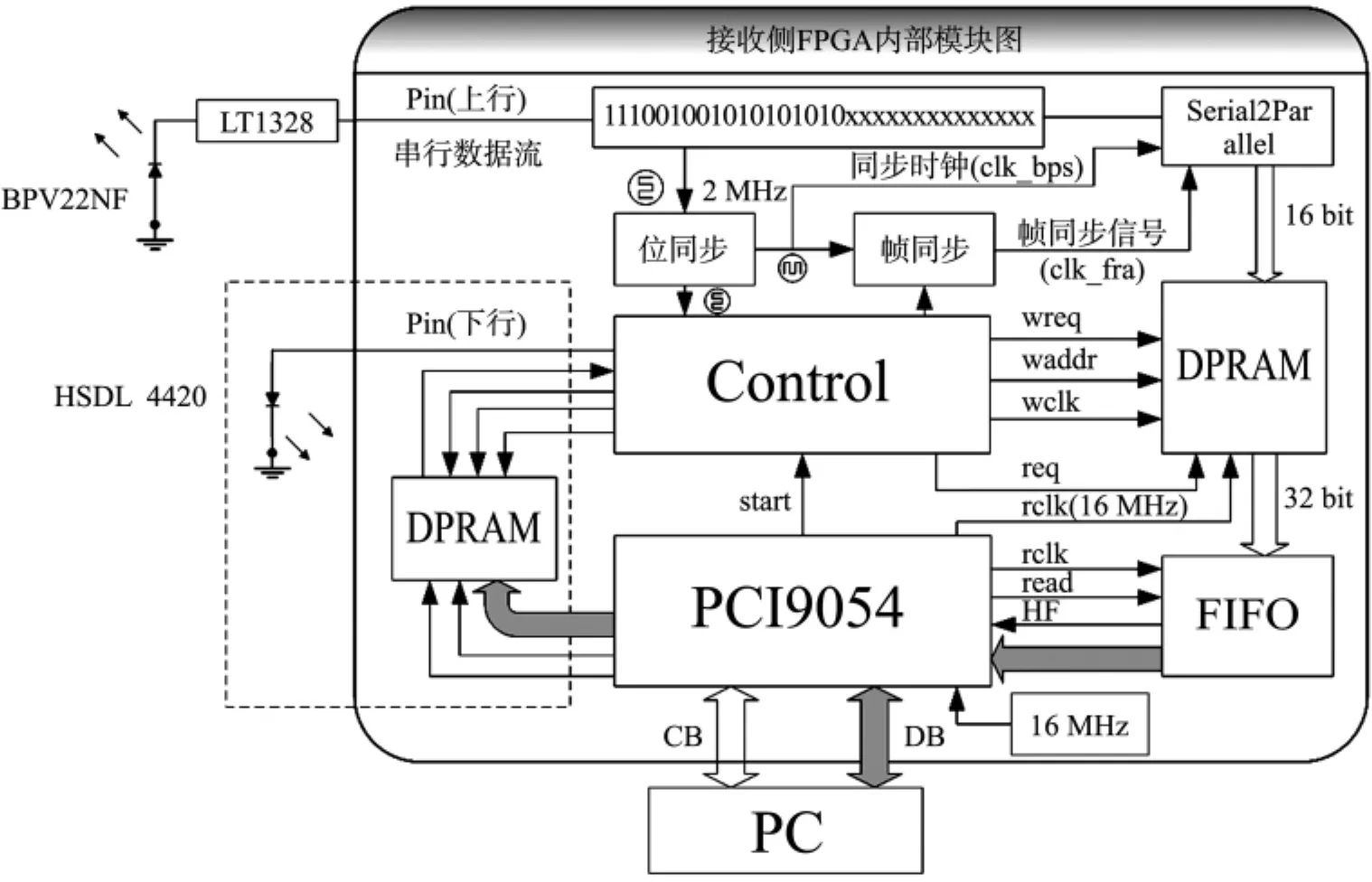

3 上行通道同步数字接收电路

固定侧FPGA内的同步数字接收模块用来取代低速红外传输情形下的UART接口,它必须保证对2 Mbit/s的串行数据流进行正确地位判别和接收,这也是整个系统实现的一个难点。本设计充分利用FPGA触发器、组合逻辑、嵌入式存储块(M4K)丰富,构建数字电路灵活,可反复配置的特点[6],将整个同步接收电路放在一块主时钟为16 MHz的FPGA内部实现,极大地节省了外设器件。各模块在FPGA内部的关系如图7所示。

上行通道的主体部分包括位同步模块[7]、帧同步模块[8-9]、serial2parallel 模块、control 模块、双端口RAM、缓冲FIFO以及PCI接口模块。下行通道由PCI、双端口RAM和control构成(图中用虚线框标出)。

3.1 位同步和帧同步模块

在数字通信系统中,常采用数字锁相环(DPLL)来实现位同步时钟的提取[10]。本方案中,在位同步模块内实现了一个基于超前滞后相位比较原理的2 M时钟数字锁相环。利用对系统时钟进行8分频,可以得到一个与输入码元速率同频的本地时钟。通过与输入码元进行相位比较,超前滞后比较器对本地时钟产生添加或扣除一个时钟脉冲的动作,不断调整本地时钟的相位,直到与码元相位误差保持在一定范围内,从而进入锁定状态。DPLL在完成对输入码流的同步锁定后,便可以对每一个码元的高低电平状态进行正确的判别;同时,DPLL恢复出的时钟为后续的帧同步模块、control模块、serial2parallel模块提供了基准时钟。

帧同步模块则实现了自动捕捉码流中的同步码字,使接收侧获得每一帧信号的起始位置以正确地对数据进行分路缓存。由于帧同步字“E4”每隔32个位时钟便出现一次,使得帧同步信号可以被周期地获取,使本系统不易失锁,具有稳定的同步性能。

3.2 并串转换及缓存模块

在位同步时钟和帧同步信号作用下,serial-parallel模块实现了在串行数据流中提取出每一帧后两字节有效载荷的功能,并在control模块控制下采用乒乓方式按64 kHz同步时钟的节拍将数据存入到深度为512、位宽为16 bit的双端口RAM中。当DPRAM有一半被写满时,数据在control控制下对双端口的另一半进行写入;与此同时,开启req信号,允许PCI9054模块以16 M频率读取刚被写满的DPRAM中的数据,并将其写入到深度为1 024,宽度为32 bit的FIFO中。待FIFO半满后,向PCI9054模块发半满中断信号HF,PCI9054模块向PCI总线请求一次长度为512的32 bit DMA传输。在应用程序中,再对获得的这1 024个采集数据进行通道区分和波形显示和分析。

图7中的LT1328是凌力尔特公司的一款支持FIR协议的红外解码芯片,SO8小外形封装,静态功耗极低,支持高达4 Mbit/s的通信速率,外加极少量的电容,就能将经过PPM编码或者NRZ编码的光脉冲信号还原成反向的TTL电平输出,可以与FPGA实现无缝连接,而不需要进行电平转换。实验观察及结果表明,经过LT1328转换得到的TTL电平信号噪声低,跳变沿陡峭,幅值稳定,完全满足DPLL对数字信号的要求。BPV22NF是推荐与LT1328搭配使用的红外接收头。

图7 固定板上FPGA内部各模块连接关系

由于在光信号发射侧,已将2 Mbit/s的数据信号按照NRZ形式编码并反向输出驱动红外发射管HSDL 4400。于是在接收侧,经过LT1328转换后得到的信号就是数据原码,可以直接使用。

4 实验结论

两块板上都选用ALTERA公司EP2C5Q208型FPGA作为控制器。在静态实验中,用函数发生器产生的正弦波来模拟待测信号,利用FPGA内部自带的逻辑分析仪SignalTap对需要考察的信号进行观察。

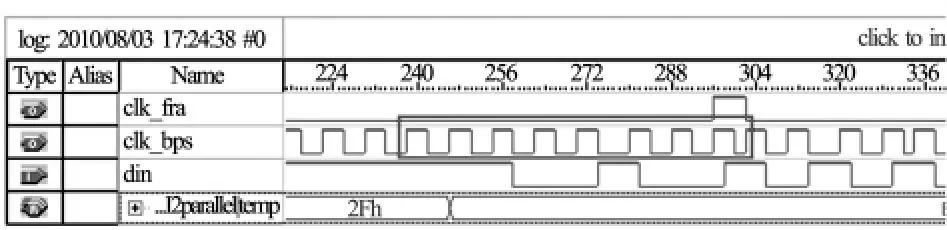

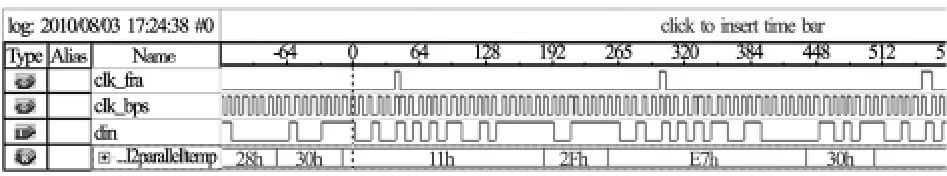

从图8中可以看到同步时钟clk_bit的上升沿始终与输入码元保持同步,且当串行码流中出现“11100100”时(对应图8中框出的8个时钟上升沿),会产生帧同步信号clk_fra;而图9则显示temp信号准确地锁存了每帧后两字节数据。随后,这些数据会依次通过DPRAM、FIFO和PCI接口模块传递给PC上的应用程序以用来显示和分析[11-12]。在实验中,只要DPLL进入锁定状态,就会建立起稳定的接收秩序,不会存在失锁现象,直到停止数据采集。

图8 检出帧同步字“E4”

图9 有效数据被正确锁存

当需要将控制数据传递给旋转板作驱动时,数据则沿着FPGA内部的下行通道进行传输,其过程与上行通道类似,只是在旋转侧FPGA中采用了更简单和适合小数据量传输的类似于串口的异步接收机制,在此就不赘述了。

5 结束语

本文基于 ALTERA公司CycloneⅡ系列芯片EP2C5Q208和红外收发器件,以及成熟的PCI总线,采用光信号同步传输的方式实现了一种轻便、多路、快速、稳定的同步双向信号传输系统,满足了对旋转件上多路信号同步测量和双向并行传输的需求,而且适当调整锁相环的工作参数,可以使锁定时钟达到FIR协议规定的4 Mbit/s带宽上限,因而在静态或动态条件下红外通信应用场合具有一定的参考价值。

[1]陈仁文.旋转件非接触信号传输中的通道特性研究[J].传感器技术,2003,22(10):9 -12.

[2]卞春江,张天宏,邓志伟,等.面向旋转构件的高速数据采集系统[J].传感器技术,2004,23(11):53 -55.

[3]MAX125 Datasheet[R].

[4]胡春华,石玉.数字锁相环路原理与应用[M].上海:上海科技出版社,1990.

[5]韩红霞,曹立华,刘帅师.基于FPGA的光纤通信系统中帧同步检测设计[J].电光与控制,2006,13(04):90 -92.

[6]任敏,庞杰,胡庆.CPLD与FPGA器件性能特点与应用[J].传感技术学报,2002,15(02):165 -168.

[7]范寒柏,陶杰,王欣.一种基于VHDL语言的全数字锁相环的实现[J].电子技术应用,2009,35(04):63 -65.

[8]张景悦,王明磊,王莹.基于FPGA的数字复接系统帧同步器设计与实现[J].国外电子元器件,2005,(5):4-6.

[9]王志,石江宏,周剑扬,等.同步数字复接的设计及其FPGA实现[J].电子技术应用,2005,31(04):77 -80.

[10]江黎,钟洪声.一种全数字时钟数据恢复电路的设计与实现[J].通信技术,2008,41(11):1 -3.

[11]温世杰,鲁冬杰,陈晓冬,等.基于FPGA的数字超声内窥镜接收系统设计[J].传感技术学报,2008,21(08):1329 -1332.

[12]方志强,段发阶,张玉贵,等.非接触式高速旋转叶片振动测量新技术的研究[J].传感技术学报,2007,20(04):937 -940.