线阵CMOS图像采集及编码传输的实现*

2011-05-06江志东高太长孙海洋翟东力

江志东,高太长*,孙海洋,翟东力

(1.解放军理工大学气象学院,南京211101;2.南京众华通电子有限公司,南京211101)

线阵图像传感器在图像扫描、非接触式尺寸检测、位移测定和条形码读出等光电探测和光电成像领域有着广泛的应用[1-2]。CCD图像传感器具有灵敏度高、频率响应高和自扫描速度快等优点,最早应用于上述领域,但CCD图像传感器也有一些无法克服的缺点,如功耗高、制造工艺复杂难于单片集成,且由于CCD是高电容器件读出速度慢。CMOS图像传感器以其功耗低、读出速度快、易于单片集成日益受到重视[3]。随着超大规模集成电路工艺技术的飞速发展,CMOS传感器性能不断完善,感光阵列不断增多,在工业自动化、民用视频、军事侦察、空问遥感成像等领域得到广泛应用[4]。随着线阵图像传感器感光阵列的不断增加,在高速图像采集处理系统中,对系统存储和数据实时处理也提出了更高的要求,需要解决图像传感器时序驱动、数据的缓冲、存储和传输等一系列问题。

在气象领域,基于CCD/CMOS传感器阵列的成像技术获取大气粒子或者其他现象的二维或三维图像,利用图像处理理论确定大气悬浮颗粒物[5]、云滴、雨滴[6]等粒子的浓度、尺度和速度分布信息,实现非接触粒子检测。在气象业务中,仪器通常需要长期连续观测且能够实时进行数据处理,因此需要重点考虑数据的存储、传输和实时处理等需求。

传统的线阵数据高速采集系统通常数字处理器(DSP或FPGA)、高速FIFO、比较器模块和传输接口芯片等组成,对于线阵CCD还需专门的驱动电路[7]。与通用DSP芯片相比,FPGA增加了设计的灵活性和适应性,缩短了产品上市时间[8]。本文介绍了基于FPGA和USB芯片CY7C68013实现的高速线阵CMOS图像数据采集系统,解决了传统采集方法中系统过于庞大和复杂的问题。针对高速采集数据的缓存、传输、实时处理及存储等需求,设计完成了线阵CMOS的驱动时序,利用FPGA内FIFO核实现了原始像素数据的缓存和抽帧输出,同时充分利用FPGA可编程特性,在FPGA内部实现了自适应阈值的比较模块,在保留所需图像信息的前提下,利用FPGA对比较后的二进制数据流数据进行压缩编码,降低了数据量,减少了对数据传输的要求,减轻了上位机实时数据存储和实时处理的压力。

1 系统总体设计与实现

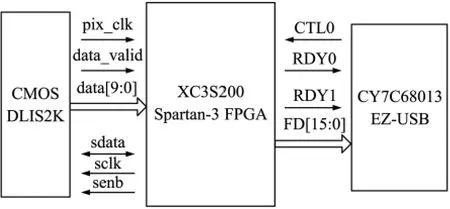

FPGA采用Xilinx公司Spartan-3系列XC3S200,主要完成传感器的时序驱动、数据的采集缓存、比较编码及传输逻辑控制等功能,该芯片容量为20万门,片上有分布式RAM 30 kbit和块RAM 216 kbit可用于构建FIFO和双口RAM;图像传感器采用Panavision Imaging公司的DLIS-2K CMOS图像传感器,该芯片包含4行2 096个像素单元的线阵,每一行中有效像元个数2 080个,16个像元单元供暗电流检测用,10位并行数字信号输出,最大数据率为120 MHz。为便于数据缓存和传输,结合系统需求实际数据输出取有效像素单元中的2 046个像素单元,每个像素单元数据用2个字节表示,结合帧数据头每帧采样数据量为4 kbyte(KB)。数据由USB芯片CY7C68013采用GPIF工作模式将数据上传至上位机。USB工作采用 GPIF方式,利用CY7C68013的通用可编程接口GPIF模式实现与传感器的无缝连接,可满足图像数据的实时传输[9]。

图1 图像采集系统硬件框图

系统采用FPGA+USB的架构,该设计包括以下三个部分:线阵CMOS图像传感器、FPGA芯片和USB芯片CY7C68013。FPGA芯片为主控模块,控制整个系统的工作时序和传输逻辑。根据需求系统可选择工作在两种模式下,即原始数据采集或编码数据采集模式。在FPGA控制下,首先从CMOS传感器的锁存读出图像数据,进行数据位转换,即将10 bit像素数据输出补为16 bit,并加入一定格式的数据帧头,然后将16 bit像素数据送至FIFO,再通过FPGA产生FIFO的读写控制逻辑和USB的接口传输逻辑,数据经USB芯片采用GPIF工作模式传至计算机,至此可完成传感器原始数据的传输。为减轻上位机存储和实时数据处理的压力,在保留所需图像信息的基础上,在FPGA中设计了数据比较编码处理模块,将原始像素数据和设定阈值进行比较,随后将比较结果即二进制数据流编码后的数据写入FPGA的FIFO中,最后编码数据仍由USB将数据上传至上位机。

2 FPGA内数据采集、编码功能的实现

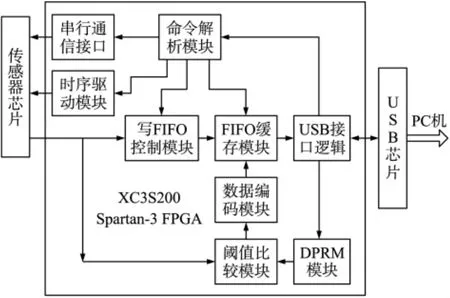

FPGA功能设计可分为接口模块、缓冲存储模块、编码处理模块三部分。接口模块负责前端传感器时序驱动、FIFO读写控制和为USB提供传输接口逻辑;缓冲存储器模块作用有利用FIFO为不同时钟域间数据传输提供缓冲,双口RAM中可写入经一定算法计算后的各点的像素阈值;编码处理模块根据设置的阈值,将实时采集的原始数据和每个像素单元的阈值进行比较,随后将比较后的结果编码输出。FPGA内功能模块设计如图2。

本系统中,如何保证数据的完整性和准确性实现高速采集时大量数据的实时传输和处理是要考虑的重点。

图2 FPGA内功能模块设计

CMOS传感器和USB芯片工作在不同时钟域,如何在不同时钟系统间实时准确传输数据是本系统的关键问题之一。常用的缓存有FIFO、SRAM及双口RAM等,双口RAM和SRAM存储量大但需配以复杂的地址发生器,而FIFO数据顺序进出,无需地址线,操作简单。异步FIFO(First in First Out)可以解决不同时钟域之间的数据传输问题,可以容纳异步信号的频率或者相位的差异[10],FIFO芯片广泛常应用于图像数据采集的缓冲[11]。因此如何设计一个高可靠性、高速异步FIFO存储器及控制逻辑实现数据的缓存、传输时难点之一。

本系统中传感器数据采样帧频需在10 kHz以上,而当传感器的帧频为10 kHz时,实时原始像素数据量即可达到40 MB/s(Mbyte/s)。在普通计算机中,硬盘的持续传输速率最高可达50MB/s,但在Windows操作系统下,应用程序很难达到这一速率。如何保留相关必要图像信息,减少数据传输量,实现数据的实时处理是本系统的难点之二。

下面着重对系统的数据缓冲模块和编码处理模块的实现及工作原理分别介绍。

2.1 数据缓冲模块

利用FPGA片内异步FIFO作高速缓存,操作简单,所用的FIFO IP核经过充分测试和优化,运行稳定、可靠。实际应用时只需根据FIFO产生的逻辑标志设计读写逻辑即可,而不需考虑FIFO设计中逻辑标志的产生和异步电路的亚稳态等问题[12]。

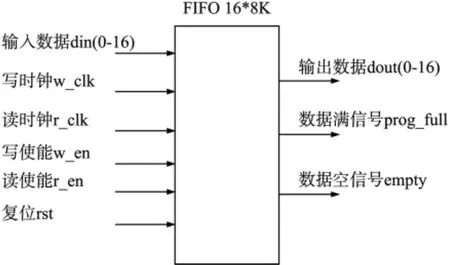

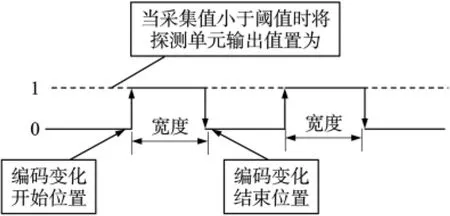

在ISE开发工具中创建FIFO_Core,选择异步时钟和使用内部块RAM,设置其输入输出数据位宽为16,FIFO深度为8 096,设置可编程满信号计数为4 095,当FIFO写计数达到4 095时(注意此对应第4 096个数据),即达到一帧数据时触发可编程满prog_full信号,FIFO的功能示意图如图3。在FIFO的例化调用时,写时钟为传感器数据输出同步时钟,读时钟为USB的GPIF模式的IFCLK。

图3 FIFO结构图

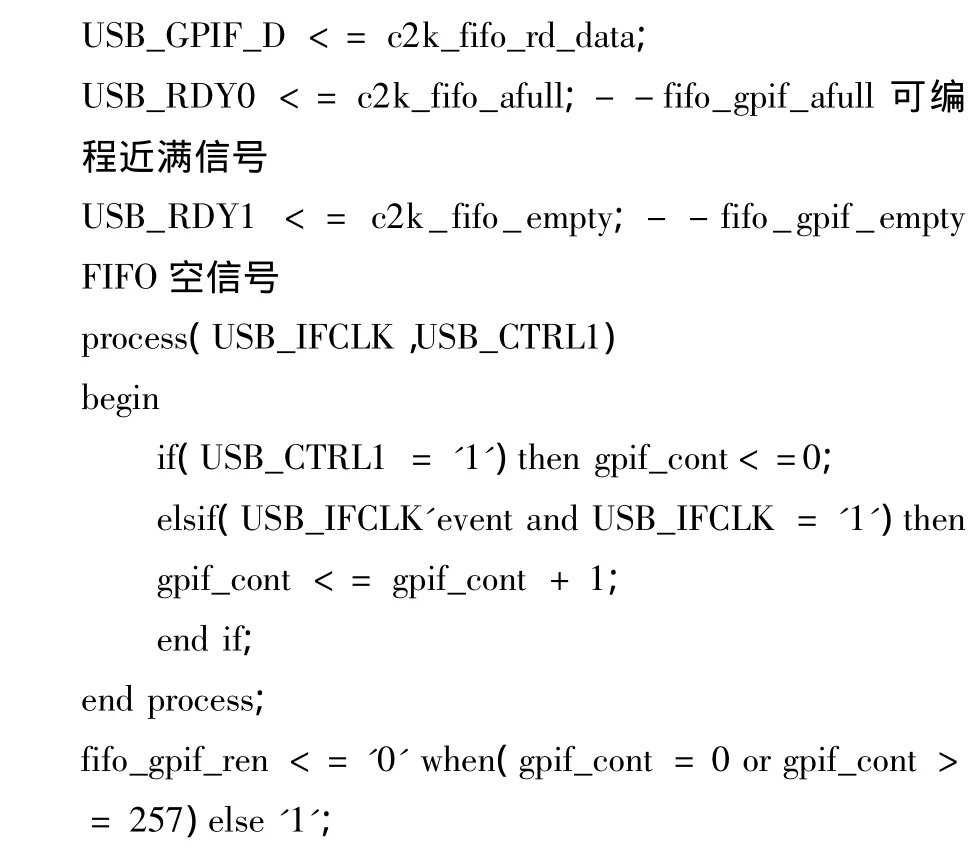

数据缓冲模块的设计实际上是FIFO的读写逻辑的设计,即写使能和读使能的控制。FIFO采取单行复位的方式,检测到有效数据标志上升沿后,启动像素计数,当像素计数值为29时,FIFO复位,像素计数值在30到2 077之间时,FIFO写使能有效。其中像素计数值为30和31时,写入FIFO数据帧头0×9 999,其后对应CMOS输出有效的2 046个像素数据。原始像素数据实时采集时,当FIFO写计数达到4 095时候,触发可编程满prog_full信号,由prog_full做为控制FIFO异步读数据的状态信号之一,当prog_full有效时,FIFO写使能禁止。FIFO读使能由prog_full触发,由USB固件程序根据其端点FIFO状态及FPGA内部FIFO的状态信号控制。USB工作与GPIF模式,设置为Auto-In(自动打包)模式,每次传输数据量为512 B(byte),对应256个像素单元数据,满足条件时无需外部控制器的干预可直接自动将FIFO中数据传输到上位机,完成CMOS数据的实时传输。下面给出了FPGA中和USB连接的部分逻辑代码:

2.2 数据编码压缩模块

为了减少数据传输量,减轻上位机数据存储和处理压力,结合系统自身功用,设计了数据编码压缩单元对原始像素数据进行处理。数据编码压缩单元包括阈值比较模块、双口RAM,数据编码模块三个部分。双口RAM直接在ISE调用Core Generator生成,其参数为2 k·16 bit,其中A口设置为写状态,通过上位机可控制写入经一定算法计算的每个像素点各自的阈值,B口为读状态,比较模块读入阈值和对应的像素数据比较。

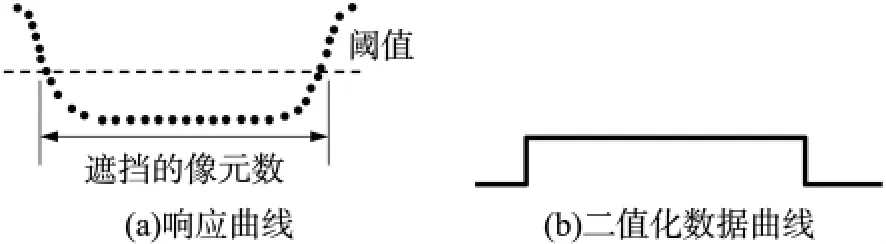

数据编码压缩前首先需将传感器像素的响应曲线二值化,根据设置的阈值(此外设置为固定值,实际测量时可对每个像素点设置各自阈值),当相应像素光强响应值低于预先设置的阈值强度时,则认为该像素被完全遮挡,置为1,如图4。数据编码示意图如图5,当检测到帧数据有效标志datavalid上升沿信号时,启动读像素计数,读像素计数范围为[30,2 077]时,触发比较使能,在读像素计数的触发下,双口RAM地址递增,像素数据值和其对应阈值进行比较(实际应用时可根据相关算法写入对应点阈值,示意图中采用固定阈值),当所采集的像素数据值低于设置的阈值时则比较结果为1,否则为0。数据编码模块是根据比较结果数据流,即二进制序列,在检测到比较结果的上升沿时记录当前像素数据的位置同时触发编码计数,在比较结果下降沿记录当前编码计数,从而确定对应的编码宽度。将比较结果数据流编码输出,输出起始位置和编码的宽度,这样即保留了原始数据的信息,又可以减少数据量,确保数据的实时传输和处理。

图4 原始数据二值化示意图

图5 编码示意图

3 仿真及试验结果

为检验模块的功能,利用Modelsim编写测试向量对相关设计进行了仿真,同时将程序编译后下载至数据采集板观测结果。

3.1 FIFO逻辑的仿真及试验

向FIFO写数据必须满足两个条件:①数据总线有数据且数据有效,②FIFO写使能有效。由于传感器行有效标志data_valid有效时一直有数据输出,而实际上我们只使用其中的2 046个数据(前两个数据为数据帧头),因此不能将data_valid直接做为FIFO的写使能有效信号,FIFO写使能标志由data_valid和FIFO的可编码满标志prog_ful共同确定。在检测到行有效信号后触发像素计数,当计数值为30和31时为数据帧头数据,32~2 077为实际像素数据。时序仿真后波形如图6(a)。将代码下载至FPGA中运行发现上位机并不能实时完全处理及存储每一帧数据,即存在丢帧情况。利用模拟数据测试传输模块发现,正常情况下GPIF的传输数据率为20 Mbyte/s左右,此外上位机的实时处理也影响数据的传输。在实际应用中,原始像素数据的采集主要用于时域分析,即统计一定时间内各个像素单元响应光强的平均水平,为数据比较阈值的设置提供参考。因此没有必要将每一帧原始像素数据记录保存,写FIFO控制采用抽帧的控制方式,即采用多级门控信号实现每几帧数据输出一帧,每一级门控信号由data_valid触发,由多级门控信号同时触发写FIFO使能,如时序仿真波形图6(b),采用每四帧输出一帧,在此条件下可完整将输出原始数据保存用于时域分析。经抽帧输出控制,对应传感器的数据采集帧频为10 kHz时,原始数据的输出量由40 Mbyte降至10 Mbyte,利用CYPRESS公司提供的USB驱动和固件程序框架无需优化即能够实现数据的正常传输,上位机能够将实时原始像素数据保存用于时域分析。

图6 异步写FIFO时序仿真图

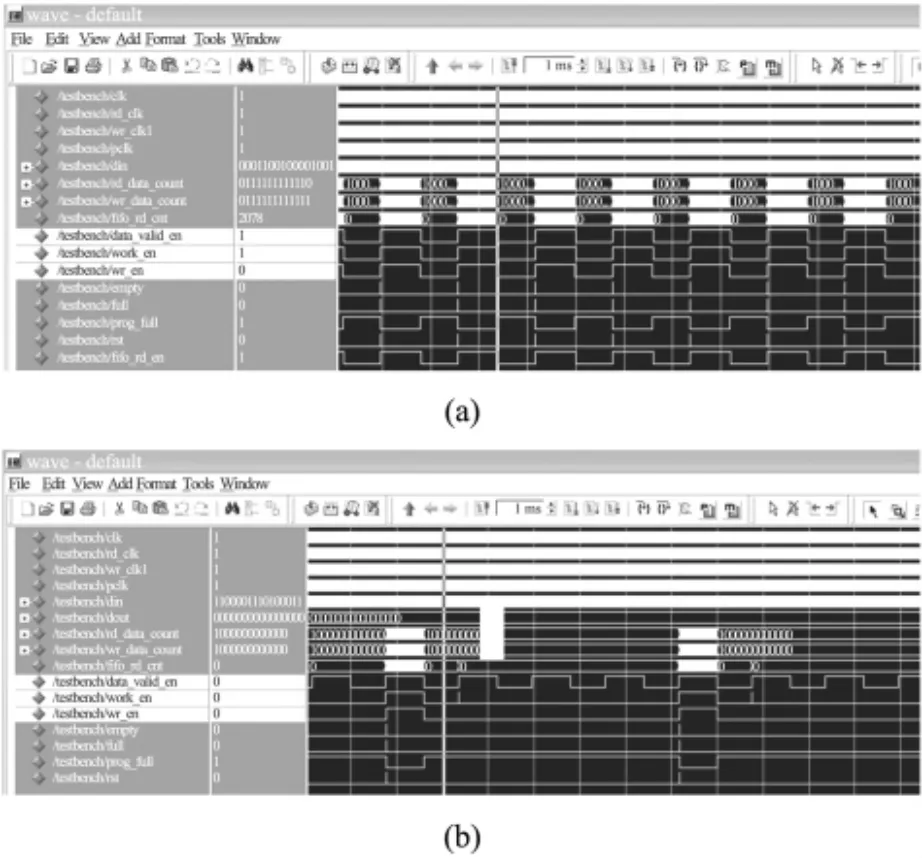

3.2 编码功能的仿真及试验

在测试向量中假设二值化起始位置为20和68,结束位置分别为52和244,则编码结果应该为[20 32][68 176],仿真时序图如图 7。经编码压缩,对应传感器的帧频10 kHz时,系统的数据采集量由每秒40 Mbyte降至78 kbyte(每帧为数据头加一组编码数据时),传输系统能够完全不丢帧降数据传至上位机,上位机能够实时存储和解码计算。

图7 编码功能时序仿真图

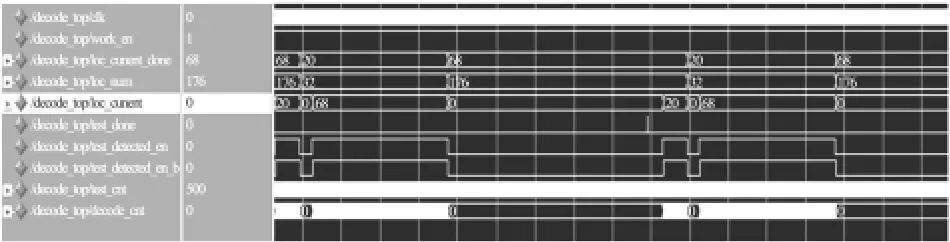

4 初步试验结果及小结

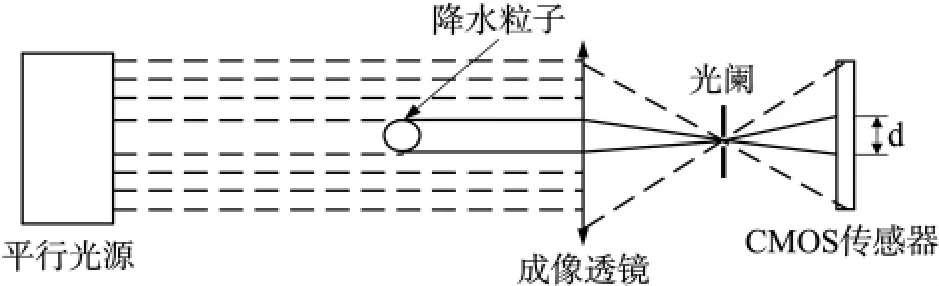

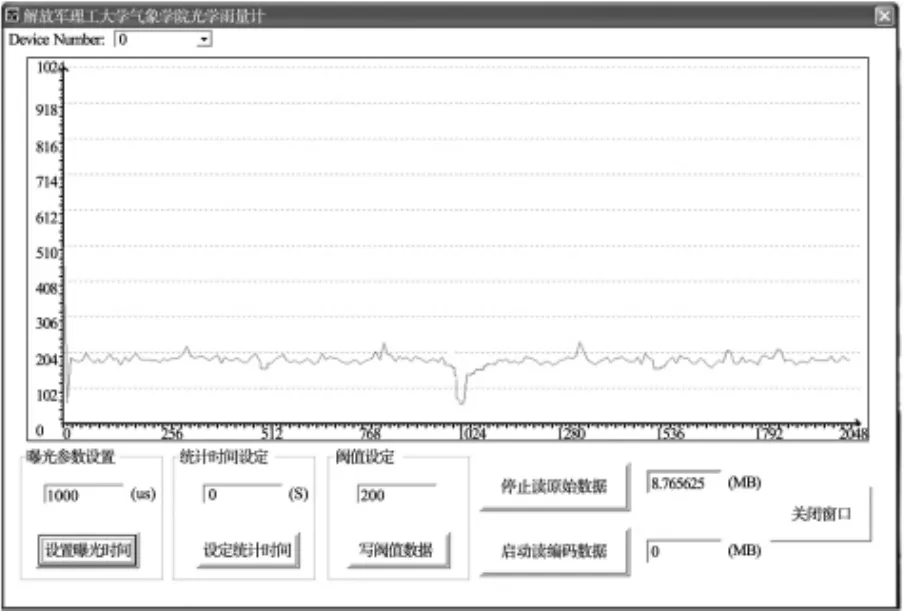

结合光学照明系统和成像系统,对数据采集板进行了初步调试。图8为系统成像示意图,当降水粒子遮挡光路时,在线阵传感器上产生投影,引起光强响应的变化。光源采用激光平行光源,中心波长650 nm,功率30 mW。传感器采样速率为20 000帧/s,以0.2 mm的铜丝遮挡光路引起的光强响应变化如图9。

图8 系统工作原理示意图

图9 实际光强响应曲线

系统采用可编程逻辑器件FPGA和USB2.0接口技术实现了线阵CMOS的时序驱动、高速采集、阈值比较和传输,解决了以往采集系统中存在软硬件过于复杂的问题,克服了大量数据传输和处理时对上位机处理带来的压力,充分利用了FPGA芯片的片内资源,结合自适应阈值统计方案,实现高速数据采集和比较编码压缩,达到了小型化、智能化和高性价比的有机结合。

初步试验结果表明,系统满足图像数据实时采集和处理的要求,同时减轻了上位机数据存储和处理的负担。为实现不同尺度、不同下落末速度降水粒子的检测,传感器采样速度应在15 000帧/s以上。DLIS-2K的最大数据输出率为120 MHz,系统采样典型的配置工作在60 MHz时,采样速率约7 500帧/s,若设当修改传感器参数配置、采用更高工作时钟,可将CMOS数据采样率提高到20 000帧/s以上。随着FPGA的发展,利用带有USB IP核的FPGA芯片可进一步实现系统的小型化。本系统可用于大气粒子的非接触测量,适当修改可应用到一维尺寸测量,边缘检测,位移测量等方面。系统初步实现了线阵图像原始数据和编码数据的采集,如何实现系统的业务化观测,还需进一步确保系统野外运行时的稳定性及关注系统自检和定标等功能的实现,此外对数据的后续处理及二次产品开发将另文探讨。

[1]周根荣,姜平.基于线阵CCD的织物图像采集系统[J].仪表技术与传感器,2007,(8):51 -52.

[2]王玉田,杨妮,林晓琳.基于CCD技术的浮法玻璃厚度测量系统的研究[J].仪表技术与传感器,2007(6):72-74.

[3]方杰.CMOS图像传感器[D].[硕士学位论文].上海:复旦大学,2004.

[4]曾桂英,潘金艳.基于FPGA的CMOS图像传感器采集系统设计[J].科学技术与工程,2010,10(03):692 -695.

[5]王丹青.基于分形理论的大气悬浮颗粒物图像识别[D].[硕士学位论文].武汉:武汉理工大学,2006.

[6]Baumgardner D,Greg Kok1,Dawson W,et al.A New Groundbased Precipitation Spectrometer:The Meteorological Particle Sensor(MPS)[C]//ams confex com,2002.

[7]虞益挺,饶伏波,乔大勇,等.一种新型CCD驱动电路设计方法[J].传感技术学报,2005,18(2):388 -390.

[8]叶敏,周文晖,顾伟康.基于FPGA的实时图像滤波及边缘检测方法[J].传感技术学报,2007,20(3):623 -627.

[9]苏建坡,马海涛,唐玉国.基于USB2.0及GPIF的CMOS图像传感器视频实时采集系统[J].仪表技术与传感器,2006(9):35-37.

[10]张毅,周成英.高速同步FIFO存储器在数字信号源中的应用[J].电子技术,2003,30(11):48 -50.

[11]汪曣,白玉洁,张艳超,等.基于CCD的胶体金试纸条光电检测仪器设计及实验研究[J].传感技术学报,2008,21(8):1370-1373.

[12]杨军,孔兵,宋克俭,等.基于FPGA的高速异步FIFO存储器设计[J].云南大学学报,2007,29(6),560 -565.