数字脉冲应答机的时延补偿方法

2010-09-27

(中国西南电子技术研究所,成都 610036)

1 引 言

单脉冲相参应答机的基本功能是相参转发单脉冲地面雷达上行信号,与地面雷达协同工作,完成飞行器轨道测量。地面雷达通过测量飞行器应答机转发信号的时延完成飞行器距离的测量[1]。因此,要求应答机转发时延稳定。

在传统模拟体制脉冲应答机设计中,脉冲延迟选用声表面波延迟线,这种延迟线插损大,延迟时间随温度变化较大,带来调试难、生产性差、时延不稳定等缺点,严重影响到地面雷达的测距精度。为了克服模拟体制脉冲应答机的缺点,脉冲相参应答机采用了数字化设计,运用数字存储转发和数字时延补偿技术,可大大提高脉冲应答机转发时延的稳定性。该数字化脉冲相参应答机具有延迟时间易修改、控制精度高、可靠性高、生产性好、小型化和使用灵活等优点。

本文主要介绍了单脉冲应答机数字终端设计,对转发精度进行了分析,提出了数字化时延补偿技术,并针对实际应用工程,给出了试验测试结果。

2 数字化终端设计

单脉冲相参应答机与地面雷达站合作实现高精度测距,关键是控制应答机的转发延时精确。采用基于FPGA的数字存储转发技术,可容易实现高精度的时延补偿,能大大提高应答机的转发精度。

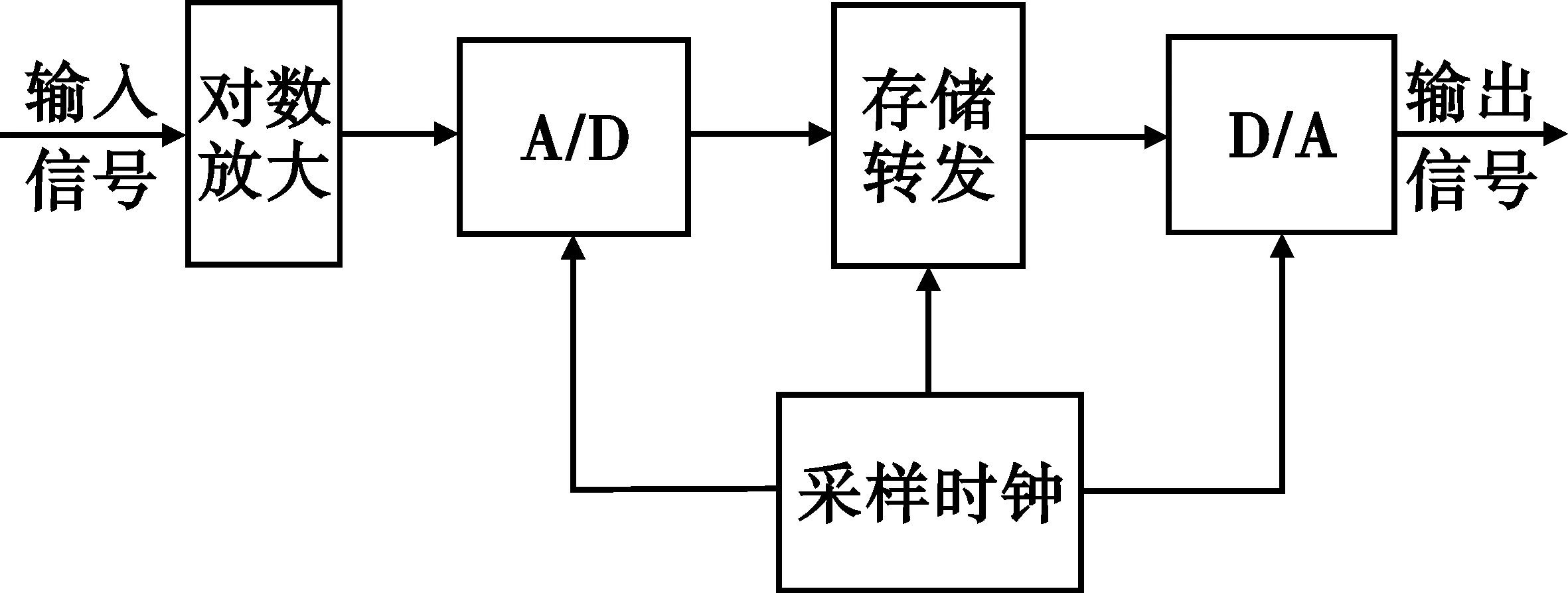

数字化终端的实现原理框图如图1所示。其信号流程为:接收高放模块送来的中频信号,经对数放大,压缩接收信号的动态范围和中频检波,再经过A/D采样后,直接送到FPGA进行数字化设计,采用数字存储方式精确控制转发延时时间,经D/A变换器输出中频转发信号。

图1 数字存储转发原理框图Fig.1 The functional diagram of digital store and forward technique

如何实现存储转发功能,是数字化终端设计的关键。终端的存储转发器采用FPGA实现,利用数据同步时钟作为写信号,将送入FPGA的数字数据写入RAM或FIFO芯片中,再用本级采样时钟将数据读出,从而实现数字接口同步以及输入、输出延时可变的灵活设计。通常,双口RAM的端口控制比FIFO更灵活,由地址线就可完成读取或存储数据要求,故本数字终端选用双口RAM实现数据同步和延时转发存储功能。针对实际工程应用中双口RAM的参数设计,应根据A/D和D/A的位数、中频调制脉冲信号的脉宽τ以及A/D采样时钟fs的关系综合计算出需要的存储器位宽和深度。

该数字终端的存储转发器各参数可通过程序灵活设置,实现了应答机时延可控,以便满足不同任务需求;同时,转发延时时间可控制在1个时钟周期内,大大提高了应答机脉冲转发的延时精度。

3 延时转发精度分析

根据脉冲信号测距原理,地面雷达通过测量脉冲信号传播时间计算目标距离[2]:

(1)

式中,c为电波传播速度,τ是传播时间。

实际得到的信号传播时间包括信号空间传播时间、应答机转发信号延时时间和信号在地面雷达系统信道中的传播时间,而应答机转发延时时间稳定性是确保地面雷达测距精度的关键。

应答机转发延时时间误差主要包括热噪声引入的转发脉冲前沿抖动、系统时钟漂移以及信号电平变化产生的转发脉冲前沿漂移等。

(1)噪声带来的延时误差Δτ1

脉冲应答机接收到脉冲信号后,接收信道和接收机中存在热噪声,含有噪声的信号进入视频放大器和门限电路时,脉冲信号前沿就会叠加噪声电压,使脉冲触发不稳定,从而造成了延时误差,这种延时具有随机分布的特点,如图2所示。

图2 噪声引入的延时误差Fig.2 Time delay error vs received noise

(2)时钟漂移的时延误差Δτ2

系统时钟漂移会引起A/D采样数据抖动,从而导致各种控制脉冲的计数误差,时钟漂移引起的时延最大误差不超过1个时钟周期,若系统采样时钟为fs,则时延误差为Δτs=1/fs。

(3)电平变化引起的时延误差Δτ3

为了适应飞行器测距需要,脉冲应答机接收信号需满足一定的动态范围要求,即应答机接收信号的电平是距离的函数,应答机离地面雷达站越远,其接收信号电平越低,反之亦然。接收信号电平的变化会导致检波器输出信号包络电平随之发生变化,而脉冲信号检波包络判决门限设置固定,弱信号和强信号对应的触发判决电平时间会不同,造成时间延时误差。当信号增强时,检波包络判决触发点时间向前移动,具体变化规律如图3所示。

图3 接收电平变化带来的延时Fig.3 Time delay vs the received signal level

导致这种现象的原因是中频脉冲调制信号经过滤波器后,因滤波器的带宽限制,滤除了脉冲信号中的高频分量部分,使脉冲信号的沿发生畸变。畸变后的脉冲经过固定判决电平判读后,脉冲前沿产生漂移。

脉冲应答机转发时延误差主要有两种类型,一种是恒定的和慢漂移误差,另一种是具有随机特性和起伏特性误差。后者是无法校正的,会引起随机的测距误差,噪声带来的延时误差Δτ1就属于此种情况。而前者针对恒定的或有规律的慢漂移误差,可以在测距系统中利用系统校正措施进行补偿或消除,时钟漂移误差Δτ2和信号电平变化带来的延时误差Δτ3属于此种情况。针对Δτ2,可以利用提高系统时钟频率和频率稳定度指标措施,减少该项误差;针对Δτ3,主要采用数字化时延补偿技术进行补偿。

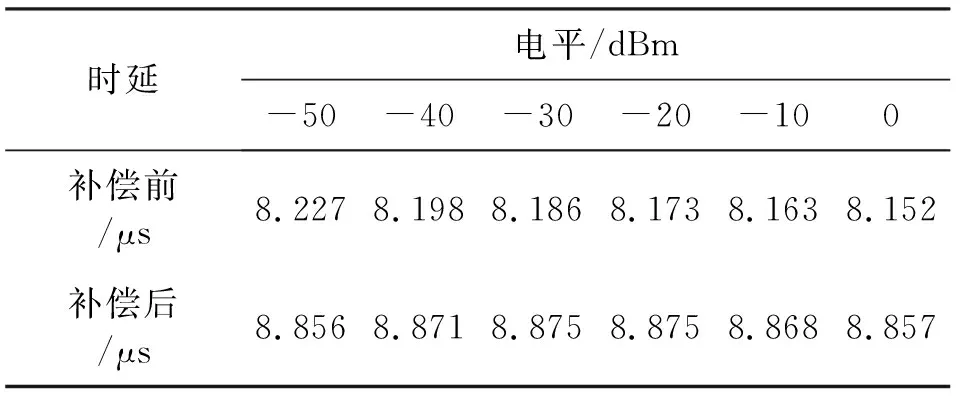

表1是某项工程中针对电平变化引起应答机时延变化情况的测试数据结果。测试条件为:未采用时延补偿技术,动态范围为50 dB,采用时间间隔仪测试应答机的转发时延。

表1 电平变化引起的时延变化表Table 1 Value of time delay vs the received signal level

从试验测试数据可知,在整个接收信号的动态范围内,电平变化引起的时延误差Δτ3=75 ns,这个指标远远不能满足系统使用要求,需改善设计。

4 时延补偿方法

针对数字化脉冲应答机终端信号电平变化引起的时延较大,需采用相应的技术补偿措施,提高脉冲应答机的时延转发精度。针对该脉冲应答机,主要采用的技术补偿措施有如下几种。

(1)增加滤波器带宽

检波前滤波器的带宽会影响接收脉冲前沿的抖动。根据工程研制经验可知,若滤波器带宽增加一倍,其脉冲前沿的延时变化可减小一半[3];但滤波器带宽变宽,会增加滤波器带内噪声,恶化后端信号信噪比,因此,在选择滤波器带宽方面需要进行折衷考虑。

(2)数字化时延补偿方法

针对脉冲应答机的时延变化,还可采用数字化补偿措施。该补偿方法主要是利用对数放大器检波脉冲的能量,根据实测能量结果实时完成时延误差的补偿。在实现上采用低速A/D采样+查找表的设计方案,即根据检波脉冲能量,查找相应的时延补偿量进行补偿。

第一种方法在设备研制前就需完成,根据设计的信号信噪比和时延变化误差量,选择合理的滤波器带宽。由于器件性能的不一致性会导致不同设备接收信号的信噪比、时延变化出现差异,因此,采用该方法缺乏灵活性。第二种方法能根据不同系统的精度要求、设备个体差异有针对性地设计延时查找表,灵活调整应答机的高、中、低转发精度。因此,针对实际研制的数字化脉冲应答机,优先选择数字化时延补偿方法。

数字化时延补偿方法的具体实现过程为:将检波脉冲进行A/D采样,在FPGA内部设计一个查找表,根据A/D采样的数字幅度,查询延时的变化量,查找表深度根据转发精度的要求设定[4]。根据工程经验,选择A/D采样速率大于10倍脉宽即可满足系统精度要求,有效位数根据系统的动态范围进行选择,其实现框图如图4所示。

图4 时延补偿的实现框图Fig.4 The implementation block diagram of time delay compensation

通过以上分析知,信号处理补偿技术设计更灵活,控制精度更高,因此在具体实现上选择数字化时延补偿方式。

5 测试结果

表2是采用数字化时延补偿方法前后测试结果对照表。从表中可知,脉冲应答机接收信号的动态范围为50 dB,在采用补偿技术前,脉冲应答机接收整个动态范围内的脉冲信号最大延时误差达到75 ns;采用数字化补偿技术后,可将脉冲延时误差减小到19 ns,大大提高了脉冲应答机的延时转发精度。

表2 数字化时延补偿方法前后的时延误差比对表Table 2 Comparison of time delay errors before and after digital time delay compensation

6 结束语

脉冲应答机在配合地面雷达完成目标测距任务过程中,要求应答机具有高的信号延时转发精度。数字化脉冲相参应答机采用基于FPGA的数字存储转发技术,并结合查找表的高精度时延补偿方法,可大大提高应答机的测距精度,对实际工程应用具有借鉴价值。

参考文献:

[1] 赵树强,许爱华,胡绍林. 脉冲雷达高仰角测量数据分析及处理对策[J].飞行器测控学报,2003,22(4):67-70.

ZHAO Shu-qiang,XU Ai-hua,HU Shao-lin. Measurement Data Analysis and Processing Counterplan of the High Elevation Angle of Pulse-Radar[J].Journal of spacecraft TT&C Technology, 2003,22(4):67-70.(in Chinese)

[2] 丁鹭飞,耿富录.雷达原理[M]. 西安:西安电子科技大学出版社,2002.

DING Lu-fei,GENG Fu-lu.Radar Princple[M].Xi′an:Xidian University Press,2002. (in Chinese)

[3] 廖承恩.微波技术基础[M]. 西安:西安电子科技大学,1995.

LIAO Cheng-en.Microwave Technology [M]. Xi′an:Xidian University Press,1995. (in Chinese)

[4] 张海燕,李欣,田书峰. 基于BP神经网络的仿真线设计及其FPGA实现[J].电子与信息学报,2007,29(5):1267-1270.

ZHANG Hai-yan,LI Xin,TIAN Shu-feng. Simulation Line Design and Its FPGA Realization Based on BP Neural Network[J]. Journal of Electronics & Information Technology,2007,29(5):1267-1270.(in Chinese)