基于DDS的快速频率源的研制

2010-06-28高峰

高 峰

(船舶重工集团公司723所,扬州225001)

0 引 言

直接数字频率合成(DDS)技术在上世纪70年代提出后,随着器件水平的提高发展十分迅速。与传统的直接频率合成(DS)、锁相环间接频率合成(PLL)相比,DDS具有频率切换时间极短、频率分辨率高、相位连续和相位噪声低等优势。因此,基于DDS技术的频率合成器在高速跳频系统中得到广泛的应用,在充分发挥DDS高速频率切换的同时如何进一步提高频率合成器输出频谱纯度,是DDS频率合成器需要解决的关键问题之一。

1 基于DDS的频率源方案

本频率源技术的设计要求为输出频率范围5~7GHz信号,跳频步进≤1kHz,频率切换时间≤0.1 μ s,相位噪声 ≤-100 dBc/Hz@1kHz,带内杂散≤-60 dBc。该频率源方案原理框图如图1所示。

图1 频率源原理框图

2 频率源设计

2.1 技术参数分析

(1)跳频步进

该频率源要求跳频步进≤1 kHz,所选用的DDS芯片BTDS856具有32位频率控制字,频率精度可达Fclk×2-32Hz,因此输出信号的跳频步进取决于DDS的时钟频率。由于DDS芯片最高时钟频率可达3.2 GHz,本方案中选用2.8 GHz的锁相介质振荡器(PDRO)作为DDS的时钟频率,则DDS的频率分辨率为:

而本方案中DDS输出信号二倍频后的频率分辨率约为1.3 Hz,所以最后输出信号的频率步进可满足≤1 kHz的要求。

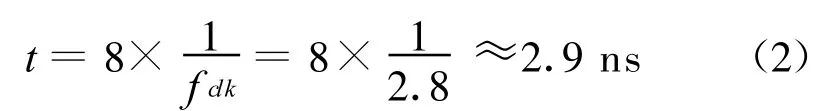

(2)频率切换时间

该频率源的频率切换时间主要取决于DDS及PIN开关的切换时间。由于该DDS频率切换时间为8个时钟周期,因此DDS的频率切换时间为:

再加上FPGA及接口芯片等数字电路传送频率控制字的延时,DDS输出信号的频率切换时间≤10 ns。

而PIN开关的切换时间主要取决开关控制码是否需要解码及PIN二极管的导通关断时间,在本频率源设计中由于FPGA输出端口充足,因此直接提供PIN开关控制码,无解码过程的延时。而选用开关采用的PIN二极管导通关断时间≤50 ns。因此,该频率源能够满足频率切换时间≤0.1 μ s的要求。

(3)相位噪声

该频率源的相位噪声要求≤-100dBc/Hz@1 kHz。相位噪声计算公式的推导在许多频率源的书中都有详细的阐述和推导(参考文献[2]有详细介绍),本文就不进行展开叙述了。频率源输出信号的相位噪声主要取决于频率变换时产生的相位噪声的恶化,其恶化规律可认为满足公式(3),式中的θnOUT(t)为频率变换后的信号相位噪声,θnIN(t)为频率变换前信号的相位噪声:

本设计中选用了相位噪声为-150dBc/Hz@1kHz的恒温晶振作为频率源的基准源,选用2.8 GHz的PDRO作为DDS的时钟信号,该PDRO输出信号的相位噪声依据公式(3)计算后为-121 dBc/Hz@1 kHz,一般来说,PDRO输出信号的相位噪声可能会比理论计算值差3 dB左右,因此DDS时钟信号的相位噪声实际值大约为-118 dBc/Hz@1kHz。DDS的相位噪声依据公式(3)计算后大约为-132 dBc/Hz@1 kHz。DDS输出信号经过二倍频后的相位噪声依据公式(3)计算后大约为-126 dBc/Hz@1kHz。而4.4~6 GHz本振信号的相位噪声最差为6 GHz,其相位噪声依据公式(3)计算且恶化3 dB后为-111 dBc/Hz@1kHz。DDS的二倍频信号与4.4~6 GHz本振信号混频后的射频输出信号的相位噪声可认为满足公式(4),式中的θnOUT(t)为混频后的射频信号相位噪声,θnIF(t)为参加混频的中频信号(即DDS二倍频信号)的相位噪声,约为-118dBc/Hz@1kHz,θnLO(t)为参加混频的本振信号(即4.4~6.0 GHz本振信号)的相位噪声,约为 -111 dBc/Hz@1 kHz。

依据公式(4)计算可知最终输出信号的相位噪声大约为-110 dBc/Hz@1kHz,满足θnOUT(t)≤-100 dBc/Hz@1 kHz的要求。

(4)杂散

该频率源的杂散要求≤-60 dBc。输出信号的杂散主要由以下几个因素产生:

(a)DDS二倍频信号的杂散;

(b)4.4~6 GHz的本振信号的杂散;

(c)DDS二倍频信号与4.4~6 GHz的本振信号混频后产生的交调信号。

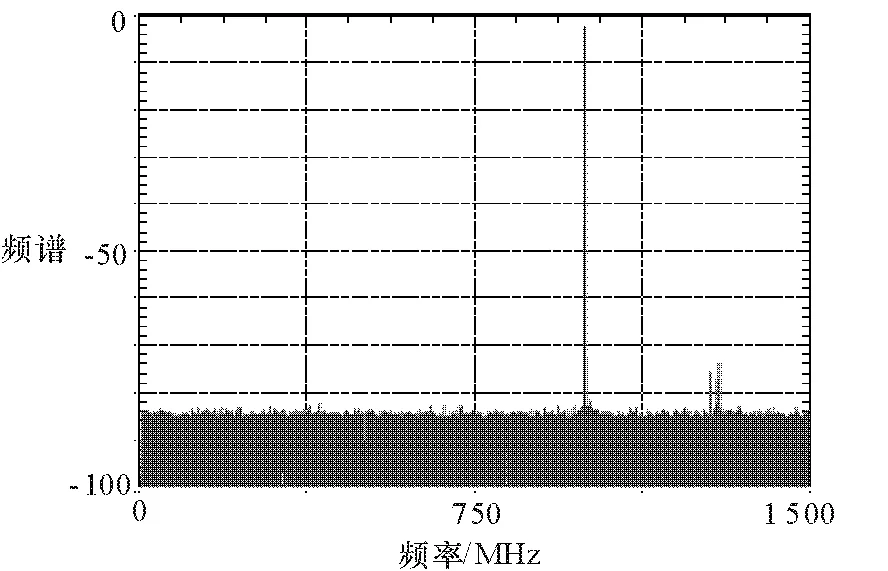

图2为当时钟频率为3GHz时,DDS输出1 GHz信号的频谱。

图2 时钟频率=3 GHz,DDS输出1 GHz信号的频谱

该DDS在3 GHz的时钟信号下输出1 GHz信号杂散≤-70 dBc,则当时钟信号为2.8 GHz时,输出300~500 MHz的信号杂散亦≤-70 dBc,但DDS输出信号中伴随着2.8 GHz时钟信号,采用300~500 MHz的LC滤波器可将该时钟信号滤除,DDS信号二倍频后,考虑到300 MHz信号的三次谐波落在6 00~10 00MHz带内 ,采用6 00~800 MHz、800~1 000 MHz的2路开关滤波器组对二倍频信号进行滤波,根据杂散恶化原理,二倍频后信号杂散将恶化6dB,则DDS二倍频信号杂散≤-64 dBc。

4.4 ~6 GHz的本振信号由100 MHz的晶振基准信号倍频后得到,晶振输出100 MHz信号杂散≤-80dBc,该杂散为近端杂散,采用中心频率为100 MHz的晶体滤波器可以将近端杂散抑制至-110 dBc以下,4.4~6 GHz信号的最大倍频比为60倍,根据杂散恶化原理,4.4~6 GHz信号的杂散最多恶化35 dB,则也能保证杂散≤-70 dBc。

DDS二倍频信号与4.4~6 GHz的本振信号混频后产生的交调信号都能通过后面的开关滤波器组滤掉,最后输出的5~7 GHz信号杂散能够达到小于-60 dBc的指标。

2.2 DDS电路设计

DDS原理在很多频率源的文献中都能找到相关内容的阐述(参考文献[1]有详细介绍),本文就不作介绍了。近年来出现了许多高性能的DDS芯片,本设计使用的Euvis公司的DDS芯片BTDS856凭借其优异性能在众多场合得到了广泛应用。该DDS芯片具有32位频率分辨率、13位ROM 相位分辨率、11位DAC幅度分辨率,能够产生高达1.6 GHz模拟信号输出(当时钟频率为3.2 GHz时)。初始相位可预置为零度。DDS芯片BTDS856有32位频率控制字,频率精度可达Fclk×2-32Hz,设计时选用Altera公司的FPGA芯片EP2C8208I8来实现频率控制。采用2.8 GHz高稳定锁相源作为DDS输入时钟频率。为了满足杂散指标,DDS输出信号选用3 00~50 0 MHz,频率精度为0.5kHz,在这一频段里,DDS输出信号的杂散≤-70 dBc。DDS信号输出采用300~500 MHz的LC滤波器,既可以滤除2.8 GHz时钟信号,又可以对300 MHz以下的低频串扰信号进行抑制。

2.3 变频设计

将300~50 0MHz的DDS信号变频至5~7 GHz可采用多种变频方案实现。考虑到选用的DDS输出信号带宽仅200 MHz,如直接将DDS信号上变频则混频后的开关滤波器组通道太多,造成设备量大、成本高,因此DDS输出信号首先必须进行带宽拓展,带宽拓展可采用倍频和混频的方式,倍频方式成本低,体积小,但恶化了杂散、相位噪声指标,混频方式成本高,体积大,但不会恶化杂散、相位噪声指标,结合本频率源技术指标要求进行分析后,决定选用倍频方式,虽然恶化了杂散、相位噪声指标,但最终输出信号能够满足要求。二倍频器选用minicircuits公司的SYK-2R,该二倍频器对基频及三次谐波的抑制高达35 dBc,在二倍频器后放大滤波,然后输出600~1 000 MHz的信号。

4.4 ~6 GHz的本振信号也可采用多种方案产生,如五个锁相源+单刀五掷开关(该方案成本高,体积大,故障率相对高),或用宽带数字锁相源(该方案频率切换时间较长)。经过分析最终采用谐波谱发生器+五路开关滤波器组的方案。该方案体积小,频率切换时间短,故障率低。将100 MHz基准信号四倍频后产生400 MHz信号,利用谐波谱发生器和开关滤波器组得到4.4~6 GHz(频率步进为400 MHz)的信号;再将此信号放大后与DDS二倍频信号混频,然后经过开关滤波器组和放大器,得到最终的5~7 GHz输出信号。

2.4 测试结果

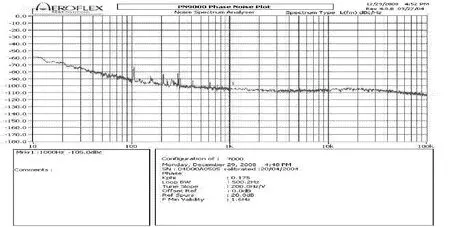

该频率源完成后对各项技术指标进行了测试,均满足技术设计要求。其中带内杂散≤-65 dBc(测试仪表HP8563E);通过示波器比较输入频率切换控制码和输出射频信号检波脉冲频率切换时间≤0.1 μ s;相位噪声 ≤-105 dBc/Hz@1kHz(测试仪表为Aeroflex-Europtest公司PN9000相位噪声测试系统),如图3所示。

在高低温测试时,发现高温下输出信号的相位噪声恶化,经分析后发现该DDS芯片在高低温下对时钟信号功率电平要求有差别,环境温度越高,DDS芯片对时钟信号功率电平要求越高,在高温(+60℃)和低温(-20℃)环境温度下,DDS芯片对时钟信号功率电平的需求相差15 dB以上。由于该DDS芯片对时钟信号功率电平有上限要求,过高则易烧毁DDS芯片。因此为了DDS的正常工作且不被烧毁,对DDS信号产生电路进行了改进,增加了温度传感器,并在时钟信号输入端增加了数控衰减器,通过温度传感器采集当前环境温度信息,对照现场可编程门阵列(FPGA)内的预置温度功率校表,控制数控衰减器的衰减量,来实现时钟信号功率保持在DDS芯片正常工作所需最佳电平。

图3 相位噪声测试结果

3 结论

该频率源利用DDS芯片BTDS856高时钟、宽带宽、低杂散等特性,实现了宽带、快速、低杂散、低相噪的性能。应用于某型搜索雷达后,达到设计效果。

[1]费元春,苏广川,米红,杨明,程燕.宽带雷达信号产生技术[M].北京:国防工业出版社,2002.

[2]赵国庆.雷达对抗原理[M].西安:西安电子科技大学出版社,1999.

[3]武国机.微波电子线路[M].西安:西北工业大学出版社,1994.