视频采集存储系统的FPGA设计

2010-05-14肖姗姗庞海燕

肖姗姗,谢 云,庞海燕

(广东工业大学 自动化学院,广东 广州 510006)

常见的药片包装可以分为瓶装、袋装和铝塑泡包装三种,由于药征在实际生产过程中要经过填药、压封、切割、区分等一系列复杂的流水线作业,难免会产生药片的漏装、碎装等现象。而传统的检验方式依赖人工目测来进行,这种工作方式劳动强度大且检测效率低,不利于企业在市场中的竞争。因此,本文设计一种基于FPGA和图像处理技术的检测系统的前端处理系统,以Xilinx公司的SOPC(System on Programmable Chip)技术为背景,利用Virtex4 FPGA为物理实现载体,采用软硬件结合的方式设计了基于SOPC的图像采集存储系统[1-2]。该设计降低了整个药片处理系统设计的复杂性,同时提高了系统的稳定性,使药片检测的实时性得到极大地提高。

1 系统的硬件结构

图1所示为视频图像处理系统结构框图,主要分为:CCD控制采集模块、DDR-SDRAM读写模块、图像处理模块和VGA显示模块。系统的处理过程由I2C配置的视频解码芯片TVP5150对摄像头输出的模拟视频信号进行解码,并传输给图像采集模块。采集模块对视频数据进行格式转换,进行去交织处理,将隔行采集的数据逐行存储到DDR-SDRAM显存中,而VGA显示部分则从DDR-SDRAM中读取数据显示。

图1 系统基本结构

(1)外部存储扩展

系统图像数据为:720 bit×625 bit×30 bit=13 500 000 bit,由于要存储的视频数据量大,而Virtex4的片内存储容量有限且掉电即失,因此必须配置大容量的外部储存器。本设计扩展了 2 MB的 Flash和 16 M×32 bit的 DDRSDRAM,其中Flash在系统中用于存放程序代码、常量表以及一些在系统掉电后需要保存的用户数据[3]。而SDRAM掉电数据即失,但其存取速度大大高于Flash且可读写[4]。因而在系统中用作程序的运行空间、临时数据及堆栈区等。图2所示为基于MicroBlaze处理器构建的嵌入式系统。

图2 基于MicroBlaze构建的嵌入式系统

(2)视频采集模块

TVP5150是TI公司推出的一款超低功耗的高性能混合信号视频解码芯片,可自动识别NTSC/PAL/SECAM制式的模拟信号。并将其按照YCbCr4:2:2的格式转化成数字信号。然后以8位内嵌同步信号的ITU-RBT.656格式输出。TVP5150具有价格低、体积小、操作简便等特点。FPGA对TVP5150芯片的操作是通过I2C总线实现的,数据传输连接方式采用最简单的ITU-RBT.656方式。

2 视频采集设计

MicroBlaze处理器对TVP5150控制驱动程序可从驱动程序模版移植而来,可用于实现采集方式的配置,并将采集的视频信号存储到环形缓冲区[5]。外部模拟视频信号经TVP5150转换为数字视频信号后,即可进入FPGA并通过视频接口模块直接排列到内部环形缓冲区数据队列的队尾。当MircoBlaze处理器接收到处理器可用中断时,系统将检测环形缓冲区是否为空。非空时,可将数据队列的头部数据取出送给处理模块,同时启动处理模块对数据进行处理。视频信号经过处理模块后,即可进入FPGA内部二级FIFO缓存。当FIFO先一级满时,向MircoBlaze处理器发出数据输出中断请求。

MircoBlaze处理器响应来自FIFO的中断后,可将FIFO先一级数据取出并存储在DDR-SDRAM中。然后清空FIFO先一级。MircoBlaze处理器的采集应用程序包括以下几部分:

(1)系统复位初始化

即禁止外部中断。初始化各驱动程序,清空环形缓冲区和二级FIFO,检测处理模块,然后启动对TVP5150的控制并进行数据采集,最后启用外部中断。

(2)处理模块可用中断服务

处理模块处理完一帧数据编码即可向MircoBlaze处理器发出中断。然后由MircoBlaze处理器控制处理模块向环形缓冲区提取数据,并在环形缓冲区耗尽时等待一定时间。

(3)数据可输出中断服务

当二级FIFO先一级所准备输出的码流满时,可向MircoBlaze处理器发出中断。然后在MircoBlaze处理器控制下,将数据存储在DDR-SDRAM,最后再清空FIFO先一级。图3所示为应用程序流程图。

图3 应用程序流程图

3 视频存储控制设计

DDR控制器模块可直接与DDR-SDRAM进行交互,因此在时序控制上要求更精确、更严格。在本设计中,使用Xilinx的DDR-SDRAM控制器的IP核来实现。

整个存储系统控制逻辑可以分为4个模块,分别是时钟产生模块、数据接口模块、数据输入输出缓存模块、DDR-SDRAM控制模块。其中,数据接口模块将来自外部的数据进行缓冲重排、时钟域的转换,并且产生写、读数据所需要的指令地址信号;数据输入输出缓存模块将来自数据接口模块的同步数据、地址缓存在FIFO中,随时供DDR-SDRAM控制器读取,并将读出的数据进行缓冲;而DDR-SDRAM控制器利用了FPGA内部的DLL模块,给系统提供了2个时钟CLK和CLK2X,改善了时钟性能,减少时钟抖动,以产生使DDR-SDRAM按预期方式工作所需要的控制信号。图4所示为图像帧存控制模块的结构图。

图4 图像帧存控制模块结构图

DDR-SDRAM控制器主要是在系统上电过程及系统意外复位发生时,对控制器进行初始化设置[6]。在系统正常工作时,进行系统读、写请求指令的接受与应答,对系统访问地址的采样与同步完成所需的状态转换、时序同步等任务,为接口模块产生相应的控制信号,并为系统提供控制器状态指示信号,同时调整对应读写操作的DQS信号时序。在设计中依据控制器的状态转移图像,可使用Xilinx DDR-SDRAM控制器IP核来实现。

在IP核的生成中,FPGA芯片采用Virtex-4系列的XC4VSX25,DDR-SDRAM型号为 Infineon_DDR_HYB25D2 56800AT_T,连接在OPB总线上,该款内存条支持最高工作频率为100 MHz,数据位宽为32 bit。13位模式寄存器的设置如下∶0_0100_0011_0010,即 BL(BurstLength)=4,CL(CASLateney)=3,BT(BurstType)=1(顺 序 方 式 ),twr(WriteReeove)=3。当所有相关设置完毕之后,点击“Generate”就能生成DDR-SDRAM接口的IP核。生成的存储系统配置如图5所示。

在Xilinx的EDK仿真软件中,FPGA仿真器将DDR的BIT文件下载到FPGA内运行,如图6所示。

4 应用系统结果验证

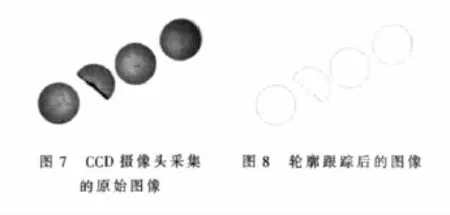

以药片作为该系统的检测对象,在MicroBlaze的控制下,摄像头读取图片并存储于DDR-SDRAM中,后经图像处理模块处理,CCD摄像头采集到的原始图像与轮廓跟踪后图像对比如图7、图8所示。

本文设计了基于SOPC的图像采集存储系统,该系统作为基于FPGA的药片检测系统的前期设计充分利用了FPGA内部预先嵌入的软核MicroBlaze,与一般使用“单片机+DSP”的多核图像处理系统比较,减少了系统所需的器件、缩小了系统的板上面积。采用软硬件协同设计的方法,明显降低了系统设计的复杂性,同时提高了系统的稳定性,使药片检测的实时性得到极大地提高。

[1]韦存刚,金星.基于FPGA的多路数据采集和控制模块设 计[J].微 计 算 机 信 息,2008,6(2)∶231-232.

[2]李莺.DDR SDRAM控制器的设计及 FPGA实现[J].攀枝花学院学报,2007,24(6):33-37.

[3]吴健军,初建朋,赖宗声.基于 FPGA的 DDR SDRAM控制器的实现[J].微计算机信息,2006,22(1):164-165.

[4]郑佳,李永亮,李娜.基于FPGA的DDR控制器的实现[J].无线电工程,2007,37(10):27-29.

[5]薛林.高速 PCI数据采集卡的设计与实现[D].南京:南京理工大学,2006.

[6]刘瑰,朱鸿宇.通用 DDR SDRAM控制器的设计[J].微型机与应用,2004(8):23-24.