HIRFL-CSR电源数字控制系统硬件平台设计

2010-03-24焦喜香乔卫民马云海

焦喜香 敬 岚 乔卫民 马云海

1(中国科学院近代物理研究所 兰州 730000)

2(中国科学院研究生院 北京 100049)

HIRFL-CSR由注入器、束运线、主环(CSRm)、实验环(CSRe)及连接主环与实验环的次级放射性束流线(RIBLL2)等组成,总长~500 m,它是一个集加速、累积、冷却、储存、内/外靶实验及高分辨粒子探测于一体的大型实验装置[1]。其工作电源均为拓扑结构,各有特点,但以大功率直流稳流电源为主,负载多是要求大激励电源的磁铁负载。且随着加速器技术的发展,对束流稳定性的要求提高,对电源系统的输出稳定性、控制分辨率及长期可靠性的要求也不断提高。数字化控制电源可明显改善电源的稳定性和控制分辨率,简化电源和上层控制系统的结构[2]。该电源的数字控制系统设计基于现场可编程逻辑门阵列(FPGA)的可再编程功能和强大的逻辑功能,以完成调节器的算法,通过软件设置电源调节器参数,便可实现对不同磁铁电源的数字控制,使磁铁电源系统的参数更精确。

1 数字控制硬件系统总体结构及设计思想

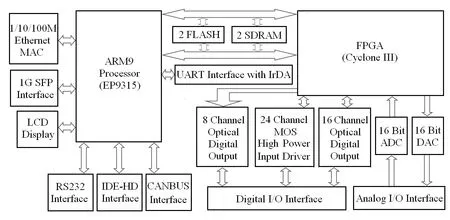

该磁铁电源系统要达到万分之一精度、ms级的响应速度和远程可调节性,考虑到对网络功能和系统配置的较高要求,以及性价比和功能扩展,该硬件平台用基于以太网技术的分布式系统架构,采用硬件在线升级能力强的FPGA+ARM结构,以实现数字调节器算法对加速器磁场电源的精确控制。其硬件结构如图1,由ARM9处理器、FPGA、AD/DA转换器及其外围电路、存储器、光模块通信单元、LCD液晶显示电路、USB键盘电路、红外串行接口单元、RS232串口通信和 CANBUS接口等组成。系统整体主要完成程序及命令的输入、测量参数的数字处理、光模块数据通信、图形界面显示及与PC机通信等。将符合要求的数字调节器控制算法程序通过JTAG口下载烧写到平台FLASH存储器中,由ARM作整个系统的控制核心,运行数控系统的控制软件,将用户输入的给定参数传输到 FPGA,用其控制算法计算,生成符合被控对象输入要求的输出信号对被控对象进行实时的调节和控制。

图1 系统硬件平台的结构框图Fig.1 Block diagram of the digital adjuster hardware system.

2 系统数字控制模块的设计

2.1 Cyclone III模块

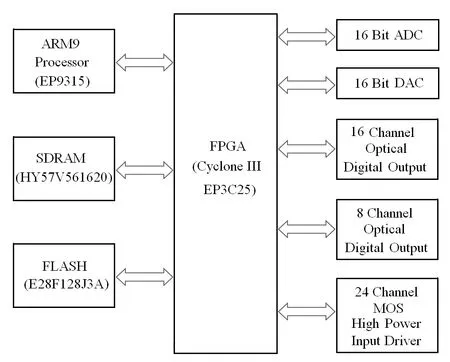

选用Altera 公司65-nm工艺、内嵌DSP处理模块Cyclone III系列的EP3C25 FPGA作为数字调节器控制器的算法核心元件。在FPGA内实现数字调节器及控制高精度脉宽调制信号 PWM(pulse width modulation)波的输出。系统的反馈输入,即负载电流和电压及前馈电压的回采值,通过 ADC转化为数字量送给FPGA,由FPGA实现对ADC/DAC的控制。硬件结构如图2。

图2 Cyclone III控制接口逻辑图Fig.2 The structure of Cyclone III connected with peripheral devices.

2.1.1 FPGA配置电路

为方便系统编程与调试,设计 AS(主动串行)配置端口,并采用 JTAG(边界扫描)配置端口。在AS配置方式中,FPGA须与Altera公司专用的AS串行配置器件配套使用。我们采用的EP2S16(Altera公司)是一种非易失性的、基于FLASH存储器的器件,可用该公司的ByteBlaster II加载电缆对其编程。这样可通过JIAG口在线改变FPGA内部逻辑进行调试,或改变配置芯片以便FPGA启动时自动下载,为后期调试、现场应用提供便利。

2.1.2 FPGA外部设备及传输信号类型

FPGA可实现外部设备控制逻辑包括高精度ADC/DAC、驱动功率开关管脉宽调制信号的控制,与EP9315的通信控制,及电源数字调节器的实现,针对用户输入的具体被控对象指标,得到适合的数字调节器参数,增加了系统的灵活性。FPGA具体的接口控制逻辑包括电源参数的采样输入控制、电源参数量的输出控制、数字端口的状态控制、大功率器件的输出驱动、微处理器及外围器件的控制。同时FPGA还嵌入串行千兆光纤接口芯片,直接接收外界DSP处理的数据,无需外接DAAD等转换器件,不受转换器件性能参数的制约。

2.1.3 数字调节器的FPGA控制

数字调节器FPGA采用基于浮点数的处理。由16位模数转换器 ADC 对磁铁电源的输出进行采样,得到16位定点数,然后将其转换为24位浮点数形式送给数字解算器,并将数字解算器输出与给定相加后,针对具体被控对象要求,生成相应的输出实现对被控对象的控制。为保证数字调节器的运行速度及实现FPGA有限逻辑资源的高效运用,数字调节器的设计采用 7级流水线式的数据处理流程,将间隔时间控制在矩阵乘法器的延迟时间 200 ns以内,达到设计的初始要求。

2.2 ARM9处理器(EP9315)模块

该系统以ARM9处理器为控制器核心,完成系统的多线程任务处理,包括FPGA数控单元的数据通信、外界接口的扩展控制及并行完成网络通信、触摸屏接口驱动、数据回读等多项任务。

处理器选用Cirrus Logic的EP9315,它是基于ARM架构的32 bit RISC微处理器,内嵌先进的运行于200 MHz的ARM920T微处理器核,支持32位ARM指令集和16位Thumb指令集,还有五级流水线和单一32位AMBA总线接口;处理器采用Harvard体系结构设计;存储器管理单元(MMU)支持Linux、Windows CE等许多嵌入式操作系统;片内集成一个Maverick CrunchTM数字协处理器,可提高ARM920T的浮点运算、整形运算与信号处理能力;集成看门狗电路有效解决死机问题,提高了系统可靠性,有功能优越、低功耗、性价比高的性能。

2.2.1 存储器设计

硬件平台需为操作系统和应用程序提供运行空间,且采样的电源数据经AD转换后,由FPGA的IO接口传入到EP9315存储器中暂时缓存,但EP9315用于DMA方式的内部FIFO容量很小,远不满足高速、连续和大容量数据采集处理要求,且处理器内部集成同步动态随机存储器(SDRAM)控制器、FLASH和静态存储器控制器的专门电路,因此在局部总线上外加存储器用于程序运行空间和数据的缓冲存取。选用2片HY57V561620并联组成32位数据宽度、512MB存储容量的SDRAM存储器;2片E28F128J3A组成256M的Flash作程序代码、掉电后需保存的数据存储器;存储器支持统一的寻址模式,所有存储器设备都可通过一组公共的地址总线和数据总线进行访问。

碳关税模块包括两个部分:一是通过碳排放因子对相应的碳排放系数进行计算,二是通过对出口商品含碳量进行碳关税的征收。具体碳排放系数计算如式(5)所示:

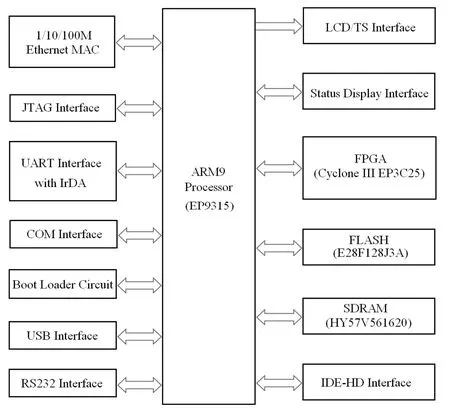

2.2.2 系统各种接口功能

调节器硬件控制系统中,处理器 EP9315内部集成一个高性能1/10/100 Mbps以太网媒体访问控制器(MAC),通过与支持MII接口的外置PHY IC KS8721BL连接,在半双工或全双工模式下提供10M/100Mbps以太网接入,实现系统在远程中央控制中心的显示、在线测试和远程控制。另外还有键盘/鼠标接口、LCD显示和触摸输入接口、IDE硬盘控制器接口、CAN BUS接口、RS232串行通信接口、红外串行接口。这些接口能满足加速器控制所需各种工业标准接口,可连接现场各种设备,提供控制所需的硬件通道。硬件连接逻辑如图3。

图3 EP9315外围控制接口逻辑图Fig.3 The structure of EP9315 connected with peripheral devices.

3 供电单元与系统PCB的设计

3.1 供电单元

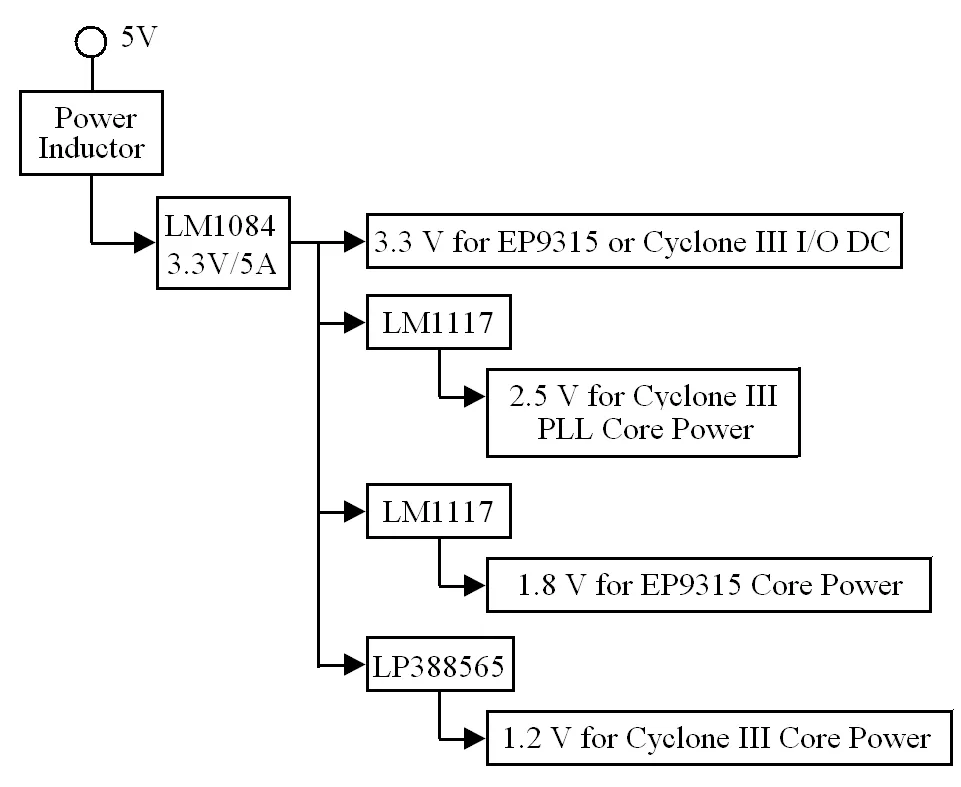

一个硬件系统中供电单元的稳定准确至关重要。本系统供电单元的电源值较多,包括AD转换器工作电压为5 V、其外接的运放需±15 V双电源供电,EP9315和CYCLONE III I/O功能模块的工作电压为3.3 V,CYCLONE III的PLL工作电压为2.5 V,EP9315和CYCLONEIII的内核工作电压分别为1.8和1.2 V。根据本系统工作特点,电源部分须提供用于模块数据发送的瞬时大电流,同时保证给处理器和FPGA提供高质量内核工作电压,所以电源电路经过两级滤波且用稳压芯片实现各电压转换。外部电压源给定+5 V电源输入,经DC-DC芯片转换为内部需要的±15 V,输出电流~1 A,满足系统要求。经稳压器件LM1085、LM117和LP38856S分别转换为3.3、2.5、1.8、1.2 V。具体结构如图4。

图4 系统电源部分的结构图Fig.4 The structure of the system’s power.

3.2 PCB设计

设计硬件系统的PCB时,电源部分由±15、5、3.3、2.5、1.8、1.2 V组成,把整层电源平面铺铜,在特殊芯片下分割电源区,给定合适电源。地平面也铺铜,通过单点和机箱地相连,减小强电信号干扰。电路中USB和SATA信号线最好不要跨岛(跨过相邻电源或地层分隔区域),保证这些信号下面是完整地平面或电源平面。系统中差分信号线尽量走同一平面,保证等长,等间距且间距尽量小,降低EMI,保证信号质量。系统中SDRAM和flash存储器运行频率较高,设计时要尽量保证所有数据线和控制信号线等长(相差12.7–25.4 mm)。

4 系统引导程序的设计

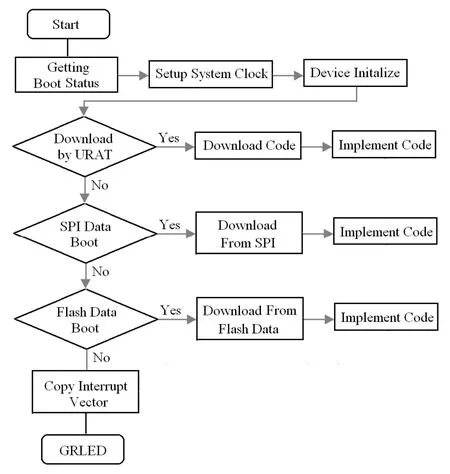

引导程序驻留在EP9315处理器的片内ROM里,当系统上电复位后,ARM920T微处理器核首先从复位地址0x0处读取启动代码,EP9315通过硬件选择,将不同的启动设备映射到0x0地址。EP9315 Boot ROM代码支持多种方式启动系统,包括内部UART下载启动,多种非易失存储器的应用系统引导方式,如SPI连接的Data Flash串行下载、两线连接的EEPROM和在NCS0空间的8位并行存储器[3]。

图5 Boot ROM流程图Fig.5 The flow chart of Boot ROM.

5 结论

该数字控制处理硬件平台以大规模FPGA和微处理器ARM为核心,支持Linux操作系统,支持PID算法,支持工业千兆光纤传输和数字显示,外接端口丰富,为现场运用调试提供方便。且CYCYLONEIII FPGA的65 nm工艺及内嵌DSP乘法器大大减小整个系统 PCB面积,保证系统低功耗、低成本和高性能及算法逻辑的实现。整个系统有良好的灵活性、通用性和可靠性。

1 王彦瑜, 郭玉辉, 林飞宇, 等.强激光与粒子束, 2008,20(8): 1353–1356 WANG Yanyu, GUO Yuhui, LIN Feiyu, et al.High Power Laser Part Beams, 2008, 20(8): 1353–1356

2 龙锋利, 程 健.原子能科学技术, 2009,43(11):1043–1048 LONG Fengli, CHENG Jian.At Energy Sci Technol, 2009,43(11): 1043–1048

3 敬 岚, 乔卫民, 徐 扬, 等.核技术, 2006, 29(10):791–795 JING Lan, QIAO Weimin, XU Yang, et al.Nucl Tech,2006, 29(10): 791–795

4 李驹光, 郑 耿, 江泽明.嵌入式 Linux开发详解──基于EP93XX系列ARM.北京: 清华大学出版社, 2006 LI Juguang, ZHENG Gen, JIANG Zeming.Embedded Linux system development technology explain──based on EP93xx ARM.Beijing: Qinghua University Press,2006