基于FPGA的数字基带传输系统编译码器的设计

2010-01-18李敏

李 敏

(湖北民族学院 信息工程学院,湖北 恩施 445000)

尽管在现代数字通信系统中基带传输不如频带传输那样广泛,但对于基带传输系统的研究仍然是十分有意义的,它仍属于数字通信系统的重要组成部分[1].随着计算机网络通信的发展,数字基带传输有着迅速发展的趋势.它不仅可以用于低速数据传输、高速数据传输,而且还可以是数字频带传输的基础.为使数字基带信号能在基带传输系统中顺利传输,就必须选择合适的码型,即对基带信号进行编码.在众多的码型中,HDB3(三阶高密度双极性码)因其无直流成份,低频成份少和连“0”个数最多不超过三个等优点,对定时信号的恢复和内在纠错都十分有利,而成为ITU推荐使用的基带传输码型之一[2].因此本文中的基带码型选用HDB3码.

1 HDB3的编译码规则

HDB3是AMI(极性交替反转码)的改进型,不仅要保持AMI码的优点,同时又要克服其连“0”串过长而导致的位定时提取困难.它的编译码规则简单介绍.HDB3码(三阶高密度双极性码)的编码规则[2]如下:

1)检查连“0”情况,若没有4个或4个以上的连“0”串,此时HDB3码”等同AMI码,即“1”码变为“+1”、“- 1”交替脉冲;否则,每4个连“0”用“000V”或“B00V”代替,其中“V”符号称为破坏符号.替代规则为:当相邻两个“V”符号之间有奇数个“1”时,用“000V”取代4个连“0”.当相邻的两个“V”符号之间有偶数个“1”时,用“B00V”取代4个连“0”.

2)相邻“V”符号的极性也应交替反转,且“V”符号的极性总与前一个非“0”符号的极性相同.因此,“V”符号被称为破坏符号.

3)“B”符号的极性与前一个非“0”符号的极性相反,并使其后的非“0”符号从“V”符号开始再交替变化.

通过HDB3编码,码序列中连“0”串减少到最多3个,这使从对应的基带信号中恢复出位定时信息是非常有利的.HDB3码的编码规则虽较复杂,但其译码却比较简单[3].从编码可见,每一个破坏符“V”总是与前一个非“0”符号极性相同,根据这一特点,可以迅速从收到的符号序列中找出破坏点“V”,而且该符号及其前面的3个符号必为“0”符号,从而可恢复出序列中的4个连“0”代码,然后再将其他的非“0”符号译码为信息序列中的代码“1”,“0”符号译为信息序列中的代码“0”.

2 编译码器设计方案

2.1 HDB3编码器的设计

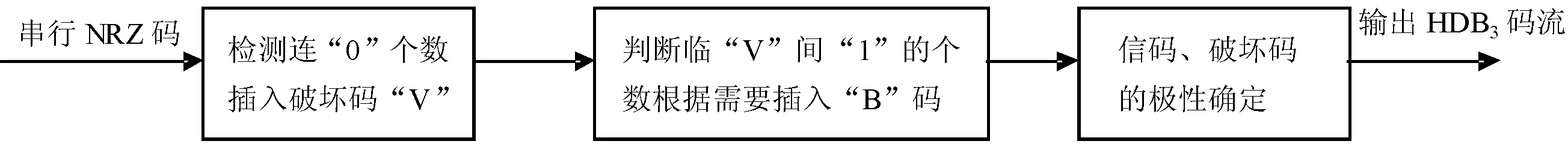

根据HDB3的编码规则以及VHDL不能处理负电平的特点,HDB3的编码模型[4]如图1所示.

图1 HDB3的编码模型

图2 HDB3码译码电路原理图

由图1可知实现HDB3编码分三步执行.首先检测连“0”的个数,一旦检测到四个连“0”便输出一相应的指示信号,并在第四个“0”的位置上用破坏码“V”代替;第二步则是在插入破坏码“V”之后检测两相邻“V”信号间信码“1”的个数N,从而去确定四连“0”是用“B00V”还是“000V”所取代.若N为奇数,则四连“0”用“000V”所取代,若N为偶数,则四连“0”用“B00V”所取代.当四连“0”被“B00V”所取代时,可通过设计一脉冲插人电路实现“B”信号的插入;最后便是确定信码与破坏码的极性.根据HDB3编码规则,信码与破坏码的极性均应满则交替出现的规则,因此极性形成电路应具有信码正负交替极性的形成和破坏码正负交替极性的形成两个功能.由于FPGA无法实现双极性的输出,所以要实现HDB3编码得在上述基础上外加一个极性转换电路,这可采用集成芯片或采用分立元器件来实现.

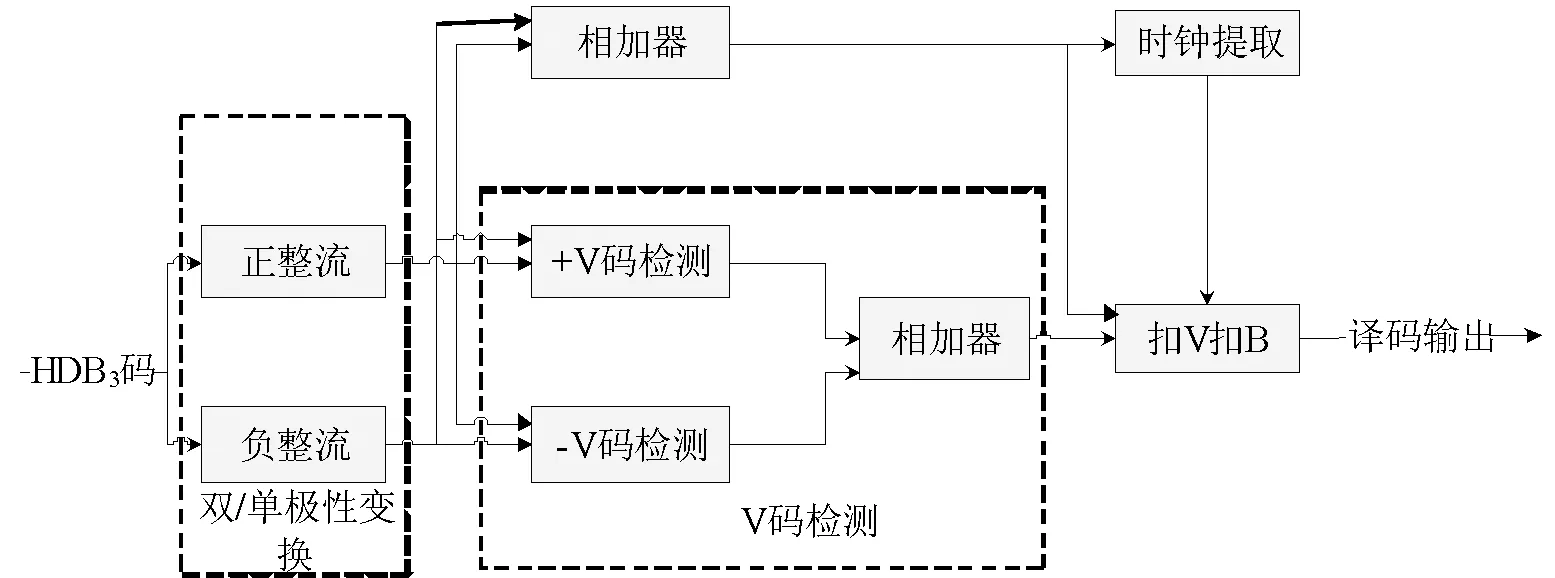

2.2 HDB3译码器的设计

HDB3译码主要任务就是要找出相邻两个极性相同的码元,即后一码元一定属于破坏码“V”,根据HDB3编码规则可知,该破坏码“V”及其前三个码元一定均是“0”,因此只需将该破坏码“V”及其前三个码元恢复成“0000”即可.经分析得HDB3译码模型如图2所示,它包括双/单极性变换、V码检测、时钟提取、扣“V”扣“B”[5]四个模块.图中双/单极性变换模块由提取正极性电平的正整流电路和提取负极性电平的负整流电路组成. “V”码检测模块完成破坏码“V”的检测,因破坏码“V”破坏极性交替出现的特点,当连续出现两同极性码元时且在无误码的情况下,后一码元一定属于破坏码“V”,一旦检测出来给出指示信号“P”.扣“V”和扣“B”模块则是在指示信号“P”和同步时钟脉冲的控制下,完成 “V”及其前三个码元的取代,即将“B00V”或“000V”恢复成 “0000”.时钟提取模块则是为了提取同步时钟,通常采用锁相环来完成[6].

3 仿真及结果分析

在选用FPGA来实现某一功能时,一般都要通过设计准备、设计输人、功能仿真、设计处理、时序仿真、器件编程与测试几个步骤.最终设计实现的目的就是在FPGA中物理实现所需逻辑功能,这个过程主要在Quartus II[7]中的编译器完成.它根据设计输人文件自动生成用于器件编程、波形仿真及延时分析等所需的数据文件.在本设计中选用的是Altera公司FPGA(EP1C6Q240C8N)芯片.

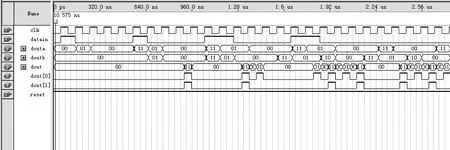

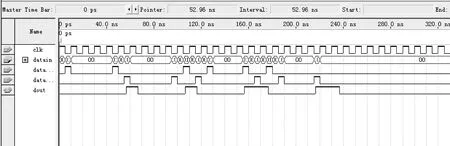

编译码器在Quartus II上经过仿真调试得到编译码仿真波形分别如图3和图4所示.

图3 HDB3编码仿真波形图

图3HDB3编码仿真波形图中datain为输入NRZ码流10000100001100001100000000,dataa为插入破坏码输出波形,即在一旦检测到4连“0”时在第四个“0”位置上插入破坏码“V”.因VHDL不能处理负电平,故“1”、“0”、“V”分别用双相码“01”、“00”、“11”表示.datab为插入“B”码输出波形,即在检测到两相邻“V”间有偶数个“1”时4连“0”用“B00V”表示,在这里“B”用双相码“10”表示.dout为单极性转双极性输出波形,即“1”码和“V”码均各自要服从正负交替原则,这里依然用双相码表示,经验证,输出结果是符合HDB3编码规则的.

图4 HDB3译码仿真波形图

由图4HDB3译码仿真波形图dout输出波形可知该仿真能得到正确的结果,因此在经过正确的仿真后,即可进行器件编程,即通过编程电缆下载数据流到EP1C6Q240C8N芯片并进行硬件测试,完成整个设计工作.

4 结束语

实验结果表明,选用FPGA实现HDB3码的编译码相对于选用专用集成电路具有很多优势,减少了繁杂的电路设计与调试,缩短了设计周期,同时利用其可编程性还可以在该FPGA芯片中集成其他电路所能完成的功能,实现多种功能.这种基于FPGA的HDB3码的设计实用、方便、简单易行,能够运用于实际项目中.

[1]南利平,李学华.通信原理简明教程[M].北京:清华大学出版社,2007:176-177.

[2]樊昌信,张甫诩,徐炳祥.通信原理[M].北京:北京国防工业出版,2006:96-98.

[3]吴海涛,陈英俊,梁迎春. 基于FPGA的HDB3编解码器设计[J].微计算机信息,2008,24(62):236-238.

[4]谭立志.三阶高密度双极性信号编译码的建模与仿真[J].现代电子技术,2008,274(11):21-23.

[5]蒋青,吕翊. 一种基于FPGA技术的HDB3译码器的设计[J].微电子学,2007,37(2):298-300.

[6]King M S,Chung J G. Look2up table based pulse2shaping filter[J].Electronics Letters,2002,36(17):1 505-1 507.

[7]张巧文,朱仲杰,梁丰,等.HDB_3编译码器的优化设计与实现[J].西南交通大学学报,2008,43(1):25-26.