基于Simplorer的锁相环电路建模与仿真分析

2010-01-18吴长坤廖红华

吴长坤,廖红华

(1.湖北民族学院 附属医院, 湖北 恩施 445000;2.湖北民族学院 信息工程学院, 湖北 恩施 445000)

锁相环(Phase-Locked Loop,简称PLL)电路是一种相位负反馈电路,其作用在于能使电路的时钟与外部时钟相位同步.PLL具有锁定时无剩余频差、良好的窄带载波跟踪性能、良好的宽带调制跟踪性能、门限性能好等优点[1~6].广泛地应用于频率合成与频率转移、自动频率调谐跟踪、模拟和数字信号的相干解调,AM波的同步检波、数字通信中的位同步提取、锁相测速与测距、微波锁相频率源以及微波锁相功率放大等领域.文中通过对锁相环路进行数学分析,建立锁相环数学模型,采用VHDL-AMS进行行为级建模,在SImplorer7.0环境下架构锁相环模型,并进行仿真分析.

图1 锁相环的基本构成

1 锁相环的数学分析

锁相环主要包含鉴相器、环路滤波器以及压控振荡器等部分[7].其基本构成框图如图1所示.其中,压控振荡器输出信号uo(t)的相位与参考信号ur(t)的相位进行比较,产生相位误差电压ue(t)来调整压控振荡器输出信号的相位,达到输出信号与参考信号同频的目的.其中鉴相器(PD)为相位比较装置,实现压控振荡器输出信号uo(t)的相位与参考信号ur(t)的相位比较,产生两个信号相位差φe(t)的误差电压ue(t).

图2 无源比例积分滤波器示意图

设参考信号ur(t)为:

ur(t)=urmsin[ωrt+φr(t)]

(1)

压控振荡器输出信号uo(t)为:

uo(t)=uomcos[ωot+φo(t)]

(2)

其中φr(t)是以ωrt为参考相位的瞬时相位,φo(t)是以ωot为参考相位的瞬时相位.一般情况,ωo不一定等于ωr,为便于比较两者间的相位差.若以输出信号的ωot为参考相位,则ur(t)的瞬时相位可表示为:

ωrt+φr(t)=ωot+[ωr-ωo]t+φr(t)=ωot+φ1(t)

(3)

其中:

φ1(t)=[ωr-ωo]t+φr(t)=Δωot+φr(t)

(4)

式中Δωo=ωr-ωo为固有频率差,即参考信号角频率与压控振荡器振荡信号频率之差.

令φ2(t)=φo(t),则式(1)和(2)可重写为:

(5)

将式(5)中uo(t)与ur(t)作为乘法器的两个输入,且设乘法器的相乘系数为km,则其输出为:

(6)

式(6)中第一项为高频分量,通过环路滤波器(LPF)即可滤除.滤除高频分量后,则有误差电压ue(t)表示为:

(7)

环路滤波器(LPF)实现误差电压ue(t)中高频分量及噪声的滤除,改善PLL系统的稳定性,该部分参数的选择对于环路带宽、稳定性起决定性作用.常用的环路滤波器(LPF)有RC积分滤波器、无源比例积分滤波器、有源比例积分滤波器和有源RC积分滤波器等.下面以无源比例积分滤波器建立环路滤波器模型为例进行分析,其示意图如图2所示.

由图2有,环路滤波器传递函数能表示为:

(8)

若系统的单位冲激响应为h(t),则环路滤波器的输出、输入关系的表达式又可写成 :

(9)

压控振荡器(VCO)为电压/频率变换器,压控振荡器(VCO)在环路滤波器输出电压uc(t)的控制下,使压控振荡器的振荡频率向参考频率靠近,直至两者的频率相同、保持一个较小的剩余相差为止,所以锁相环实质就是压控振荡器受外部参考信号控制,使得压控振荡器的输出信号的相位和外部参考信号的相位保持某种特定的关系,从而达到相位锁定.

压控振荡器的振荡频率ω0(t)受控制电压uc(t)的控制.不管压控振荡器的形式如何,其特性总可以用瞬时角频率ω0与控制电压之间的关系曲线表示.当uc=0,仅有固有偏置时的振荡角频率然ωc0称为固有角频率.必ω0以ωc0为中心而变化.在一定的范围内,ω0与uc呈线性关系.在线性范围内,其控制特性可表示为:

ω0(t)=ωc0(t)+Kvuc(t)

(10)

式(10)中,Kv为特性斜率,表示单位控制电压可使VCO角频率变化的数值,又称为VCO的压控灵敏度.因压控振荡器的输出对鉴相器起作用的不是瞬时频率,而是它的瞬时相位.该瞬时相位可对式(10)积分求得:

(11)

故:

(12)

由此可见,压控振荡器在环路中起了一次理想积分的作用.因此压振荡器是一个固有积分环节.若用微分子p表示,则上式可表示为:

(13)

由此可得压控振荡器的数学模型.

2 锁相环的VHDL-AMS建模

利用VHDL-AMS对PLL各模块建模,鉴相器(PD)、环路滤波器(LPF)以及压控振荡器(VCO)的VHDL-AMS模型分别如图3(a)、(b)、以及(c)所示.

图3(a) 鉴相器(PD)的VHDL-AMS模型 图3(b) 环路滤波器(LPF)的vhdl-ams模型 图3(c) 压控振荡器(VCO)的VHDL-AMS模型

图3(a)中,k为乘法器增益系数;图3(b)中,k为LPF增益系数,fp为极点频率,fz为零点频率,图3(c)中,kv为压控灵敏度,fco为VCO固有频率.

3 仿真结果与分析

3.1 压控振荡器(VCO)仿真与分析

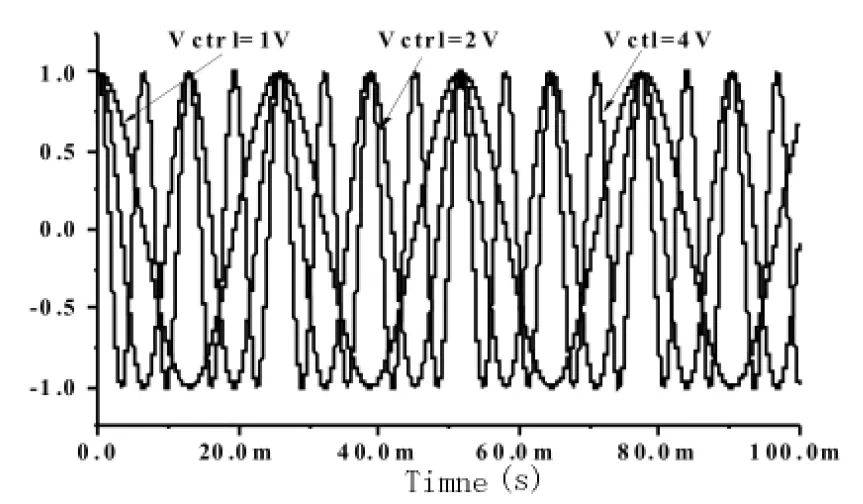

1)压控振荡器输入信号对输出信号的影响 仿真分析时,设输入信号的频率为20 kHz时,压控振荡器的压控灵敏度kv为20,固有频率为10 Hz时,仅改变输入信号的幅值,输入电压幅值分别为1、2、4 V可得到如图4所示的VCO输出波形.

从图4易知,当输入信号的幅值分别为1、2、4 V时,输出信号频率呈线性递增,由此可知:随着输入信号幅值增大时,输出信号频率随之增大,且输出的峰峰值不变化.

在此基础上,仅改变输入信号的频率,即输入信号频率分别设为1、10、20 kHz,仿真结果表明:无论输入信号的频率怎么改变,VCO输出信号不变.

2)压控灵敏度对输出信号的影响 设输入信号的幅值为2 V,频率为20 kHz时,压控振荡器的固有频率为10 Hz时,仅改变压控振荡器的压控灵敏度,压控灵敏度分别为30、20、10可得到如图5所示的VCO输出波形.

图4 压控振荡器输入电压对输出信号的影响

图5 压控灵敏度对输出信号的影响

由图5易知,改变压控振荡器压控灵敏度,压控振荡器输出信号的频率将随之变化,且随着压控灵敏度的降低,压控振荡器压输出信号频率随着增加.

3.2 锁相环(PLL)的仿真与分析

仿真分析时,设输入信号的频率为100 Hz;鉴相器的增益系数为1;环路滤波器的增益为1,极点频率为200,零点频率为10 000 Hz;压控振荡器的压控灵敏度为10,固有频率为100 Hz时.仅改变输入信号幅值,且输入信号的幅值是分别为1、2、4 V时,PD、LPF以及VCO模块的输出波形如图6所示.

图6 输入电压改变对PLL输出波形影响,其中图(a)为输入信号波形,图(b)为PD输出波形,图(c)为LPF输出波形,图(d)为VCO输出波形

从图6易知,随着输入信号的幅度增大时,鉴相器、环路滤波器输出幅度均随之增加,而VCO的输出幅度、频率基本不变,说明了PLL具有很强的锁相能力,且在当前条件下,PLL在450~500 Hz的频率范围内具有良好的跟踪能力.

4 结束语

通过对锁相环电路的数学分析,利用VHDL-AMS语言对鉴相器、环路滤波器以及压控振荡器进行行为级建模,并在Simplorer 7.0环境下仿真.仿真结果表明,采用VHDL-AMS语言对模型的行为级建模,具有概念清晰、仿真简捷、高效,仅通过调整模型参数即可对系统性能进行全面分析.

[1]Young I A,Jeffrey K G,Wong K L,et al.A PLL clock generator with 5 to 110 MHz of lock range for microprocessors[J].IEEE Journal of Solid-State Circuits,1992,27:1 599-1 607.

[2]Mirabbasi S, Martin K.Design of loop filter in phase-locked loops[J]. Electronics Letters,1999,35:1 801-1 802.

[3]Park C H, Kim O, Kim B.A 1.8-GHz self-calibrated phase locked loop with precise I/Q matching[J]. IEEE Journal of Solid-State Circuits,2001,36:777-783.

[4]Kyoohyun L,Park C H,Kim D S,et al.A low-noise phase-lock loop design by loop bandwidth optimization[J]. IEEE Journal of Solid-State Circuits,2000,35:807-815.

[5]仇善忠,张冠百.锁相与频率合成技术[M].北京:电子工业出版社,1986:7-14.

[6]李文英,蒋敦斌.锁相环中鉴相器特点及其与压控振荡器的关键使用技术[J].测控技术,2008,27(3):142-208.

[7]郑继禹,万心平,张厥盛.锁相环路原理与应用(第2版)[M].北京: 人民邮电出版社,1984:30-36.

[8]杨庆.基于VHDL与CPLD器件的FIR数字滤波器的设计[J].湖北民族学院学报:自然科学版,2005,23(1):66-68.