利用计算机并口ECP模式实现计算机对外围设备的控制及数据采集

2009-01-06叶青青

叶青青

[中图分类号]R562.25[文献标识码]A[文章编号]1007-9416(2009)11-0121-04

1 并行口简介

并行口是PC机的常用接口。并行口由4根控制线,5根状态线及8根数据线构成。并行口位于PC机背面,通常为D-25针母座,也有的是D-25针公座。并行口有5种向下兼容的操作模式,分别是:兼容模式(Compatibility Mode)、半模式(Nibble Mode)、BYTE模式(Byte Mode)、EPP模式(EPP Mode)和ECP.模式(ECP Mode)。兼容模式(SPP)、半模式、Byte模式均是软件握手,速率只有50KByte/s,最多也就是150KByte/s。EPP、ECP模式都是硬件握手,传输速率相近,速率最高可达2Mbyt/s。EPP模式5根状态线中只用了2条,因而在实时双向通信中能力显得不足,且ECP模式可以使用FIFO缓冲器来发送/接收数据同时在Windows下还可以使用DMA通道来移动数据,因而ECP模式更适用。

2 ECP说明

(1)ECP协议里有一个叫做Run Length Encoding的简单压缩配置,它的最大压缩比率是64:1,且它对发送重复单一字节的数据采用计数和COPY一个字节的方式工作,计的数确定重复字节的个数。例如,要发送出25个‘A,首先发送24紧随其后是‘A。外围设备接收到之后通过计数24及‘A恢复出25个‘A, 这对于像扫描仪、打印机那样数据比较长的外设来说,是非常好的并行接口。

压缩的 Byte在数据处理路径上有别于其它Byte,它作为指令被送到ECP的地址FIFO端口(ECP Address FIFO),发送到Address FIFO寄存器的字节可能是两种东西,一是压缩数据长度的计数,二是字符的ASCI码。压缩Byte的MSB为1,那么其它7个BIT(BIT0—BIT6)代表的就是字符的ASCI码;如果压缩Byte的BIT7为0,那么在其它BIT位传输的就是一个压缩数据长度的计数。

(2) ECP硬件特性

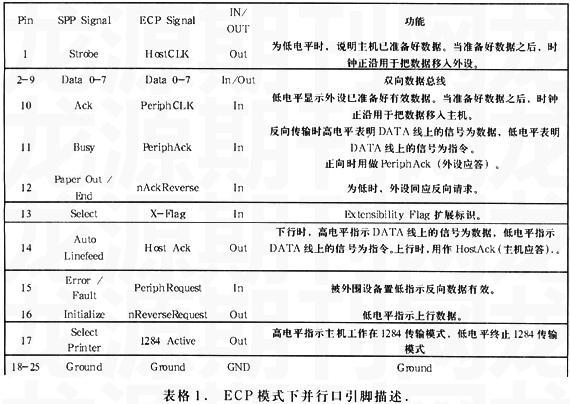

普通计算机只有一个并行接口,ECP、SPP、EPP只是并行接口的几种工作模式,它们之间的差异就在于引脚

功能分配的不同,软件运行的方式不同。SPP是软件握手,EPP、ECP是硬件握手,但ECP和EPP硬件握手的方式还不同。ECP向后兼容SPP、EPP,当它工作在SPP模式时,并行端口上的每个数据线的用途与工作在SPP模式下并行口上的数据线的用途完全相同。当它工作在EPP模式时,并行端口上的每个数据线的用途与工作在EPP模式下并行口上的数据线的用途完全相同。当计算机工作在ECP模式下时,25脚并行接口各引脚功能定义如下表:

(4)ECP软件寄存器

表格2列出了ECP寄存器的内容。前三个寄存器和SPP寄存器几乎完全相同,只是控制端口寄存器的Bit5位特殊,在ECP模式里它控制并行口的收发方向,进而影响ECR寄存器的FIFO Full及FIFO Empty Bit位。

当并行口工作在SPP模式时,基地址通常被称为数据端口或数据寄存器,它使用简单,用于把数据放到并行口的数据线上(PINS2—9)。在标准SPP模式下,这个寄存器通常只负责把数据写到并口上,如果你想读这个寄存器,只能读到上一次发出的数据。然而如果你的并口是双向的(Byte Mode),就可以在这个地址上接收数据。当并行口工作在ECP模式时,基地址+0用作地址FIFO(见表1、表2)。

基地址+1 称为状态端口或状态寄存器,不可写。状态端口的高5位直接反映并行口的5条状态线(引脚10,11,12,13,15)的状态,Bit2是显示IRQ的状态位,Bit1、Bit0是保留位。请注意BIT7位(BUSY)低电平有效,例如,如果寄存器的第7位是‘0,那就意味着并行口的第11脚加入的是+5V,同样如果BIT2(NIRQ)是‘1那一定没有中断发生,详见表格3。

控制端口(基地址+2)又称为控制寄存器。在具体使用它时,读是没有意义的,一般用作只写,详见表格4。

基地址+402h :

基地址+402h是ECP的扩展控制寄存器(ECR),ECR设定在那一种模式ECP端口就将工作在那一种模式。

ECR的高三位字节用于选择操作模式,共有7种模式,但并不是所有主机的并口硬件都支持这些模式,EPP就是其中一例。

Standard Mode :选择这种模式,将使ECP端口工作于SPP标准模式,但不包含双向功能。

Byte Mode / PS/2 Mode :ECP端口工作于SPP的双向模式。

Parallel Port FIFO Mode :此种模式任何数据都可写入DATA FIFO,端口使用SPP握手把FIFO中的DATA送给外围设备,而握手过程是由硬件产生的。这对于非ECP的外设如打印机是非常有用的,你可以有一些ECP的特性如FIFO缓冲器、硬件握手,它是用已有的SPP握手而非ECP握手。

ECP FIFO Mode :ECP使用的标准模式。这种模式使用的是已经讲述过的ECP握手。

EPP Mode/Reserved :对于有些计算机,这种模式就是使ECP端口工作于EPP模式;而在有些计算机里这种模式仍作为保留模式。

Reserved :保留模式。

Configuration Mode :在这个模式里共有两个配置寄存器可以用(CNFGA及CNFGB),它们都有指定的地址。

FIFO test mode:用于测试FIFO缓冲器的性能也用于确定这些功能的正确性。当端口处于这种模式时,任何写进TEST FIFO(BASE+400H)的字节都被放进FIFO缓冲器里,任何从TESTFIFO寄存器里读出的字节都是取自FIFO缓冲器。你可以使用ECR的FIFO Full及FIFO Empty的Bit位来确定FIFO缓冲器的性能,通常FIFO缓冲器有16个字节的深度。

ECR的其它BIT位在ECP操作端口中也起到非常重要的作用,ECP中断BIT(BIT4)位使能中断,DMA Enable Bit (Bit 3)使能直接内存的存取的。如果ECP?Service Bit (Bit 2)被置高说明一个中断请求已开始。不同计算机并行口使用的芯片往往不同,而不同芯片的ECP Service Bit位的复位方法可能是不同的,有些芯片需要你置0该Bit位,而有些芯片只需对ECR读一次就可实现对ECP Service Bit位的复位。

FIFO Full (Bit 1) and FIFO Empty (Bit 0)显示FIFO缓冲器的状态。由于这两个Bit位是在并行口数据传输方向已确定的条件下取得的,所以这里无需考虑Control Register的Bit5位。如果BIT0(FIFO Empty)置为1,那么FIFO缓冲器为空;如果BIT1置为1,那么FIFO缓冲器为满;如果这两个BIT位都不为1的话,说明有数据在FIFO里但它不满,这两个BIT位可用在FIFO Test Mode,用以测定FIFO缓冲器的容量。

基地址 + 400h为ECP的配置寄存器A,有关ECP端口的一些内容都可以在配置寄存器A里得到。MSB确定中断方式:边沿或电平触发,这主要依赖于你使用的并行卡。BIT4—6位列出了卡上的总线宽度,一些卡只有8位数据宽度,而有些卡却有32或16位的数据宽度。为了使你的并行卡发挥最大的效能,可以先利用软件读出这些BIT位的状态,以此决定输出端口的最大字的数据宽度(见表5)。

配置寄存器的低三位,用于主机的恢复。为了从一个错误中恢复,软件必须知道有多少个字节已送出,而获取已送出字节的方法是查看暂存于FIFO的字节数。

有些外设的输入端口可能有以Byte为单位的移位寄存器,需要并行口FIFO满之后才将数据发送给外设,Bit2就是确定并口是否FIFO满之后再传输的Bit位。还有,并行口只有8位宽度,而你需要传输字长16位或32位的指令,如果是这种情况,并行端口的字仍然能够送出。字长可能是1Byte、2Byte或4Byte,而在发生错误时整个字的一些Byte可能还未送出,此时配置寄存器的Bite0和Bite1位就指明了剩余在FIFO里的Byte数量,继而可以将剩余的Byte全部送出。

基地址+401h为配置寄存器B (cnfgB),是可读/写寄存器。一些并行口可以利用软件配置CnfgB从而设置IRQ和DMA资源。而有些端口则需设置BIO或在并行卡上跳线来设置IRQ和DMA,因此此时ConfgB为只读。

配置寄存器的Bit 7设为1时,选择使用RLE压缩输出数据,在发送之前主机将压缩数据,复位之后压缩数据将被发送到外围设备,BIT6将反馈IRQJ脚的状态。有些设备不仅仅把IRQ用做反映并行口的状态,还用于诊断冲突(见表6)。

BIT5到BIT3提供了端口IRQ分配的状态,同样BIT2到BIT0提供了DMA通道状态。我们可以读/写前面提及的BIT位,但对于跳线的并行卡,只能读它的状态。

3 并行口ECP模式与外设通信实例

计算机实现对AT89C51单片机的控制,单片机上传一组数据给计算机处理。单片机与计算机的所有对接端口需加10K上拉电阻(见图1、图2、图3)。

计算机C语言:

#define ECPAddr 0x0378

#define ECPState 0x0379

#define ECPContr0x037A

#define DataFIFO0x0778

#define ConfigRegB 0x0779

#define ECR0x077A

#include

/******************************** 下传3452 *********************************/

outp (ECR, 0x60);

outp (ECPContr, 0x04);//进入1284传输模式

outp(DataFIFO,3); outp(DataFIFO,4);outp(DataFIFO,5);outp(DataFIFO,2);m= inp(ECR)&0x01;

while(m==0x00)//如果数据未完全移出循环等待

{

m= inp(ECR)&0x01;Outtime++;

if( Outtime>1024)

{

state = 0x10;//“通信失败”显示

break;

}

}

Outtime=0;

outp (ECPContr, 0x3c);//退出1284传输模式

/********************************** End*********************************/

/*************************** 接收100个数据*****************************/

outp (ECR, 0x60);

outp (ECPContr, 0x21);//0x21

for(i=0;i<=99;i++)

{

m= inp(ECR)&0x01;

while(m==0x01)//如果数据为空循环等待

{

m= inp(ECR)&0x01;

Outtime++;

if( Outtime>1024)

{

i=100;//退出本次100个读数

break;

}

}

y[i]=inp (DataFIFO)/10.0-3.5;

}//数据完全读入后,nreverse Request并未置高

outp (ECPContr, 0x0c);//退出1284传输模式并口17脚此时为低电平

/*********************************End ********************************/

上述程序片段是本人利用LabWindows软件制作的,经过实际测试,这里为限制篇幅而略去了一些变量的定义、控制。

单片机C语言:

sbit HostCLK=P2^0;sbit PeriphReq = P2^2;sbit PeriphCLK=P2^5;sbit HostACK=P2^1;

sbit PeriphACK=P2^6;sbit nReverReq=P2^3; sbit nACKRever = P2^7;sbit ACT1284=P2^4;

while(ACT1284&&nReverReq;==0)//主机未下传指令之前等待

{ }

PeriphACK=1;//外设应答置高停止接收数据

PeriphACK=0;//外设应答置低准备接收数据计算机只有查询到此信号为低电平才将数据移入总线。

for(j=0;j<=3;j++)

{

while(HostCLK)

{}

PeriphACK = 1;

while(HostCLK==0)

{}

DATA[j]=P0;//HostCLK上升沿将数据移入单片机

PeriphACK = 0;//外设应答置低结束一个读周期

}

While (nReverReq)//主机没有上传数据请求循环等待

{ }

if((DATA[0]==3)&&(DATA[1]==4)&&(DATA[2]==5)&&(DATA[3]==2))

{

nACKRever=0;//响应主机上传数据的请求

PeriphACK=1;//通知主机送出的是数据防止主机误操作移出数据

for(j=0;j<=99;j++)

{

P0=j;

PeriphCLKC=0;//通知主机总线上的数据是有效数据

while(HostACK==0)//主机未响应有效数数据前循环等待

{ }

PeriphCLKC=1;//正沿将数据移入主机

while(HostACK)//主机未响应已读入数据之前循环等待

{ }

}

}

上述程序段因篇幅所限略去了一些变量的定义、赋值。

计算机的并行口ECP模式传输速率最高可达2Mbyt/s,可实现实时通信。它成本低,在短距离数据传输及控制中是非常理想的通信方式。在办公、工业控制中得到广泛的应用。

[参考文献]

[1] http://www.beyondlogic.org/spp/parallel.pdf

[2] Http://www.deyondlogic.org/ecp/ecp.htm

[3] LabWindows/CVI8 Help