面向神经形态系统的忆阻逻辑电路综述与展望①

2023-01-18王佳阳董哲康纪晓悦胡小方周广东齐冬莲1

王佳阳, 董哲康, 纪晓悦, 胡小方, 周广东, 齐冬莲1,,5

1.杭州电子科技大学 电子信息学院, 杭州 310018; 2.浙江大学 电气工程学院, 杭州 310027; 3.浙江省装备电子重点实验室, 杭州 310018; 4.西南大学 人工智能学院, 重庆 400715; 5.海南浙江大学研究院, 海南 三亚 572025

目前大部分现代智能计算系统都是基于冯诺依曼架构[1]设计的, 在该结构中数据的处理和存储是分离的, 伴随着巨大的能量消耗[2-4]. 近年来, 随着科学技术的不断发展与进步, 受脑启发的神经形态系统[5]这一新型信息处理系统的出现为解决冯诺依曼瓶颈提供了很大的可能性. 神经形态系统具有高度的并行计算能力、 极低的功耗并且能够实现存算一体, 已经逐渐成为了人工智能领域[6]的研究热点之一[7-9]. 其中, 逻辑电路是神经形态计算硬件实现的基本计算单元, 对于构建新型神经形态系统具有重要的意义.

目前实现逻辑电路的方法可以分为三类[10-13], 即基于传统元器件实现的逻辑电路、 基于集成芯片实现的逻辑电路以及基于忆阻器实现的逻辑电路. 基于传统互补金属氧化物半导体(Complementary Metal-Oxide-Semiconductor Transistor, CMOS)[14]技术和集成芯片构建的逻辑电路在连续扩展、 电路面积、 功率消耗等方面面临着严峻的挑战[15-17]. 具有纳米尺寸、 电阻可变且非易失、 耗能低等特性的忆阻器, 为构建逻辑电路提供了新的思路. 忆阻器[18]这一新型电路元器件的概念于1971年由蔡少棠教授首次提出, 该器件表示了电荷量和磁通量之间的关系. 2008年, 惠普实验室首次验证了实物忆阻器的存在, 并指出其是一个纳米级无源的二端电路元器件, 忆阻器的成功制备引起了全球范围内研究者们的广泛关注[19]. 随着忆阻器研究的不断深入, 忆阻逻辑电路为传统集成电路技术的发展提供了新的思路和解决方案, 逐渐成为了构建面向神经形态系统中逻辑电路的一个热点研究方向[20-22].

本文的主要结构和框架如下: 在第1部分整理和分析了忆阻逻辑电路中常用的忆阻器模型; 在第2部分对近年来的忆阻逻辑电路进行了详细的梳理和分析, 并根据输入、 输出逻辑状态变量的不同, 将其分为三类, 并对这三类电路的特性进行了对比和分析; 在第3部分, 本文介绍了忆阻逻辑电路在神经形态系统中的应用现状; 针对忆阻逻辑电路在操作复杂性和物理实现方面的缺陷, 在第4部分展望了忆阻逻辑电路的发展方向; 最后, 本文对忆阻逻辑电路及其在神经形态系统中的应用进行总结. 需要说明的是, 本文全面综述了面向神经形态系统的忆阻逻辑电路, 旨在总结当前的发展趋势和未来的发展前景, 希望进一步促进忆阻器在目前建立的逻辑电路架构以及人工智能领域神经形态系统中的应用.

1 忆阻器模型

忆阻器具有非易失性、 纳米尺寸、 低功耗、 与传统CMOS技术可兼容、 阻值变换快速等特性, 已经广泛应用在面向神经形态系统的逻辑电路中. 目前, 该领域一直致力于寻找新的材料和技术制备不同结构、 不同物理机制的忆阻器件. 与此同时, 大量的工作已经投入到忆阻器数学模型的研究中. 一个准确、 通用、 简洁的忆阻器数学模型能够重现忆阻器所具备的复杂动力学特性, 对于后续的应用研究至关重要. 目前, 众多不同类型的忆阻器模型被构建[23-35], 例如不同材料的忆阻器、 惠普忆阻器、 阈值开关忆阻器、 电压阈值自适应忆阻器、 扩散型忆阻器、 单极性忆阻器等等.

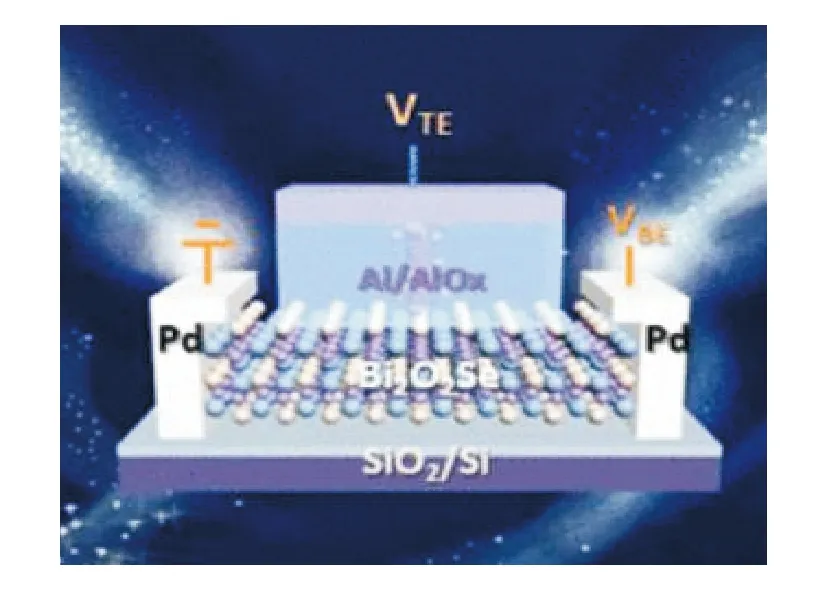

忆阻器通常由金属-绝缘体-金属(metal-insulator-metal, MIM)结构制成, 大多新型材料具有环境稳定性、 合适的能带结构和高导电性, 故新型材料制备的忆阻器在逻辑电路的构建中具有很高的应用潜力. Pt/W/Ta2O5/Pt/Ti/SiO2/Si[23], Au/Pt/TiO2/Pt/Ti/Au/Pt/TiO2/Pt/Ti[24], Pd/Bi2O2Se/Pd[25], Pt/ZnO/Pt[26], Ta/TaOx/Pt[27], Pt/Ta/Ta2O5/Pt/Ti[28], Pt/HfO2/TiN[29], Pt/Ta2O5/W/Pt[30]等材料制备的忆阻器都已在忆阻逻辑电路中验证了模型的合理性, 图1展示了新型材料Pd/Bi2O2Se/Pd制备的忆阻器示意图.

图1 新型材料Pd/Bi2O2Se/Pd制备的忆阻器模型

虽然由新型材料制备的忆阻器具有独特的物理和电子特性, 但是忆阻器的成功制备存在一定的技术壁垒, 且基于忆阻器构建的逻辑电路对忆阻器的一致性和稳定性要求较高, 构建具有实物忆阻器电气特性的忆阻器数学模型至关重要.

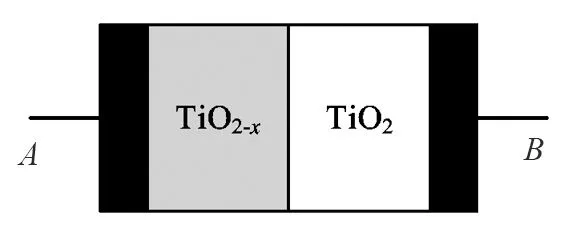

2008年, 惠普实验室提出了一个Pt/TiO2/Pt结构的忆阻器模型[19](图2). 该模型将两层纳米级的二氧化钛薄膜夹在两个铂片电极之间, 其中一层TiO2薄膜没有氧空位, 另一层薄膜中为缺失氧原子的TiO2-x层(掺杂层), 忆阻器的阻值是这两层薄膜阻值的总和. 由于通过薄膜的电荷量和电荷方向的不同, 掺杂层的氧空位会发生离子迁移, 两层薄膜的厚度会发生变化, 从而改变忆阻器的电阻状态. 定义忆阻器的高阻态阻值和低阻态阻值分别为Roff和Ron; 定义未掺杂薄膜端为忆阻器的正极, 掺杂层薄膜端为负极. 当在忆阻器的正极施加高电平时, 忆阻值减少, 反之, 忆阻值增加. 当离子线性迁移时, 模型的阻值M(x)定义为:

图2 Pt/TiO2/Pt忆阻器模型

M(x)=Ron·x+Roff·(1-x)

(1)

(2)

(3)

其中:D为忆阻结构中两层薄膜的总厚度,w为掺杂层的厚度,x为掺杂层在两层薄膜中的占比,μv为内部离子漂移的平均速度,i为通过该忆阻器的电流.

在纳米级器件中, 极小的电压就可以产生巨大的电场, 并在离子迁移过程中出现显著的非线性特征. 离子的非线性漂移在两层薄膜的边界处特别明显, 迁移速度逐渐减少至零. 考虑到状态变量x的值应该限制在区间[0,D]中, 为了模拟非线性离子迁移现象, 在线性离子迁移模型的基础上引入特殊的窗函数f(x)可以得到对应的忆阻器非线性离子迁移模型. 相较于线性离子迁移模型, 该模型除状态变量x的变化趋势发生改变(见式(4)), 其余状态方程均相同.

(4)

文献[31]基于量子力学遂穿现象, 提出了耦合欧姆-隧穿忆阻器模型, 也称阈值开关模型 (Threshold Switch Model). 该模型的等效电路如图3所示, 图中的R表示欧姆阻值,Rt表示忆阻值,L表示隧道势垒的宽度. 该忆阻器模型的阻值定义为:

图3 耦合欧姆—隧穿忆阻器模型

(5)

(6)

其中:L表示隧道势垒的宽度;f0,κ为该模型的拟合参数;r表示一个与电压有关的参数.

阈值自适应模型[32](threshold adaptive memristor, TEAM)是一种基于电流阈值的忆阻器模型, 即忆阻器的阻值是否变化取决于流经忆阻器的实时电流值与电流阈值之间的关系. 然而, 在大部分基于忆阻器的逻辑电路设计中, 基于电压阈值的忆阻器模型应用更广泛. 基于此, 文献[33]引入电压阈值自适应模型(voltage threshold adaptive memristor, VTEAM), 该模型允许通过调整模型的参数来模拟各种忆阻器的行为. 该模型中的忆阻器阻值定义为

(7)

式中:Roff和Ron分别为忆阻值的极大和极小值,xoff和xon分别为忆阻器内部状态变量x的上下边界值.

VTEAM模型区别于HP忆阻模型的一个显著特性是具有阈值特性, 忆阻器的阻值切换速度更快. 当施加于忆阻器两端的电压为正负阈值之间的数值, 忆阻值不发生变化. 而施加的电压超过正电压阈值, 忆阻值增加. 相反, 若施加的电压低于负电压阈值, 忆阻值减少. 该模型结构简单、 具有阈值特性、 准确度高, 还有一定的通用性, 为忆阻逻辑电路的设计提供了新的思路.

对于非易失性忆阻器, 在不施加偏置电压时, 可以保持在原来的阻值状态. 然而, 在去除偏置电压时, 若此前易失性忆阻器处于低阻值状态, 其会在纳秒到毫秒的时间内自发地从低阻值状态回到高阻值状态. 数字型易失性忆阻器(扩散型忆阻器)是构建逻辑电路的理想选择, 不但具有很高的开关比, 可以在低至纳秒的时间内完成电阻切换, 还具有良好的可扩展性, 基于扩散型忆阻器进行内存中计算的可能性已经被证明[34]. 但数字型易失性忆阻器需要一个电源来存储信息, 故其构建的逻辑电路会比基于非易失性忆阻器构建的电路复杂.

双极性忆阻器具有阻值快速切换特性与阈值特性, 为其实现忆阻逻辑电路提供了天然的条件. 目前, 大量基于忆阻器的逻辑电路设计方案采用双极性忆阻器模拟不同的逻辑功能[19,23-34]. 不同于基于双极性忆阻器的逻辑电路, 单极性忆阻器有着很高的开关比和极高的集成度, 并且该忆阻器仅仅与施加的电压大小有关, 只需要一个极性的电压[35], 能够有效降低外围电路的复杂度. 另外, 单极性忆阻器更容易并入存储器阵列中, 进而实现功能复杂的逻辑电路.

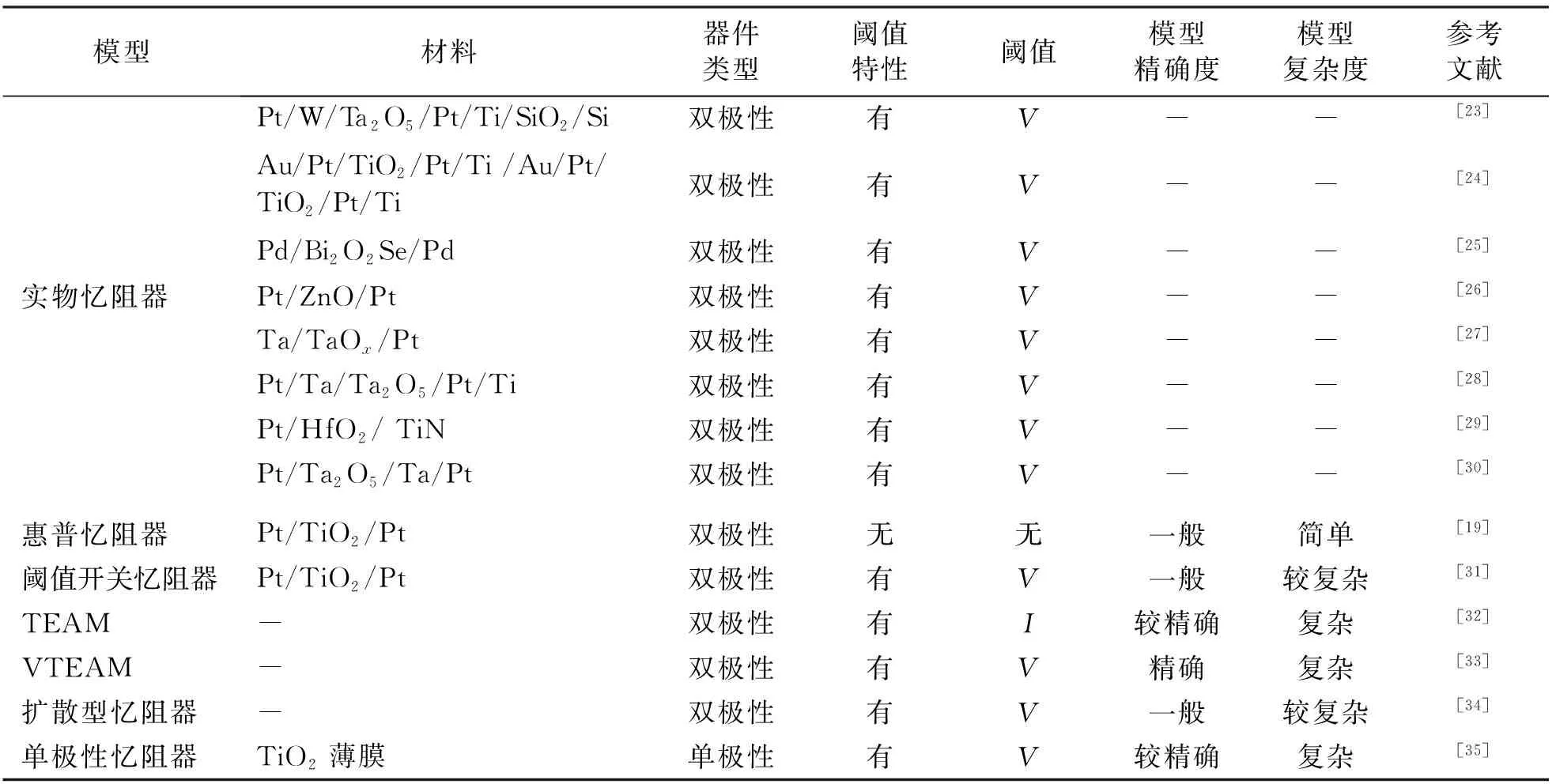

针对以上介绍的忆阻器模型进行整理和分析, 并将得到的结果整理于表1:

表1 忆阻器模型汇总

从表1可以发现基于Pt/TiO2/Pt材料构建的惠普忆阻器模型简单, 然而其没有阈值特性, 阻值的状态易受到外界的干扰, 抗干扰能力较弱. 但是, 惠普忆阻器实现阻值的转换对施加电压的大小没有太高的要求, 故其在忆阻器/CMOS混合构建的逻辑电路中应用广泛. 表1中应用于数字逻辑电路的忆阻器模型多为双极性, 与单极性忆阻器相比, 电阻的开关能发生在较低的电压条件下. 根据表1, 可以看出大多数忆阻器模型都具有阈值特性, 且将电压作为阈值的忆阻器模型占大多数, 值得注意的是, 表中提及的TEAM模型为电流阈值模型. 忆阻器具有的阈值特性能够保证忆阻器具有良好的开关特性, 这是其能否在数字逻辑电路中得到较好应用的关键特性. 此外, TEAM模型和VTEAM模型相对精确度较高, 也被广泛应用于实现忆阻逻辑电路.

2 忆阻逻辑电路与特性分析

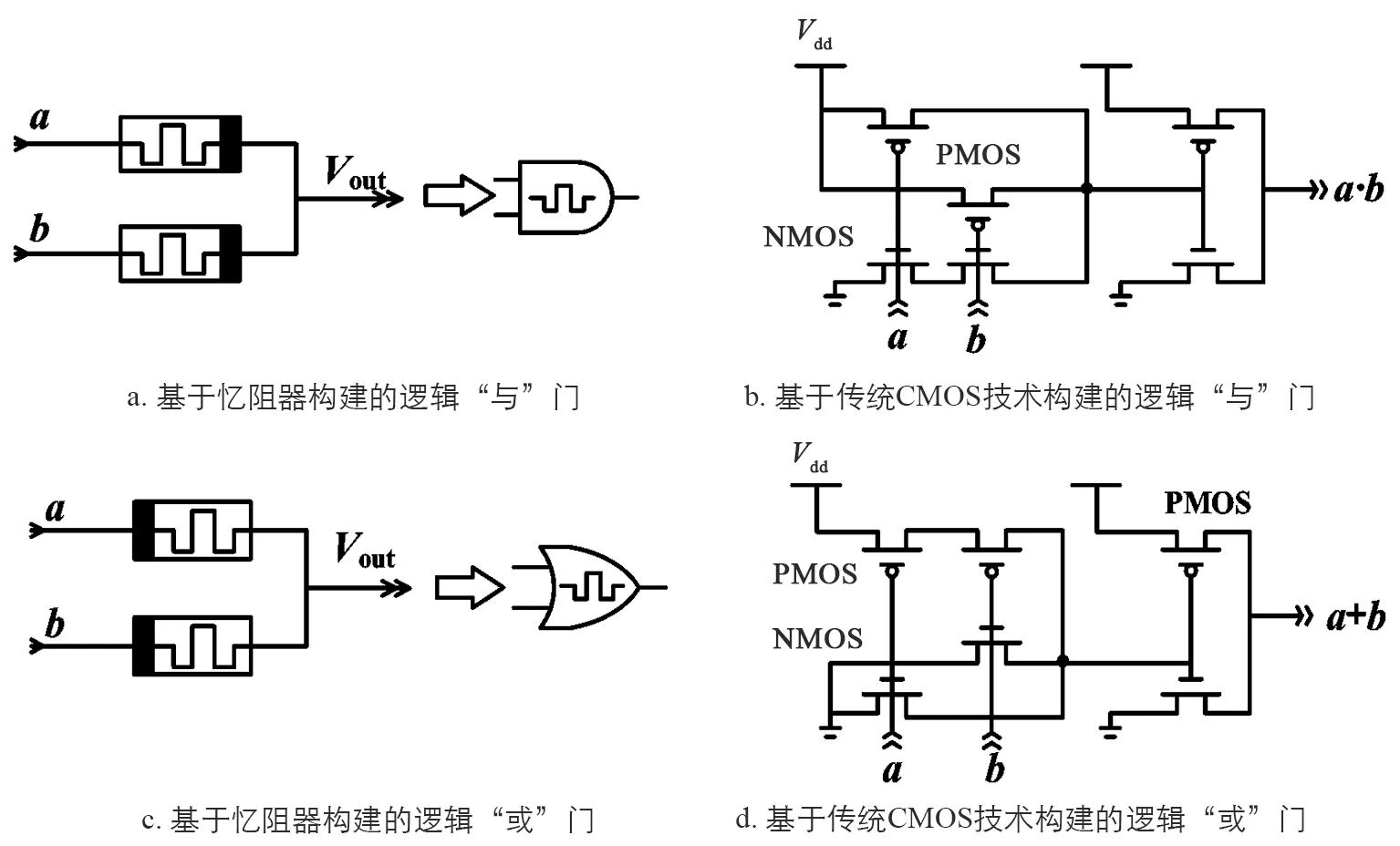

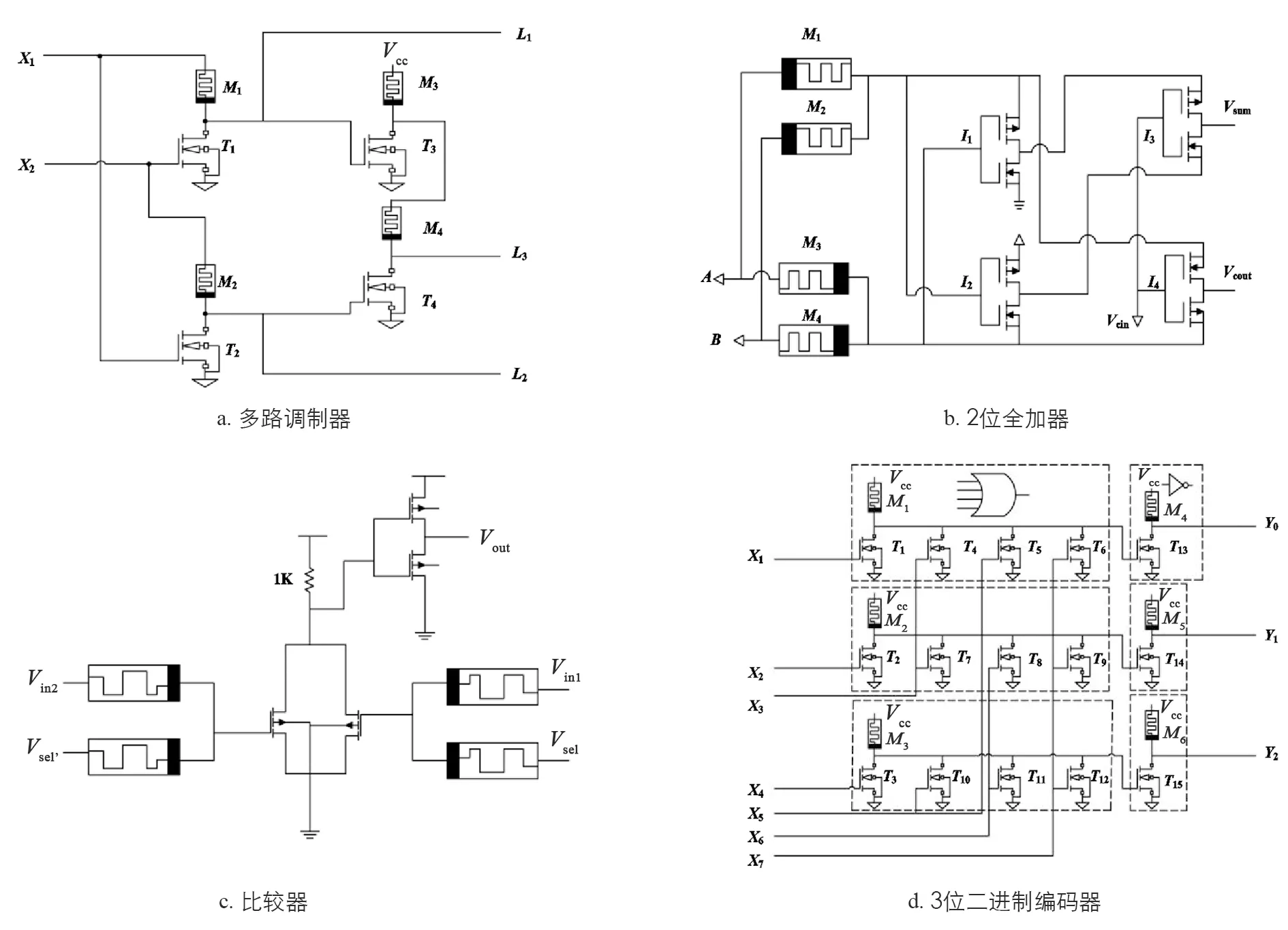

忆阻器凭借良好的开关特性被广泛应用于逻辑电路. 基于忆阻器的逻辑电路不仅能够实现布尔逻辑、 实质蕴涵逻辑, 还能实现携带信息量更多、 运算效率更高的三值逻辑电路. 基于忆阻器的逻辑电路与传统的逻辑电路内部的逻辑状态变量存在着明显的差异. 在由晶体管、 集成芯片构建的传统逻辑电路中, 电压是唯一逻辑状态变量. 输入端口接入电压信号, 并在整个信号处理过程以电压形式进行逻辑运算, 最后输出也为电压形式. 而忆阻逻辑电路内部的逻辑状态变量除了具有传统逻辑电路电压形式外还有两种不同的表现形式: 一种是电阻作为输入、 中间运算和输出结果中的唯一状态变量; 另一种是电压和电阻都作为状态变量引入电路的运算.

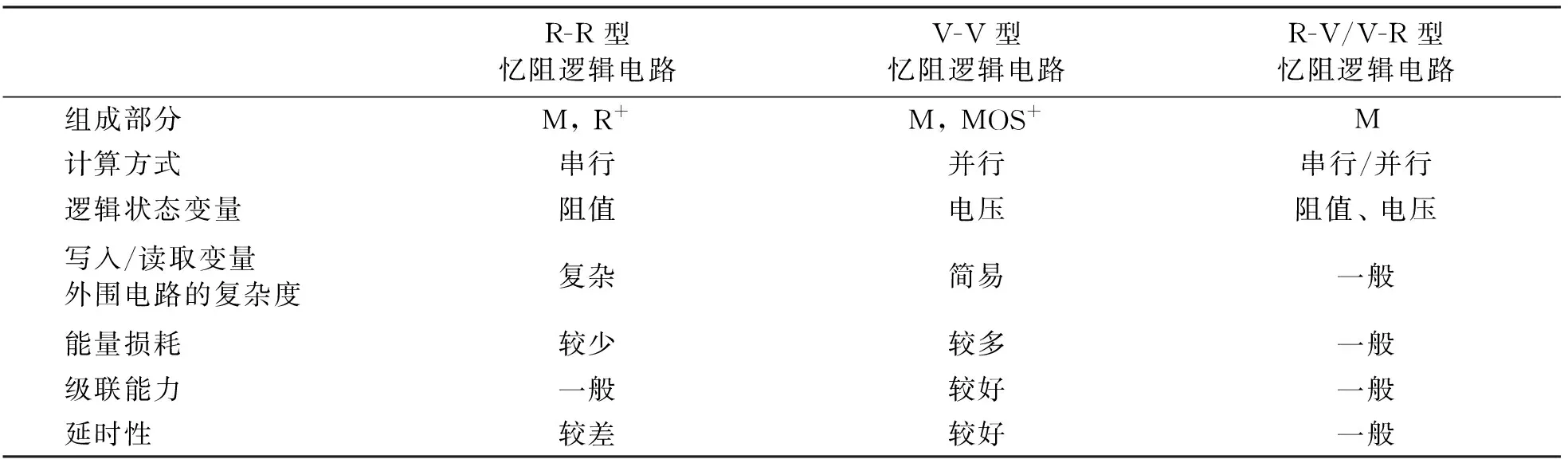

基于以上分析, 本文将忆阻逻辑电路大致分为三类: 第一类逻辑电路中的输入、 输出状态变量均为阻值, 定义其为R-R忆阻逻辑电路; 第二类逻辑电路中的输入、 输出状态变量均为电压, 定义其为V-V忆阻逻辑电路; 第三类电路中的输入、 输出状态变量为阻值和电压的组合, 定义其为V与R组合状态变量忆阻逻辑电路. 在此分析这三类忆阻逻辑电路的特性, 为后续其在神经形态系统中的应用提供良好的参考.

2.1 忆阻逻辑电路

2.1.1 R-R型忆阻逻辑电路

R-R型忆阻逻辑电路是指使用忆阻值替代传统逻辑电路中的电平信号来进行逻辑计算的一类电路. 1910年, 《数学原理》一书提出了4种基本的逻辑运算[36]. 其中的“与”“或”“非”运算被广泛地应用于计算机系统和集成电路, 这3个基本运算操作能够形成一个完整的集合. 还有一个被命名为“实质蕴涵(Material implication, IMP)”的运算操作, 由p和q两个变量构成, 逻辑函数pIMPq(p→q)的数学物理含义为“如果p, 那么q”, 用数字逻辑中的表达式如下:

(8)

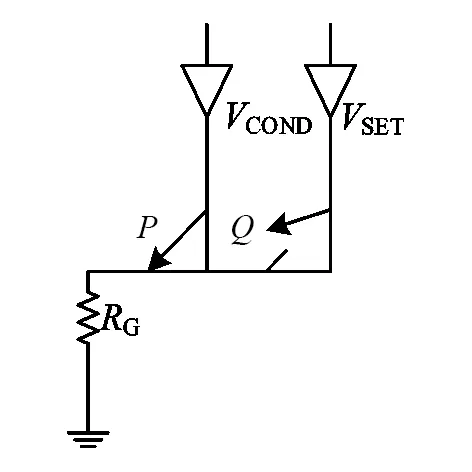

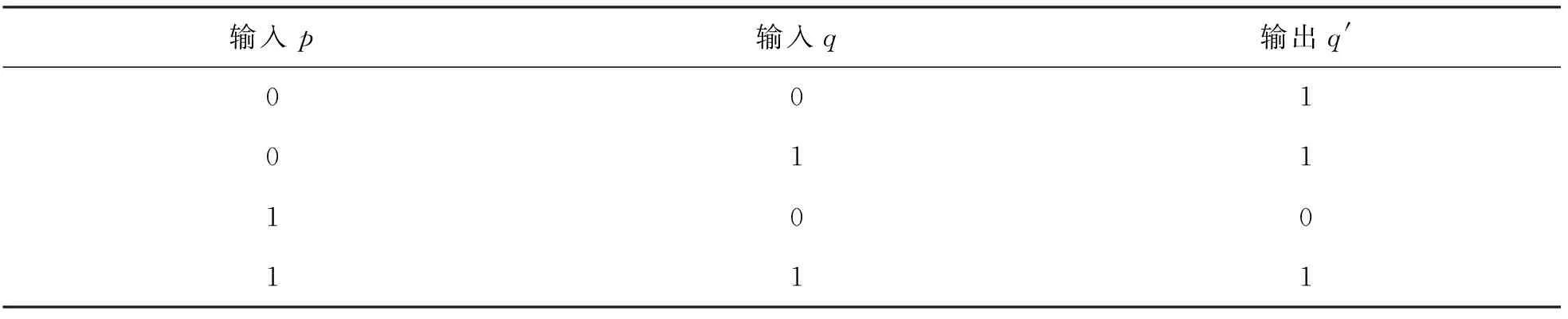

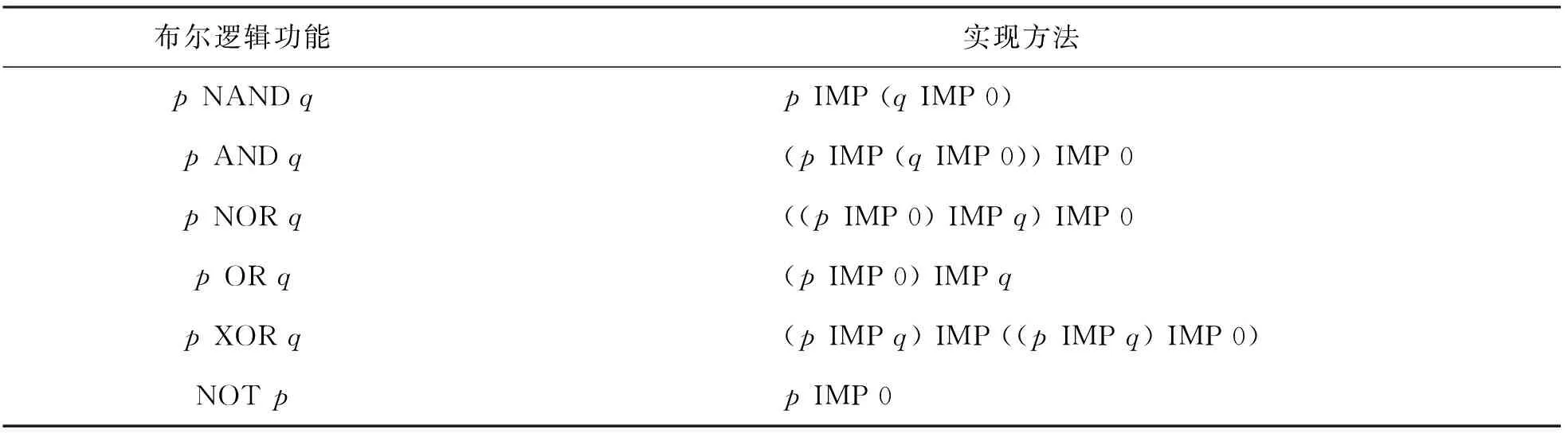

惠普实验室提出了基于忆阻器实现实质蕴涵逻辑的电路(IMPLY), 该电路的输入、 输出逻辑状态变量均为忆阻值. 实质蕴涵逻辑操作(IMP)可以由两个忆阻器和一个电阻器构建的简单电路实现, 并运用提出的IMP操作和FALSE逻辑[37]操作(总是输出逻辑“0”)构建了一个二输入的“与非”门. 图4为IMP操作的电路图, 由两个参数完全相同的忆阻器P和Q与一个接地负载电阻器RG串联构建, 表2为其对应的真值表. 基于该IMP和FALSE操作, 能够实现不同的布尔逻辑, 具体的实现方法列于表3.

图4 实现IMP实质蕴涵逻辑的电路示意图

表2 p IMP q →q′对应的逻辑真值表

表3 基于IMP操作和FALSE操作的不同布尔逻辑实现方法

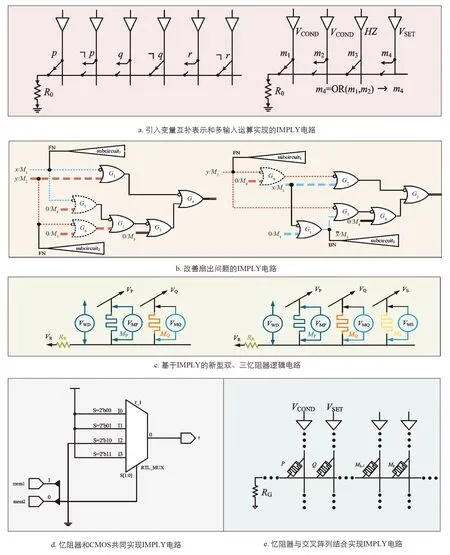

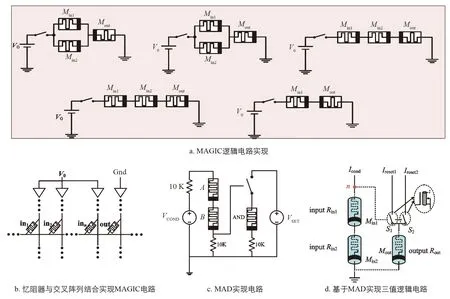

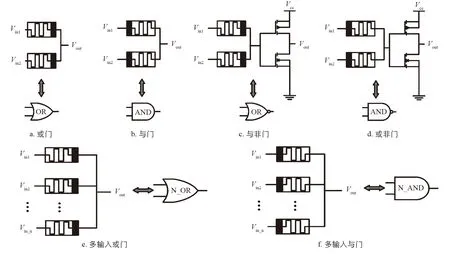

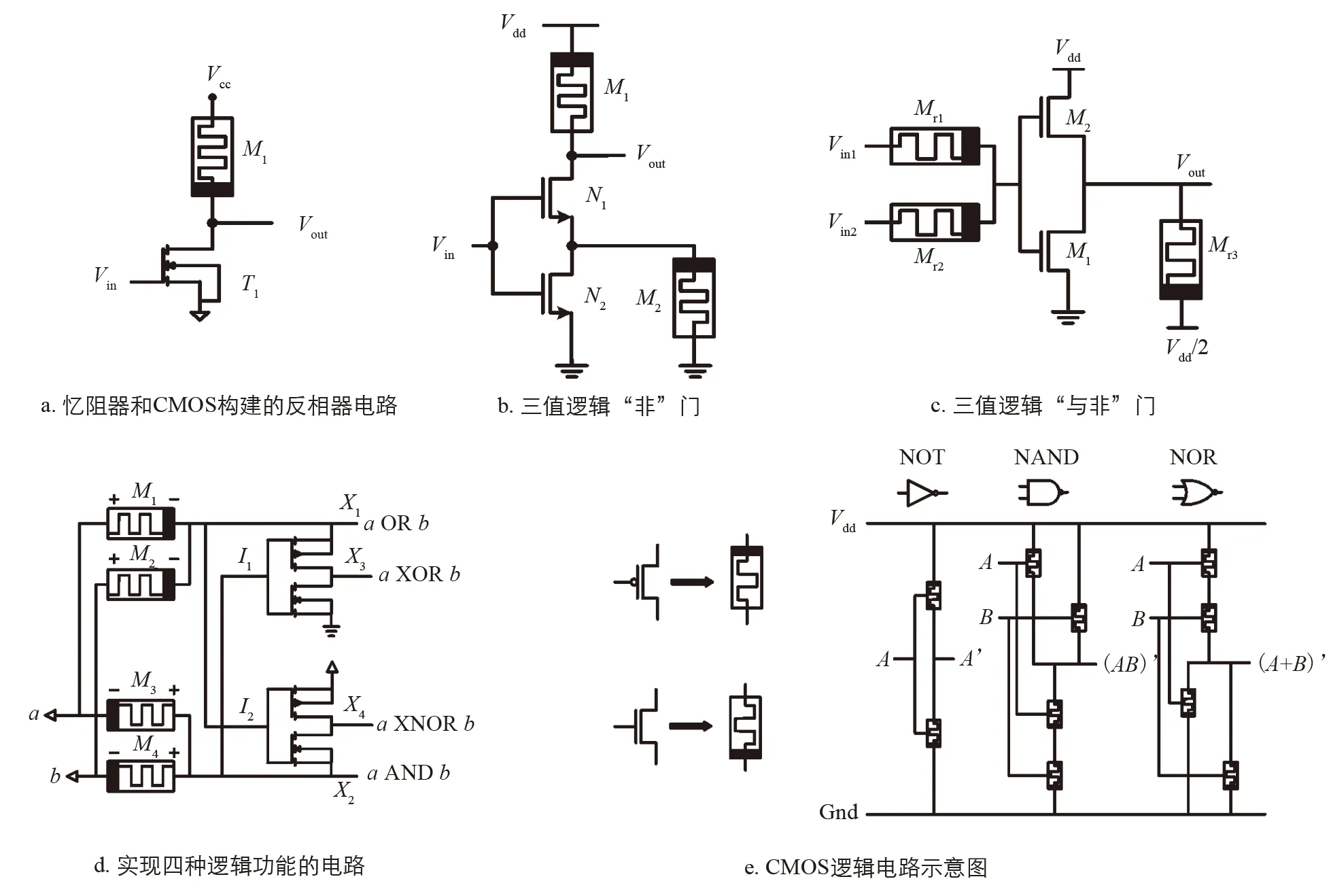

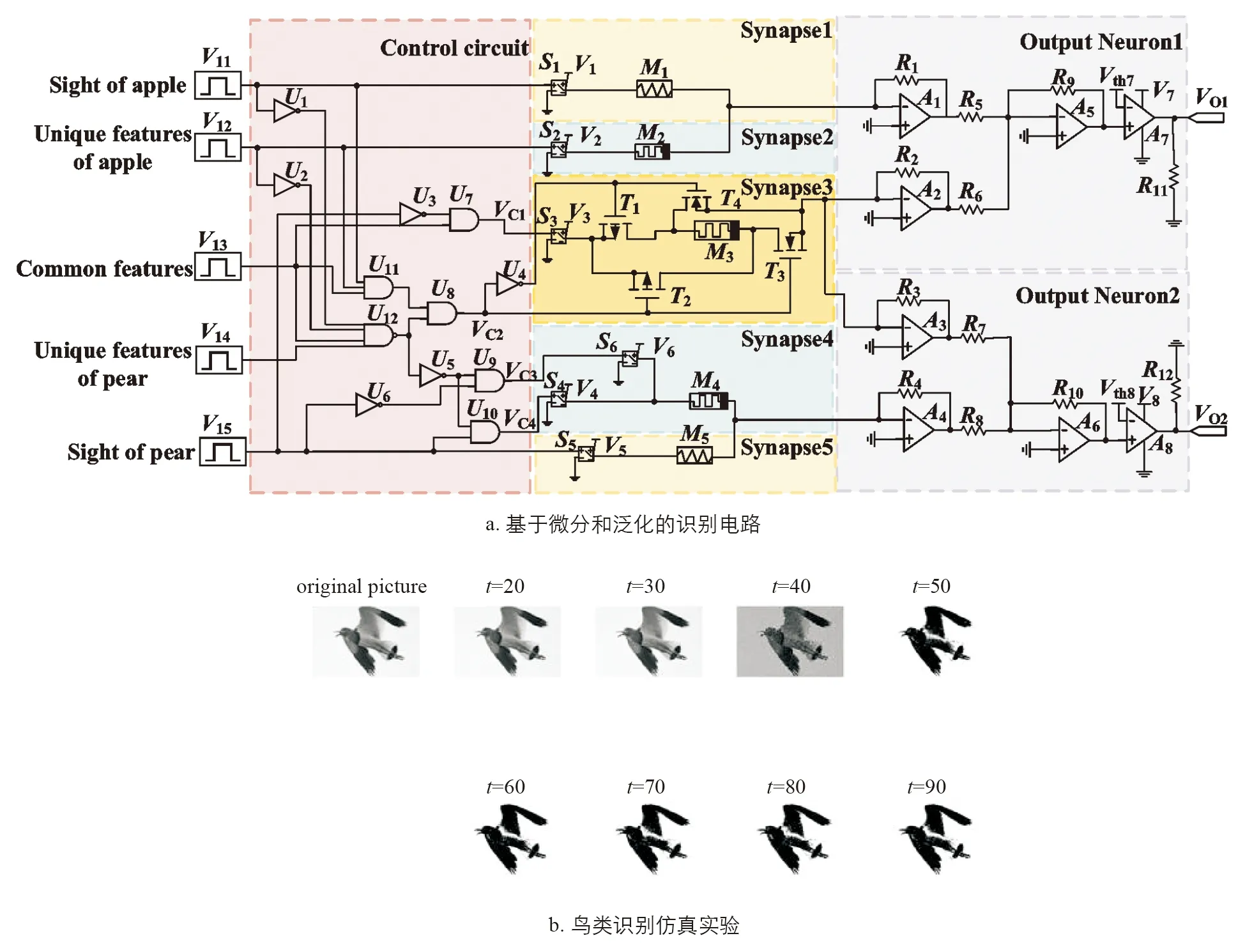

IMP逻辑操作的实现思路: 对两个忆阻器施加不同的电压, 其中施加于P上的电压为VCOND, 施加于Q上的电压为VSET, 限定两个电压均为负电压, 且满足|VP|<|VQ|. 定义忆阻器的极小值Ron(极大值Roff)对应电路中状态变量的逻辑“1”(逻辑“0”), 并规定电阻器的阻值满足不等式Ron IMPLY电路在忆阻逻辑电路中应用广泛, 但基于IMPLY构建的电路存在一个主要缺陷, 即其需要冗长的周期序列以执行不同的逻辑运算. 从性能的角度分析, 电路延时过长. 多次IMP逻辑操作还可能导致错误累积从而影响逻辑运算的准确性. 针对IMPLY电路的进一步研究和改进工作大多在文献[38]提出的电路基础上进行. 文献[39]提出了引入变量的互补表示和多输入运算实现IMP逻辑的新方法, 构建的电路如图5a所示. 变量的互补表示策略中每个输入和输出变量需要两个忆阻器, 一个存储变量的值, 另一个存储其反向值. 多输入运算时应考虑所使用忆阻器的极大值和极小值的比率足够大, 以区分多个并行非导电器件和单个导电器件. 如果输入被用于并行执行多个布尔操作, 每个逻辑门的操作行为将互相影响, 导致结果不准确. 文献[40]为解决该问题, 提出了一种综合算法, 并设计了新的没有扇出问题的逻辑异或门和同或门, 如图5b所示. 图5 基于忆阻器实现的IMPLY电路及其改进电路 文献[27]基于IMPLY电路, 提出了一种新的逻辑电路实现方法, 并构建了双忆阻器逻辑电路和三忆阻器逻辑电路, 如图5c所示. 该电路与IMPLY电路最大的区别为电阻器RG不再接地, 并且在实现不同逻辑函数时, 需要施加特定的电压在忆阻器和电阻器上. 文献[41]中提出了一种忆阻器和CMOS技术兼容实现IMPLY电路的方法, 该电路的输入为两个忆阻器P和Q的阻值状态, 而输出的阻值状态可以认为是忆阻器Q的最终阻值状态, 使得阻值能够作为输出传递到下一级电路, 构建的电路如图5d所示. IMPLY电路与交叉阵列兼容, 故很多研究将IMPLY电路集成于交叉阵列中, 如图5e所示, 在工作忆阻器所在的位线上施加特定的电压VSET和VCOND, 在子线上串联一个接地的电阻器RG. 文献[42]基于IMPLY电路, 提出了一个新的基于忆阻器的逻辑电路——忆阻器辅助逻辑(Memristor Aided loGIC, MAGIC), 该电路中输入、 输出逻辑状态变量均为忆阻值, 定义忆阻器的极小值Ron(极大值Roff)对应电路中状态变量的逻辑“1”(逻辑“0”). 在MAGIC中, 不需要电阻器这一元器件进行分压操作, 整个电路仅由忆阻器实现. 此外, MAGIC电路中使用不同的忆阻器作为输入和输出, 输出被写入一个专用的忆阻器, 将输入和输出逻辑状态变量进行分离, 保护输入变量不被破坏. 该方法构建的电路还具有结构简单的特点, 只需要在开关上施加一个特定的电压就能实现对应的逻辑功能. 基于MAGIC电路构建的基本逻辑门如图6a所示, 输入忆阻器Min1和Min2的初始阻值状态作为逻辑电路的输入, 需要事先对忆阻器进行初始化操作, 将这两个输入忆阻器与输出忆阻器Mout串联连接, 施加特定的电压后Mout切换阻值状态. 具体地, MAGIC电路的实现分为连续的两个阶段. 首先将输出忆阻器的阻值状态初始化为特定值, 进一步, 对逻辑电路施加电压V0. 输出忆阻器Mout上的电压取决于输入和输出忆阻器的逻辑状态. 简而言之, 输入忆阻器和输出忆阻器构成一个分压器. 当施加在忆阻器两端的电压大于其阈值电压, 输出忆阻器的逻辑状态能够改变. 相反, 若电压低于阈值电压, 输出忆阻器的阻值将保持在初始状态. MAGIC电路结构简单, 只需要一个控制电压, 不需要额外的电阻器, 输入和输出状态存储在不同的忆阻器中, 且运算过程高效稳定, 能够重复操作. 故基于MAGIC的逻辑电路通用性较强, 目前在该方面的研究很广泛. 文献[43]将忆阻器的阻值分为高阻、 中阻、 低阻3个阻值状态, 表示逻辑“0”“1”“2”, 基于MAGIC电路设计实现了三值逻辑门电路. MAGIC电路也能够与交叉阵列兼容, 在输入忆阻器所在列施加特定电压, 输出忆阻器所在列接地, 电路示意图如图6b所示, 使用此设计方法在忆阻逻辑电路中应用广泛. 图6 基于忆阻器实现的MAGIC电路及其改进电路 文献[44]基于IMPLY电路, 提出了一个新型逻辑门——忆阻器驱动门(memristors-as-drivers gate, MAD Gate). 该电路通过感应输入忆阻器的值, 并将其作为输出忆阻器的驱动器, 该电路实现的简单逻辑门例如“与”“或”“非”“与非”“或非”“异或”门等都只有一个逻辑操作的延时, 并且最多只需要3个忆阻器. 以逻辑“与”门为例, 电路图如图6c所示. 忆阻器A和B的忆阻值作为输入逻辑状态变量, 输出逻辑状态变量为与开关相连的忆阻器的阻值, 定义忆阻器的极小值Ron(极大值Roff)对应电路中状态变量的逻辑“1”(逻辑“0”). 为保证输入忆阻器在传感阶段的阻值不发生变化, 选取比忆阻器的正阈值电压小的VCOND. 同时为了确保输出忆阻器的忆阻值能够发生改变, 选取比忆阻器的负阈值电压小的VSET. 若忆阻器A和B的阻值都对应逻辑“0”或者任意一个输入忆阻器的阻值对应逻辑“0”, 控制开关闭合端的电压近似于0, 不足以启动开关, 故输出忆阻器保持其原始状态“0”. 而若A和B均处于低阻值状态, 将会开启与输出忆阻器相连的开关, 输出忆阻器的阻值在VSET的影响下减小, 逻辑状态转变为逻辑“1”. 文献[45]基于MAD设计了一个基于忆阻器的三值逻辑门电路, 电路示意图如图6d所示, 开关S1和S2的开闭由端点n的电压决定, 两个电流Ireset1和Ireset2被选通并流经输出忆阻器改变其阻值状态, 忆阻器的高阻、 中阻、 低阻分别表示逻辑“0”“1”“2”, 实现了忆阻逻辑电路的多值运算. 2.1.2 V-V型忆阻逻辑电路 基于忆阻器构建的逻辑电路中的输入、 输出逻辑状态变量除了可以是电阻, 也可以为电压, 并将输入输出变量均为电平信号的电路称为V-V型忆阻逻辑电路. 文献[46]中提出逻辑运算可以通过将忆阻器与CMOS技术集成的方法来实现, 提出了一种基于忆阻器/CMOS混合结构的逻辑电路实现方法, 并将其命名为忆阻器比例逻辑(memristor ratioed logic, MRL). 在这种逻辑电路中, 逻辑运算中的“与”和“或”功能可以通过忆阻器实现, 逻辑运算中的“非”门电路和信号放大功能由CMOS技术构建的反相器实现. 基于MRL结构实现的基本逻辑电路示意图如图7所示. 图7 基于MRL结构实现的基本逻辑电路 不同于IMPLY电路实现的二值逻辑, MRL电路中的输入输出逻辑状态变量始终为电压信号, 高电平(低电平)对应电路状态变量的逻辑“1”(逻辑“0”). 将施加在两个忆阻器上的电压Vin1和Vin2作为该逻辑电路的输入变量, 输出则为两个忆阻器相连端口的电压Vout. 逻辑“或”门和逻辑“与”门电路拓扑相同, 均可由两个极性相反的忆阻器串联构建, 如图7a和图7b所示. 若在两个逻辑门电路施加相同的输入信号(高电平或低电平), 输入端口不存在电压降, 两个忆阻器之间没有电流通过, 那么输出电压与输入电压相同. 然而, 若施加的两个输入信号电平相反(一个高电平一个低电平), 电路中就会存在压降, 相应地, 电流将会从高电平一端流向低电平一端, 同时忆阻器的阻值状态将会在电流的作用下发生改变, 进而影响输出电压Vout的值. 在逻辑“或”门和“与”门的输出端连接一个CMOS反相器, 即可实现逻辑“或非”门和“与非”门, 如图7c和图7d所示. 基于二输入逻辑“或”门和“与”门的电路结构, 构建了多输入“或”门和“与”门, 如图7e和图7f所示. 在大多基于MRL构建的电路中, 使用CMOS反相器实现逻辑“非”门, 而文献[47]中使用一个忆阻器和一个CMOS晶体管混合的结构改进了逻辑“非”门, 如图8a所示, 在一定程度上减少了电路的面积. 文献[48]通过两个忆阻器和一个CMOS反相器构建了一个三值逻辑“非”门, 如图8b所示. 文献[49-50]基于MRL设计了一个三值逻辑电路, 将作为状态变量的电平信号分为三档, 分别代表逻辑“0”“1”“2”. 其中“与”“或”门的构建与MRL相同, “非”“与非”“与或”门的构建都在输出端口串联了一个忆阻器, 并且在忆阻器的输入端施加一半的电源电压, 实现的逻辑“与非”门的电路图如图8c所示. 在MRL中, 不同的电路拓扑结构实现了不同的逻辑函数功能, 整个运算过程不需要额外的初始化操作, 电路的输出结果与忆阻器的初始状态无关, 通用性更好. 例如文献[51]提出了一个新的忆阻器/CMOS逻辑电路, 可以在同一个电路中实现逻辑“与”“或”“异或”“同或”4种逻辑运算, 如图8d所示. 图8 基于忆阻器的MRL改进电路 基于MRL设计的逻辑电路中, 逻辑“非”门的实现方式大多还需要一个CMOS反相器, 故基于该方法构建的逻辑电路相较于纯忆阻器构建的逻辑电路, 功耗和面积都更大. 在计算输出电压过程中, 尽管满足不等式Roff≫Ron, 仍存在少量的电压衰减. 但是通过对电路的不断级联, 会导致电压衰减现象更加明显, 最终影响逻辑电路的准确性. 文献[31]提出了一个基于忆阻器的类CMOS电路, 该电路的输入、 输出逻辑状态变量均为电压, 也属于V-V型忆阻逻辑电路. 该电路中使用正向极化忆阻器代替N型晶体管, 用反向极化忆阻器代替P型晶体管. 相应地, 正向极化忆阻器的初始阻值为Ron, 反向极化忆阻器的初始逻辑状态为Roff. 若在正向极化忆阻器两端施加正电压, 阻值状态将不会发生改变, 若施加的电压为负电压, 阻值将会从Ron增大至Roff. 若在反向极化忆阻器两端施加正电压, 阻值状态将不会发生改变, 而若施加的电压为负电压, 阻值将从Roff减少至Ron. 基于该电路构建的逻辑“非”“与非”“或非”门电路如图8e所示. 图中忆阻器显示为三端器件, 以方便其与CMOS器件比较. 该电路的输入输出逻辑状态变量均为电压, 定义输入信号为正电压时, 对应逻辑“1”, 输入信号为负电压时, 对应逻辑“0”, 定义输出电压近似于电源电压Vdd时, 对应逻辑“1”, 近似于接地电压Gnd时, 对应逻辑“0”. 以实现的逻辑“非”门为例, 在输入正电压时, 两个忆阻器都将维持其原先的阻值状态, 即反向极化忆阻器为高阻值状态, 正向极化忆阻器为低阻值状态. 根据电路分压原理, 输出的电压近似为0V, 对应逻辑“0”. 相反地, 若施加的电压为负电压, 两个忆阻器的阻值状态都发生了翻转, 即反向极化忆阻器的阻值状态转变为低阻值状态, 正向极化忆阻器的阻值状态转变为高阻值状态, 输出的电压近似表示为电源电压, 对应逻辑“1”. 2.1.3 V-R/R-V型忆阻逻辑电路 在V-R型忆阻逻辑电路中, 将电压信号作为逻辑输入进行逻辑计算, 而计算得到的结果由忆阻器后继的阻值状态作为逻辑输出. R-V型忆阻逻辑电路是将忆阻器的阻值状态作为逻辑输入, 电路的输出电压与参考值进行比较, 得到逻辑输出结果. 由于输入输出逻辑状态不统一, 在写入和读出相应变量时, 需要采用不同的方法, 在一定程度上增加了设计电路的复杂性, 因此逻辑电路中输入输出状态变量为不同变量的电路较少. Akers逻辑阵列[52]是由实现相同逻辑功能的单元互连而成, 每个逻辑单元的输出被传输到下方和右侧的数组, 控制对所有的行输入高电平(逻辑“1”), 对所有的列输入低电平(逻辑“0”), 电路如图9a所示. 各个单元实现的逻辑函数为 (9) 文献[53]提出了一个基于互补忆阻器结构的Akers逻辑阵列, 该电路由两个反向串联的互补忆阻器(两个忆阻器的阻值状态相反)组成(图9b). 该电路的输入逻辑状态变量为忆阻器的阻值, 定义忆阻器的极小值Ron(极大值Roff)对应电路中状态变量的逻辑“1”(逻辑“0”), 在x,y两端施加特定的电压后, 输出为两个忆阻器相连公共端口的电压Vf, 定义高电平(低电平)对应逻辑“1”(逻辑“0”), 该电路属于R-V型忆阻逻辑电路. 如果忆阻器MZ为高阻值状态, 则与MZ相连的电路导通, 施加在y上的电压作为电路的输出. 若MZ为低阻值状态, 与MZ相连的电路断开, 而与互补忆阻器相连的电路导通, 施加在x上的电压作为电路的输出, 两个忆阻器相连的公共端口电压表示为 (10) 进一步, 设计了一个逻辑“异或”门, 该门电路由8个忆阻器构建, 并对每行的最左边列施加高电平, 并将每列最上方一行接地, 电路如图9c所示. 电路的实现分为两个阶段: 首先要对电路中的忆阻器进行初始化操作, 即写入需要输入的逻辑状态变量; 紧接着, 通过施加一个低电平执行相应的布尔逻辑函数. 需要说明的是, 这里使用的低电压需要确保阵列中的忆阻器阻值状态不会发生改变. 图9 Akers逻辑阵列及实现方法 文献[54]提出了一个由忆阻器和开关构建的逻辑电路, 可以通过不同的开关操作实现基本的“与”“或”“非”“与非”“或非”门, 电路图如图10所示. 在一个电路中就能实现多个逻辑操作, 大大节省了电路的面积和功耗, 并且提出的电路不需要进行初始化操作, 减少电路的执行时间. 该电路的输入逻辑状态变量为电压, 定义信号的高电平(低电平)对应电路状态变量的逻辑“1”(逻辑“0”). 输出逻辑状态变量为忆阻值, 定义忆阻器的极小值Ron(极大值Roff)对应电路中状态变量的逻辑“1”(逻辑“0”), 属于V-R型忆阻逻辑电路类型. 以逻辑“与”门为例做详细介绍, 上面部分的4个忆阻器为调控忆阻器, 下面的两个忆阻器为负载电阻, 逻辑“与”门通过将忆阻器M1,M2,Ms2与电压相连端的开关闭合, 其余忆阻器相连的开关断开, 定义忆阻器M1和M2的阻值分别为R1和R2,Ms2的阻值远大于R1和R2, 那么3个忆阻器相连的公共端的电压为: (11) 若V1和V2均为高电平(低电平), 公共端电压Vs近似等于高电平(低电平), 产生的电流从Ms2的正极流向负极(负极流向正极), 其忆阻值减少(增加), 故输出的状态变量对应逻辑“1”(逻辑“0”). 若V1为高电平,V2为低电平,M2阻值减少, 公共端电压Vs近似等于低电平, 输出逻辑“0”. 类似地, 若V1为低电平,V2为高电平, 输出“0”. 针对以上的3类忆阻逻辑电路, 本文从组成部分、 计算方式、 逻辑状态变量、 写入/读取变量外围电路的复杂度、 能量损耗、 级联能力、 延时性7个方面开展对比和分析, 并将结果整理于表4中. 表4 忆阻逻辑电路性能对比 1) R-R 型忆阻逻辑电路 输入输出状态变量均由忆阻值表示, 有助于构建结构简单的忆阻存内计算系统. 实现二值逻辑时, 该类型逻辑电路中忆阻器的极大值和极小值分别表示逻辑“0”和逻辑“1”. 实现三值逻辑时, 该类型逻辑电路一般是将忆阻器的阻值分为3档, 分别对应逻辑“0”“1”“2”或者逻辑“-1”“0”“1”. 该类型的忆阻逻辑电路组成部分简单, 极大地缩减了电路的规模, 减少了电路的功耗. 然而, R-R型忆阻逻辑电路的计算方式为串行, 需要设定冗长的时间序列, 极大地增加了逻辑计算的时间成本, 延时性较差. 同时, 该类型电路需要较复杂的外围电路, 进行写入/读取变量的操作. 2)V-V型忆阻逻辑电路 电压表示输入输出的逻辑状态变量, 与已经成熟的CMOS技术兼容, 对驱动电路的要求较低. 实现二值逻辑时, 逻辑“0”和逻辑“1”分别由低电平和高电平表示. 实现三值逻辑时, 一般采用3个不同的电压, 分别对应逻辑“0”“1”“2”或者逻辑“-1”“0”“1”. 该类型的忆阻逻辑电路, 通过直接给操作电压分配逻辑意义, 消除了R-R型忆阻逻辑电路中将逻辑输入信号写入忆阻器的过程, 不需再设计外围电路进行写入状态变量的操作. 由于该类型电路的输出逻辑状态变量由电压表示, 级联性相较于状态变量中有阻值的电路更好, 能够并行地执行逻辑计算. 但输出电压是易失性的, 需要额外的存储单元来存储逻辑输出. 除此之外, 该类型的电路较难应用于忆阻器的交叉阵列中, 存在一定的局限性. 3) R-V/V-R型忆阻逻辑电路 输入输出状态变量为忆阻值和电压的组合, R-V型忆阻逻辑由电阻输入和电压输出构成, 而V-R型忆阻逻辑电路中的输入状态变量为电压, 输出状态变量则为忆阻值. 实现二值、 三值逻辑功能, 该类型电路所表示的逻辑值与以上讨论的两类逻辑电路相同. R-V型忆阻逻辑电路同V-V型忆阻逻辑电路的输出逻辑状态变量相同, 是易失性的, 需要设计能够实现存储功能的外围电路. R-V/V-R型组合型逻辑电路的输入/输出为忆阻值, 需要设计相应的外围电路执行写入/读取变量操作. 这一类型的电路在逻辑迭代计算过程中, 每个计算的电阻(电压)输出都必须转换为下一次计算的电压(电阻)输入, 级联能力一般, 需要设计外围电路实现变量的转换, 极大地增加了运行时间和功耗, 延时性一般. 忆阻器不仅可以作为计算元件, 还可以作为R-R型、 V-R型忆阻逻辑电路中的存储元件, 它们都是非易失性逻辑, 为开辟非冯诺依曼架构开辟了一条新的路径. 基于内存存储的非易失性布尔逻辑门是构成内存计算体系结构的基本和关键块. 对于指定的逻辑操作, R-R型忆阻逻辑电路通常比V-V型、 V-R型和R-V型3种忆阻逻辑电路需要更多的外接设备. 采用相同逻辑配置的R-R型忆阻逻辑电路所实现的操作通常是有限的, 并且施加在忆阻器上的电压需要特定的时间序列, 存在过于冗长的情况. 除此之外, 逻辑状态变量中含有阻值的忆阻逻辑电路在变量的写入或是读取过程中, 需要外围电路对变量进行阻值和电压的转换, 此过程在增加了电路面积的同时增大了电路的能量损耗. 可重构逻辑能够通过改变相同电路拓扑所应用的操作信号来执行各种逻辑功能, 提供了高灵活性和内在并行性, 这对于执行复杂的计算任务至关重要. R-R型和V-R型忆阻逻辑电路具有较低的可重构性, 级联性一般, 通常需要额外的电路进行级联, 电路的复杂性会在一定程度上提高. 虽然V-V型忆阻逻辑电路的某些电路需要晶体管元器件, 电路面积较大的同时损耗也会有所提升. 但该类型的忆阻逻辑电路不需要外设的电路进行逻辑状态的读取和写入工作, 并且该电路的输出为电压, 与现有成熟的CMOS技术兼容, 级联性能较好, 该类型的电路应用较广阔. 神经形态计算系统中的逻辑运算至关重要, 不同的逻辑功能(包含“与”“或”“非”等基本逻辑门电路和累加器、 比较器等复杂逻辑功能电路)可以用忆阻逻辑电路进行替换, 进一步减少该计算系统的尺寸和能源消耗. 基于文献[55], 神经形态系统中传统二输入逻辑“与”门和“或”门的构建需要6个CMOS器件, 如图11b和图11d所示. 而基于忆阻器构建的逻辑电路, 只需要两个忆阻器即能实现二输入逻辑“与”门和逻辑“或”门, 如图11a和图11c所示. 虽然构建一个逻辑门的传统元器件和忆阻器数量相差不大, 但神经形态系统是一个复杂的脑启发并行计算系统, 内部含有不计其数的计算单元. 相比之下, 基于忆阻器构建的逻辑电路使用的元器件的数量明显小于传统方式构建的逻辑电路中使用的器件数, 在尺寸和能源消耗上具有很大的优势. 图11 基于忆阻器和CMOS技术构建的逻辑“与”“或”门对比 基于忆阻器的逻辑电路具有小面积、 低功耗、 存算一体、 运算速度快等特性, 不仅能够实现基本的布尔逻辑、 三值逻辑运算电路, 还能够实现加法器、 乘法器、 编码器、 译码器、 幅度比较器、 多路调制器、 线性反馈移位寄存器、 触发器等不同功能的电路[23,43,56-66], 在数字逻辑电路中得到了广泛的应用(图12). 图12 忆阻逻辑电路在数字逻辑领域中的不同应用 神经形态系统需要并行处理和分析不同计算单元中的数据, 其中逻辑运算模块是一个基本且关键的组成部分, 而忆阻逻辑电路为构建一个运算速度更快、 效率更高、 面积更小的神经形态系统提供了很大的可能性. 下面介绍了忆阻逻辑电路在联想记忆、 情感计算、 模式识别3个方面的潜在应用. 联想记忆[67]是神经形态认知系统的一个重要分支, 也是人类大脑所特有的功能, 通常通过一个感觉信号或两个及以上感觉信号与一个行为操作的关联来实现. 巴甫洛夫条件反射[68]是生物联想记忆中最具代表性的学习类型, 设计并实现巴甫洛夫联想记忆成为了人工智能领域内的研究热点, 对研究类脑神经网络具有重要的意义. 近年来, 有很多工作致力于将忆阻逻辑电路应用于巴甫洛夫联想记忆电路中. 文献[69]设计了一种带有时滞学习的巴甫洛夫联想记忆神经网络电路, 实现了学习、 遗忘、 快速学习、 慢遗忘、 时滞学习等功能. 文献[70]提出了一种基于二阶条件反射的巴甫洛夫联想记忆电路. 该回路可以在初始学习后对条件刺激作出反应, 并实现两种遗忘功能. 此外, 该回路可以通过条件刺激间接建立条件反射, 而不是直接建立非条件刺激的条件反射. 文献[71]提出了一种基于忆阻器的全功能巴甫洛夫联想记忆电路, 如图13a所示. 设计的巴甫洛夫联想记忆电路为三输入一输出电路, 输入信号分别表示肉、 正常铃声和低响度铃声, 输出信号为狗是否分泌唾液, 输入和输出的状态变量均为电压, 其中电压信号的高电平和低电平分别对应逻辑“1”和“0”, 实现了联想记忆中的两类学习过程和3类遗忘过程. 图13 忆阻逻辑电路在联想记忆和情感计算中的应用 文献[72]提出情感计算的目的是通过赋予计算机识别、 理解、 表达和适应人的情感的能力来建立和谐人机环境, 并使计算机具有更高的、 全面的智能. 情感计算与巴甫洛夫联想记忆有着相似的生理属性定义, 对构建神经形态系统具有重要的意义. 许多研究人员已经使用忆阻逻辑电路来实现情绪记忆的模型构建, 实现了对人类情感的简单模拟, 能够实现快乐和悲伤这两种情绪. 另外, 随着研究的发展, 根据信息输入的状态来判断情绪输出的状态, 实现了情感关联学习、 情感形成和情感表达等功能. 文献[73]提出了一种新的基于忆阻器的神经网络情绪模型及其电路实现, 该模型中有3个输入和2个输出, 联想学习和3种遗忘过程共同构成了全功能情绪模型, 设计的情感记忆电路可以调节学习速率, 为实现人工智能机器人提供了一个新的思路. 文献[74]提出了一种学习速率可变的情绪模型, 如图13b所示, 该模型考虑了3种遗忘方式: 只应用无条件刺激, 只应用中性刺激, 无条件刺激和中性刺激都不用. 文献[75]基于忆阻器仿真实现了情绪与记忆一致性的神经网络电路. 不同于传统的记忆或情绪单一的神经网络, 该电路由记忆模块、 情绪模块和联想神经元模块组成(图13c), 具有学习、 遗忘、 快速学习、 缓慢遗忘、 精神疲劳、 情绪抑制、 情绪一致性记忆等功能. 忆阻逻辑电路在模式识别[76]和模式分类[77]领域也有应用, 文献[78]提出了一个由4个晶体管和1个忆阻器构成的阻值双向调节电路, 而后结合忆阻逻辑电路对其进行扩展, 构建了苹果的识别和特征召回电路. 文献[79]在传统联想记忆的基础上加入泛化和微分理论, 提出了基于微分和泛化的简单分类和识别电路, 如图14a所示. 该电路将对象的特征作为输入, 将电路的输出作为分类结果, 实现苹果和梨的分类和识别的功能. 文献[80]提出了一种双模忆阻器桥接突触电路, 并利用该电路构建多层神经网络, 结合细胞神经网络实现机场灰度鸟类图像的边缘提取, 实验结果如图14b所示. 图14 忆阻逻辑电路在模式识别和分类领域中的应用 忆阻器因其良好的开关特性, 为探索新的逻辑运算范式开辟了一条新的道路, 并为传统的CMOS电路提供了一个很有前景的替代方案. 并且, 忆阻器具有非易失特性, 即使撤去两端的电压, 其阻值也不会发生改变, 实现了存算一体, 为构建新的非冯诺依曼架构提供了极大的可能. 然而, 目前提出的忆阻逻辑电路在操作复杂性和物理实现方面都存在一些限制, 亟需得到进一步的改进. 1) 如何保证忆阻逻辑电路中模型的一致性和稳定性. 在基于忆阻器设计的逻辑电路中, 对于纳米级元器件忆阻器的一致性要求极高, 其参数的微小变化都可能造成较大的计算偏差. 使用校验方法或者冗余设计的方式可以在一定程度上容忍离散性带来的误差, 但会带来额外的能耗和延时, 削弱基于忆阻器的存内计算的先天优势. 其次, 逻辑计算的精确度也与忆阻器件的稳定性有联系, 若在调整电路中的忆阻器阻值后, 其阻值发生偏移, 对于三值逻辑电路, 其输出结果可能不准确. 由于应用于实际电路中的计算量很大, 需要大规模高密度的忆阻逻辑电路, 然而减少忆阻存储单元上的面积可能会导致一致性降低, 这意味着减小面积不是最有效的方法. 2) 如何解决忆阻逻辑电路时间序列冗长问题. 基于忆阻器的逻辑电路因其非易失性, 在进行逻辑运算操作时, 要求在逻辑运算之前不断地对忆阻器进行初始化操作, 从而容易引起时间序列冗长的问题. 若要将忆阻逻辑电路应用于神经形态系统, 需要大数量的忆阻器, 这意味着若每一步骤前都需要初始化, 这将会是一个相当繁琐的过程. 故如何减少或彻底消除初始化操作是改进忆阻逻辑电路的一个重要环节, 也是未来需要研究的一个重要方向. 引入自学习系统, 使得忆阻器能够实时调整自己的状态, 不再需要初始化操作, 或许是未来的一个研究方向; 同时, 研究特定的忆阻值写入和读取机制, 也能有效解决时间序列冗长的问题. 3) 如何解决多忆阻逻辑电路的级联问题. 目前构建的忆阻逻辑电路大多存在着难以级联的问题. 在一个复杂的系统中, 存在着不计其数的计算单元, 各个单元之间都有些许的联系, 若不能解决级联问题, 忆阻逻辑电路的发展将会受到很大的限制. 特别地, 对于输出逻辑状态为阻值的电路, 若在一个电路的输出后级联多个电路, 将会产生扇出问题, 进而导致错误结果的输出. 而对于V-V型逻辑电路, 尽管忆阻器能与传统CMOS元器件兼容, 两者之间的自然差异依然存在. 在执行级联操作时, 由于在负载容量方面的不足, 在不加放大电路的情况下易产生信号退化问题. 如何改进设计已有的逻辑电路, 使得其能够更好地级联, 进而广泛应用于神经形态系统, 也是未来我们研究的一个有力着手点. 4) 如何解决交叉阵列结构的忆阻逻辑电路中漏电流问题. 应用于神经形态系统的忆阻逻辑电路多与交叉阵列相结合, 能够在一定程度上减少电路的面积. 但交叉阵列存在一个很大的缺陷, 即存在漏电流. 目前存在增大忆阻器阻值, 反串联忆阻器, 将忆阻器与二极管、 三极管、 开关结合构成存储单元等减少漏电流的方法, 但这些方法增加了交叉阵列的读写操作步骤, 如何在减少漏电流的同时简化读写操作是未来工作一个很好的切入点. 5) 如何实现可重构、 多值忆阻逻辑电路. 一个计算系统中一般不仅仅是进行单一的逻辑操作, 往往需要根据不同的需要, 进行灵活的改变以实现逻辑功能. 故基于忆阻器的可重构逻辑电路将会是未来计算系统的一个发展趋势, 我们可以加大对该方面的研究, 改进并设计出通用的拥有完整逻辑集的电路. 目前, 忆阻逻辑电路领域的大多数研究都以二值逻辑为实现目标, 二值忆阻逻辑电路已经趋向于成熟. 然而, 基于忆阻器实现三值逻辑电路的研究相对较少, 三值逻辑相对二值逻辑携带了更多的信息量, 并且实现三值逻辑的电路运算速度更快、 面积和体积更小且功耗更低. 对三值逻辑的进一步研究, 为未来探索多值逻辑和模糊逻辑提供了可能. 6) 如何建立忆阻逻辑电路与神经形态系统的融合机制. 基于忆阻器构建的逻辑计算系统和脑启发并行神经形态计算系统都是很有前途的内存计算体系结构, 目前将忆阻逻辑电路与神经形态系统相结合的研究相对较少, 大多是用忆阻逻辑电路构建的逻辑门代替神经形态系统中的传统逻辑门或是在联想记忆方面的一些应用, 在实现信息检索、 图像识别、 语音识别等方面的应用仍面临着挑战. 因对计算速度和智能信息处理的进一步要求, 迫切需要开发一种具有高效二进制逻辑和神经形态计算功能的集成计算体系结构. 未来的主要工作可以是将忆阻逻辑电路应用于神经形态系统, 设计一些模拟人类大脑的紧凑电路. 忆阻器具有非易失性、 纳米尺寸、 低功耗、 与传统CMOS技术兼容、 阻值变换快等特性, 其在逻辑电路中的应用在尺寸和能源消耗方面具备一定的优势, 为探索新的计算范式和架构提供了全新的思路. 逻辑电路是神经形态计算硬件实现的基本计算单元, 故忆阻逻辑电路对于构建新型神经形态系统具有重要的意义. 本综述首先介绍了当前在忆阻逻辑电路中广泛应用的忆阻器模型. 紧接着, 介绍了近年来流行的忆阻逻辑电路, 并根据电路的输入输出逻辑状态变量的不同, 将忆阻逻辑电路分为R-R型、 V-V型、 R-V/V-R型忆阻逻辑电路3类. 从这3类电路的组成部分、 计算方式、 逻辑状态变量、 写入/读取变量外围电路的复杂度、 能量损耗、 级联能力、 延时性7个方面, 进一步讨论了各类忆阻逻辑电路的优缺点. 其中, 电路的组成部分和延时性是衡量逻辑电路质量的重要指标, 电路的延时性能取决于操作脉冲的数量, 而电路的组成部分中忆阻器的数量和晶体管的数量决定了电路的尺寸和能耗. 由于V-V型忆阻逻辑电路的输入输出状态变量都为电压, 在进行写入和读取变量操作时不需要再设计额外的电路. 该类型的电路对驱动电路的要求最低, 不需要设定冗长的时间序列, 并且其与已经成熟的CMOS技术兼容, 级联性相较于状态变量中有阻值的电路更好, 故目前该类型的电路的应用最广泛. 本文讨论了忆阻逻辑电路在联想记忆、 情感计算、 模式识别3个神经形态系统领域中的潜在应用. 忆阻逻辑电路可以替代神经形态系统中的传统逻辑电路, 能够在一定程度上减少电路的面积与功耗, 具有广阔的发展前景. 最后, 针对忆阻逻辑电路在操作复杂性和物理实现方面的缺陷, 本文总结并展望了忆阻逻辑电路及其应用于神经形态系统的发展方向.

2.2 忆阻逻辑电路性能对比分析

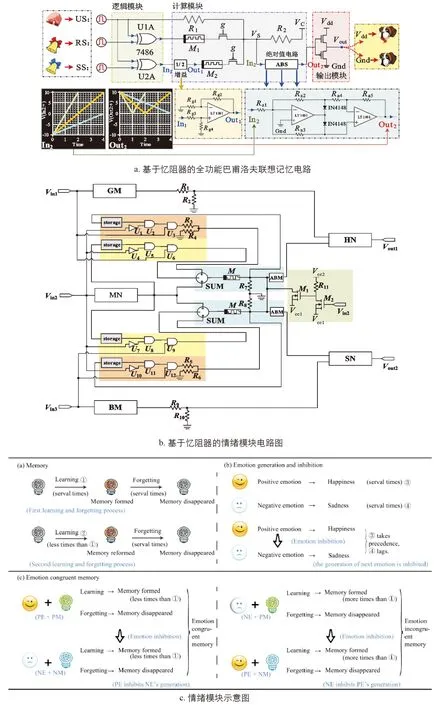

3 忆阻逻辑电路在神经形态系统中的应用

4 展望

5 结论