基于FPD-Link Ⅲ的机载高速视频信号切换与补偿研究

2023-01-07杨伟樱刘月

兰 天,杨伟樱,刘月

(陕西工业职业技术学院 陕西 咸阳 712000)

0 引言

随着航空技术的不断发展,各型飞机凭借自身不受地形地貌限制的优势在国防、民航等各领域大放异彩。为了保证飞机飞行的安全,飞行员需要实时观察各类型视频信号保证飞行安全。与此同时视频信号朝着传输速率更快、分辨率更高、线路更少的方向迭代。因此能同时在不同显示器上显示相同的视频画面,并且能实时切换各路视频通路,提供高质量的视频画面,为多人同时协同工作提供了工作平台,且完成了数据显示的通道备份,安全系数增高[1]。

传统实现视频切换的方式主要是基于CPLD/FPGA 的实现方式[2-3],该方式需要对输入视频信号先解码为RGB 并行信号,完成切换操作后再对该RGB 信号进行重新编码。该步骤需要挂载多片缓存芯片,当输入、输出视频通路较多时,对应的编解码芯片与缓存芯片个数都需增加,功耗大大提高,且FPGA 芯片管脚有限,当视频路数较多时容易达到挂载上限,制约功能扩展。

机载系统中常用的视频格式包括:XGA、DVI、HDMI、LVDS 与ARINC 818 等视频信号。XGA 作为模拟信号,视频质量较差,传输速率较慢,并且机上环境恶劣,容易受到干扰[4];DVI、HDMI、LVDS 作为数字差分信号[5-6],具有较好的抗干扰能力与显示效果,当含有多路视频时,上述数字差分信号均存在数据线过多、连接器与航插定义不够等问题。ARINC 818 作为新一代航空数字视频总线[7],具有传输速率高、抗干扰能力强等优势,但其作为光信号,传输需要光纤介质,传统电缆无法满足其传输要求,另外须在视频发送端与屏幕显示端增加光电器件对光信号进行电-光/光-电转换,增加现场可编程门阵列(FPGA)对视频信号进行ARINC 818 协议的编解码操作,速率越高,开销越大。

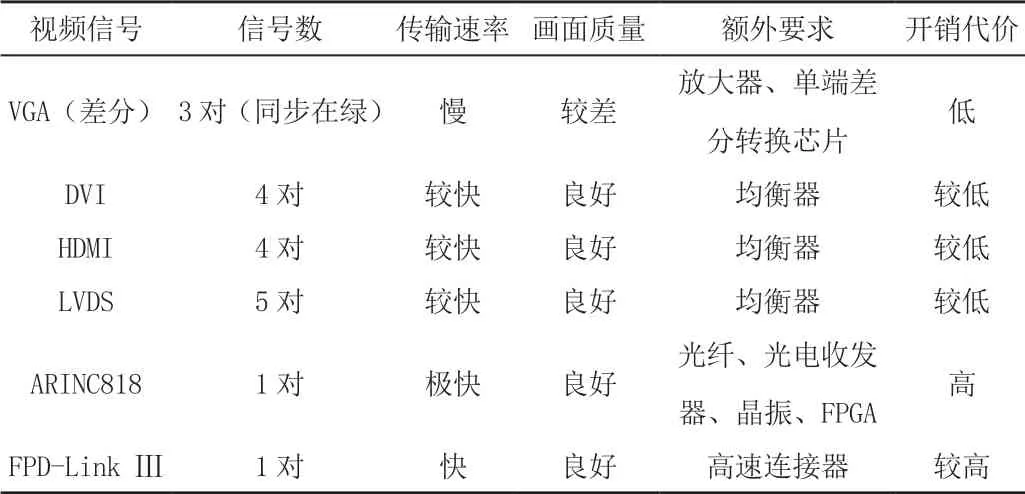

FPD-Link(Flat Panel Display Link)[8]是在1996年提出的一种高速数字视频接口标准。LVDS 作为第一代的FPD-Link 信号,相较于RGB 并行信号而言,具有抗干扰能力强、传输距离远等特点。第二代FPD-Link 被称为FPD-Link Ⅱ,采用SerDes 的接口,取代了第一代使用的LVDS 7:1 接口,只需1 对差分传输线便可完成数据与时钟信号的传输。FPD-Link Ⅲ作为第三代FPD-Link[9],在向下兼容FPD-Link Ⅱ的基础上,增加双向通信功能,并支持在链路上传输I2C 和CAN 等低速总线信号,且只支持SerDes-CML(Current Mode Logic)电平接口,这使其在3Gbps 的传输速率下理论上仍可实现10 m 的通信距离,在保证高速传输的情况下极大缩减了电缆与连接器的接口需求[10]。以1 路24 位RGB 编码的视频信号为例,表1对比了各个机载视频信号的特性。通过上表可以看出,在综合考虑各个机载视频信号的特点后,FPD-Link Ⅲ明显优于其余视频信号,因此本文提出一种基于FPD-Link Ⅲ的高速视频信号切换的设计方案,利用单片机作为接收切换控制信号的主控芯片,利用高速交叉开关芯片作为切换功能与信号处理的核心芯片,实现兼容多种视频格式输入的高速视频信号切换模块的设计,大规模扩展了视频通路并有效降低功耗与硬件成本,且具有较强抗衰减能力。

表1 常用机载视频信号特性比较

1 系统设计方案

本文设计的视频切换模块,主要完成对视频的输出选择控制,兼容1 路XGA 视频、1 路DVI 视频、1 路HDMI 视频、1 路LVDS 视频与8 路FPD-Link Ⅲ视频输入(分辨率为1 024×768@60 Hz),完成对这12 路输入视频的切换选择并实现最多12 路FPD-Link Ⅲ视频输出。切换控制指令通过SPI 总线由CPU 发送至单片机MCU,再通过SPI 总线由单片机MCU 对交叉开关进行配置,实现任意1 路输入视频在任意1 路或多路通道的输出。同时单片机还需对各编解码芯片根据视频分辨率进行相应配置,主要由XGA、DVI、HDMI、LVDS 视频解码电路和FPD-Link Ⅲ视频编码电路与切换电路以及时钟、电源、复位电路等组成。系统功能框图如下图1所示:

图1 视频切换系统功能框图

2 系统硬件设计

分析图1所示系统框架可知:视频切换系统的主要功能是实现FPD-Link Ⅲ视频信号的任意路由以及广播多播,同时兼容4 种常见的机载视频格式输入。该硬件系统可分为:时钟电源复位电路、主控制电路、视频格式转换电路、视频切换电路4 个部分构成。

2.1 时钟、电源、复位电路

本系统选择晶振SG7050CAN单片机提供8M工作时钟,采用2 片LTM4616IV#PBF 为系统转换各个工作电压,1 片负责5 V 转3.3 V,为各个芯片提供电源供电与上拉电压,另1 片负责5 V 转2.5 V、1.8 V 电压,为各个编解码芯片提供工作电压和IO 电压;选用TPS74401 芯片提供模拟1.8 V 电压,为芯片提供模拟/锁相环电压;此外选用MAX706 为该模块提供复位信号。

2.2 主控制电路

主控制电路由主控制芯片以及外围电路构成,处理器选用意法半导体STM32F103RBT7。该MCU 主频达到72 MHz,内置128 K FLASH 与20 K SRAM,支持2 路SPI、2 路I2C、3 路USART、1 路USB 与1 路CAN 共9 条5 类总线,便于控制视频切换模式的选择以及视频编解码芯片的配置。

在本系统设计中,利用MCU 的1 路SPI 总线与2 路I2C 总线完成以上控制操作。1 路SPI 总线用来接收外部(CPU 模块或JTAG 调试接口)切换命令;1 路I2C 总线完成对视频编解码芯片配置,使其满足当前分辨率下视频流的解码与编码操作;另1 路I2C 总线完成对高速交叉开关芯片模式的初始化与切换配置。

2.3 视频格式转换电路

本系统选用的高速交叉开关输入、输出通道均只支持PECL/CML 电平的差分信号,为了兼容其他视频格式,需要对XGA、DVI、HDMI、LVDS 这4 种视频格式进行转换为FPD-Link Ⅲ视频信号。

(1)XGA 解码器采用ADV7403,该芯片可将外部输入的模拟视频信号解码为24 位的数字RGB 信号,最高支持1 280×1 024@60 Hz 分辨率的VESA 格式视频数据;

(2)DVI 解码器采用TFP401,最高支持UXGA 方式,分辨率最高支持1 920×1 080@60 Hz;

(3)HDMI 解码器采用ADV7612,该芯片支持双路高清多媒体接口(HDMI),最高支持1 600×1 200@60 Hz 显示分辨率,可输出YCbCr 或RGB 2 种解码信号;

(4)LVDS 解码器采用SN75LVDS83 接收器,支持接收一组18/24 位色的LVDS 信号,最大分辨率支持1 280×1 024@60 Hz;

(5)FPD-Link Ⅲ编码器选用DS90UB925Q,支持5~85 MHz 像素时钟频率的24 位RGB 并行视频信号转换为FPD-Link Ⅲ高速视频信号。对DS90UB925Q 的VDDIO 按照1.8 V 电压供电用以满足在后端选用的高速信号交叉开关的电平要求。

2.4 视频切换电路

视频切换电路为本系统核心电路,根据方案设计要求,需要使用输入、输出各12 端口的高速差分交换芯片作为切换电路核心,ADN4612 芯片是一款12×12 高速差分信号交换芯片,拥有12 路差分PECL/CML 兼容输入和12 路差分CML输出,每个端口的数据速率最高达11.3 Gbps,支持输入通路的任意路由并支持多播和广播模式,满足项目开发需求。

在本设计中采用MCU 对外部SPI 总线接收相关指令,再通过I2C 总线对交换芯片寄存器进行配置转换,使得切换配置既可初始化设置,又可按照主机要求按需切换。ADN4612 芯片内含256 个寄存器,可适应多种工作需求下的模式设置,包括对FPD-Link Ⅲ信号进行预加重、均衡等多种增强操作,均可通过I2C 总线由MCU 进行配置。

3 系统软件配置

本系统的软件配置主要分为以下三个部分:视频解码芯片配置、视频编码芯片配置、视频切换芯片配置。

3.1 视频解码芯片配置

芯片ADV7403、ADV7612 可根据不同配置对不同制式的视频信号进行解码处理,因此需要根据对输入、输出的视频格式、刷新率、视频增强、偏移等功能对相应芯片的寄存器进行配置,使其符合系统设计需求。这两种解码器均留有I2C 接口,可以通过MCU 进行寄存器配置,更灵活地实现视频信号格式、质量的调节。其余解码器通过外部电路配置即可满足要求,不再需要通过寄存器配置。

3.2 视频编码芯片配置

编码器DS90UB925Q 可将并行RGB 信号编码为FPDLink Ⅲ信号,考虑后端交叉开关芯片需求与传输距离要求,可对该编码器进行接口、时钟采样、工作模式、去加重等功能进行配置。同样的该芯片留有I2C 接口,仍可通过MCU 对其进行寄存器配置。

3.3 视频切换芯片配置

视频切换芯片采用高速交叉开关ADN4612 实现,除完成对信号的任意路由及广播功能的配置之外,还承担着对信号质量增强并实现软距离传输的功能。信号速率越高,高频信号的趋肤效应越明显,高频成分衰减较大。且信号在板间及整机间传输,插损、回损会极大地影响信号完整性,因此需要对信号进行补偿,即在接收端进行均衡处理,在发送端进行预加重处理。

根据芯片相关信号传输眼图,由图2、图3可以看出,当高速信号未进行均衡或预加重处理时信号的高频分量衰减很大,信号质量受到严重影响。而分别进行均衡与预加重操作后,信号质量有了明显改善。本系统传输的1 024×768@60 Hz 的FPD-Link Ⅲ信号速率大致在2 Gbps,属于高频信号,传输过程中高频分量衰减严重,且接收的来自外部的8 路FPD-Link Ⅲ信号质量不可控,故需要对输入信号进行均衡、对输出信号进行预加重处理。

图2 高速信号在不同均衡配置下传输1 米时的眼图

图3 高速信号在不同预加重配置下传输1 米时的眼图

根据手册对地址从0×20 到0×88 的寄存器进行预加重与均衡配置,令FPD-Link Ⅲ信号幅值增加、增益增强,满足机上远距离传输需求。在系统调试中,预加重操作按(003B)13.98 dB 增益配置,均衡操作按反向(0xD)12 dB、正向(0xD)9 dB 增益配置。在整机输出端连接10米长电缆后端测得任意1 路FPD-Link Ⅲ视频信号的信息,仍具有较好的完整性,码间串扰与噪声影响较小,说明均衡、预加重操作配置可以较好地解决高频分量衰减的问题,视频图像可以稳定显示无抖动、闪屏、偏色等问题,表明系统工作状态良好。

4 结语

综上所述,本文设计并开发了一种基于FPD-Link Ⅲ的机载高速视频信号切换系统,通过分析FPD-Link Ⅲ相较于其余机载视频信号的优势,确定了本方案的实用性与优势,且考虑到目前常用的相应机载视频信号,通过兼容性设计可以兼容VGA、DVI、LVDS、HDMI等4种视频格式输入,便于对现有设备进行替换。方案介绍了整体系统架构与各个功能模块的芯片选型,并给出了实际应用下对于高速信号补偿的寄存器配置。通过实际测试与验证可以表明:本系统可以实现1 024×768@60 Hz 分辨率的12 路视频的任意切换与广播功能,在经过远距离传输后视频显示稳定、无闪烁、无偏色,取得了预期效果。