等离子体表面阶跃型梯度硅沉积对环氧树脂闪络性能的影响

2022-05-13闫纪源梁贵书段祺君阮浩鸥康玉婵彭程凯

闫纪源 梁贵书 段祺君 阮浩鸥 康玉婵 彭程凯 谢 庆

(1. 华北电力大学新能源电力系统国家重点实验室 北京 102206 2. 华北电力大学电力与电子工程系 保定 071003)

0 引言

气体绝缘输电线路(Gas Insulated transmission Lines, GIL)具有输电容量大、安装和运维方便、不受恶劣气候影响等特点,在快速发展的高压直流输电系统中得到了大量的应用[1-4]。氧化铝/环氧树脂(Al2O3-ER)复合材料因机械强度高、电气性能优良、制备简单而作为GIL内盆式绝缘子的常用材料[5-7]。然而盆式绝缘子在直流高压下会积聚大量表面电荷,长时间运行有可能造成局部放电甚至发生沿面闪络,成为电力系统安全稳定运行的隐患[8-10]。

对于绝缘材料的沿面闪络研究,国内外学者通过表面处理[11-14]和填料掺杂[15-18]等方法来优化电场分布、加快表面电荷消散,进而提升材料的沿面闪络性能。对于表面处理方法,李传扬等通过磁控溅射法在绝缘材料表面沉积Cr2O3薄膜,进而抑制表面电荷的注入[19]。张冠军等通过喷砂、激光刻蚀、砂纸打磨等方法调控材料的表面粗糙度,并研究表面形貌与闪络电压的关系[20-22]。安振连等通过表面氟化法提高了环氧树脂的表面电导率、降低了陷阱深度并减少了表面电荷积聚[23]。以上方法虽然效果显著,但设备造价昂贵并且改性时间较长,难以实现大规模的工业应用。大气压等离子体射流(Atmospheric-Pressure Plasma Jet, APPJ)技术因设备简单、操作方便、反应效率高、环境友好、仅作用于材料表面而不影响材料内部结构等特点,成为近几年来绝缘材料表面改性的研究热点[24-26]。张冠军等使用He/CF4混合气体实现了环氧树脂的APPJ氟化处理,发现随着氟化时间的增长,材料的表面粗糙度不断增加,憎水性逐渐增加,但材料的真空闪络电压先升后降[27]。谢庆等以正硅酸乙酯(Tetraethyl Orthosilicate, TEOS)为反应前驱物,通过APPJ硅沉积方法在Al2O3-ER表面沉积SiCxHyOz薄膜,加快了材料的表面电荷消散速率并提升了闪络性能[28]。邵涛等通过调整APPJ硅沉积的反应物浓度[29]、气体流速[30]、激励电源[31]、电极结构[32]等参数控制绝缘材料的表面粗糙度、水接触角、表面官能团等表面理化特性,并研究APPJ对绝缘材料表面电气性能的影响机理。

目前的APPJ方法主要从构造射流阵列、控制射流管运动等角度来扩大处理面积,使样片整体得到均匀的改性[33-34]。但实际工况下的电场为非均匀分布,对绝缘材料的均匀改性难以达到最佳的提升效果。有研究表明,通过掺杂ZnO、SiC等非线性电导填料可以实现绝缘材料对非均匀电场的自适应调控[35-36],并且填充位置和填充含量影响着盆式绝缘子的电场分布和功率损耗[37]。杜伯学等通过构造表层功能梯度材料来主动调控材料的表面介电参数,进而减少电场畸变[38]。李进等通过仿真手段研究材料表层介电参数的最优梯度分布,通过磁控溅射、表层氟化等方式实现材料的表面梯度改性,并提升材料的沿面闪络性能[39-40]。

本文结合APPJ硅沉积技术与表层功能梯度改性思路,实现Al2O3-ER的表面阶跃型梯度改性。通过测量未处理、均匀处理、梯度处理样片的理化特性与电气参数,分析了表面阶跃型梯度改性对沿面闪络性能的提升机理,给出了极不均匀电场下材料表面参数调控策略。

1 实验装置与方法

1.1 样片制备与改性

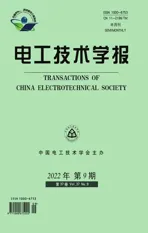

本文所用Al2O3-ER样片均由课题组自主制备。具体成分和配比见表1。制备时将所有原料按比例加入玻璃器皿并用机械搅拌机搅拌10min,然后将混合溶液放置入真空干燥箱中,在60℃的环境下进行真空脱泡。同时将铁制模具喷涂脱模剂后加热至80℃,待混合溶液内的气泡全部升腾破裂后,将脱气泡的溶液浇注到模具中并在真空干燥箱中加热至120℃。在经过2h的固化后即可得到直径40mm,厚2mm的Al2O3-ER样片。制备好的样片需用装有无水乙醇和去离子水的超声清洗机中各清洗20min,再放入真空干燥箱内室温干燥24h后方可进行改性处理。

表1 样片成分和配比 Tab.1 The composition and proportion of samples

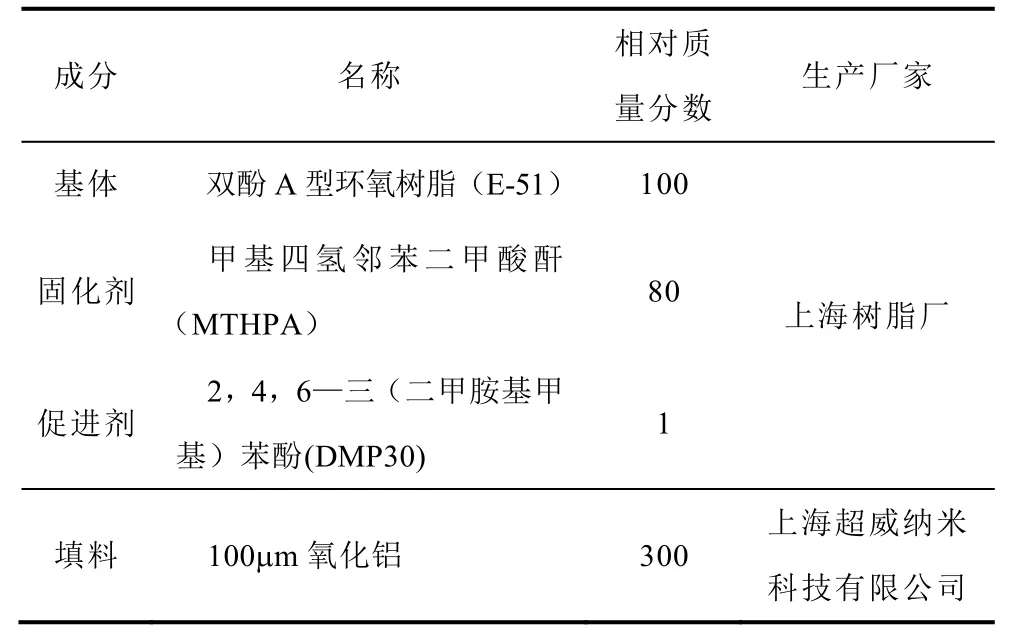

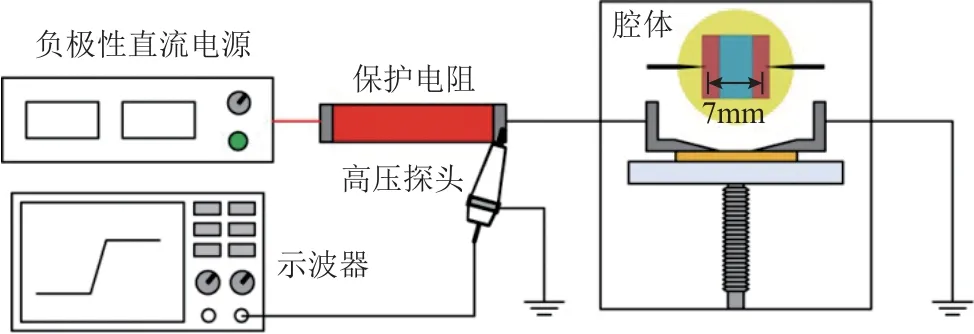

本文通过APPJ改性平台,实现Al2O3-ER的表面均匀硅沉积与表面阶跃型梯度硅沉积,等离子体表面硅沉积平面实验装置如图1所示。全套装置由南京苏曼等离子科技有限公司研制,主要包括射流枪、气路、电路三部分。射流枪由电路模块、气路模块以及绝缘与固定部件组成。电路模块以两个直径40mm、高20mm的铁制圆柱作为高压端与接地端,圆柱内有4个2×2排列的小孔,孔径8mm。气路模块为4根外径8mm、内径4mm、长180mm的石英玻璃管。组装时分别将玻璃管穿过高压模块与接地模块,经绝缘部件固定后即可使用。本文仅用其中两根射流管。气路部分包括两路高纯氩气(纯度≥99.999%)、质量流量计、加热装置和作为反应前驱物的TEOS。一路氩气作为载气,以1L/min的流速通入装有前驱物的洗气瓶中,同时加热洗气瓶至70℃;另一路氩气以10L/min的流速与载气充分混合,混合气体再平均通入两路射流管。电路部分方面,以高频高压电源(输出电压0~20kV、中心频率50kHz)为等离子体激励源,使用前将电源与射流枪的高压端相连,射流枪接地端与0.1μF电容串 联后接地。实验时使用Tektronix DPO 2002B示波器监视等离子体放电参数。当电源电压为4.5kV,电源频率53kHz时,射流管端部会产生淡紫色火焰,此时通过升降平台调整样片表面与射流管端部的间距为15mm后,即可认为改性开始并计时。

图1 等离子体表面硅沉积平面 Fig.1 The plasma surface silicon deposition platform

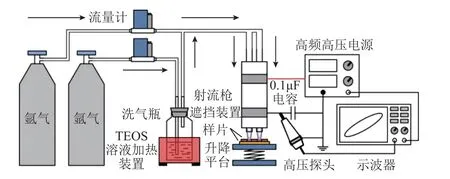

在进行等离子体表面阶跃型梯度改性时,首先将样片表面划分为高场强区和低场强区,样片分区示意图如图2所示。低场强区宽4mm,区域中心与样片圆心重合;高场强区由两块宽2mm的矩形区域构成,并且紧贴于低场强区两侧。实验时两类区域单独处理,即在处理高场强区时,使用遮挡装置盖住低场强区以避免相互干扰。由于高场强区由两块区域组成并且相距较远,导致单路射流管无法同步处理,为保证高场强区的处理效果一致,调整两路射流管间距使其中心与两块高场强区中心重合,并同时进行处理。在处理低场强区时,同样遮挡高场强区并用两路射流管同时处理该区域。高场强区和低场强区处理时间均为3min和5min,即样片表面硅沉积时间从左到右依次为3min,5min,3min和5min,3min,5min,样片标记为Si3-5-3和Si5-3-5。此外,以等离子体表面均匀硅沉积3min和5min样片作为对照组,分别标记为Si3和Si5,未处理样片标记为UT。

图2 样片分区示意图 Fig.2 The schematic diagram of sample partition

1.2 样片表面性能测试方法

本文对等离子体改性前后样片的表面形貌、化学成分和表面电气性能进行了测试。其中通过扫描电子显微镜(SEM,Zeiss Sigma)观察样片表面微观形貌,并用表面轮廓仪(Bruker Contour GTK)测量表面粗糙度;通过X射线光电子能谱分析仪(XPS,Thermo Scientific Escalab 250Xi)获得样片的表面元素成分和相对含量;通过SM7110 高阻计测量表面电导率。

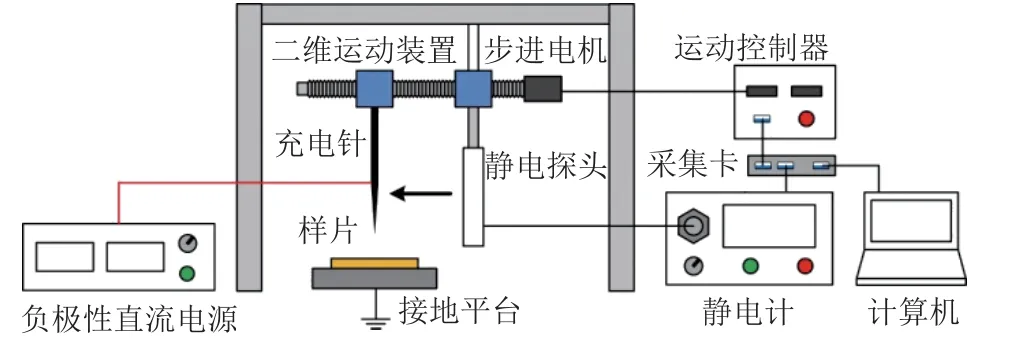

样片的沿面闪络实验和表面电荷测试平台均由课题组自主搭建,其中沿面闪络实验平台如图3所示。实验前设置针-针电极间距为7mm,通过腔体内的绝缘升降平台使样片紧贴针-针电极下端,左侧针电极通过10MΩ的保护电阻与负极性直流高压电源(输出电压0~-50kV)串联,右侧针电极接地。控制环境温度为25℃,相对湿度30%。实验时以0.1kV/s的速率匀速升压,直至样片发生沿面闪络时立即断电,通过Tektronix DPO 2002B示波器和Trek P6015高压探头捕捉并记录闪络电压的波形和幅值。每种样片进行10次闪络实验,取平均值作为该样片的闪络电压值。

图3 沿面闪络测试平台 Fig.3 The surface flashover test platform

研究表明,绝缘材料发生沿面闪络与表面电荷特性密切相关,而表面电荷密度与材料表面电位近似呈正比关系[41]。因此本文通过研究样片的表面电位衰减特性来反映表面电荷的消散情况。表面电位测量平台如图4所示。样片放置在可升降的接地平台上,上表面与电晕充电针间距7mm。将电晕充电针尖调整到待测点位正上方,设置充电电压-7kV,持续时间1min,充电完成后通过二维运动装置将Trek-6000B型静电探头移至充电点位上方2mm处,使用Trek P0865型静电计与采集卡记录30min的表面电位衰减数据。表面电位测量实验环境温度为25℃,相对湿度30%。

图4 表面电位测量平台 Fig.4 The surface potential measurement platform

2 实验结果

2.1 表面形貌测试结果

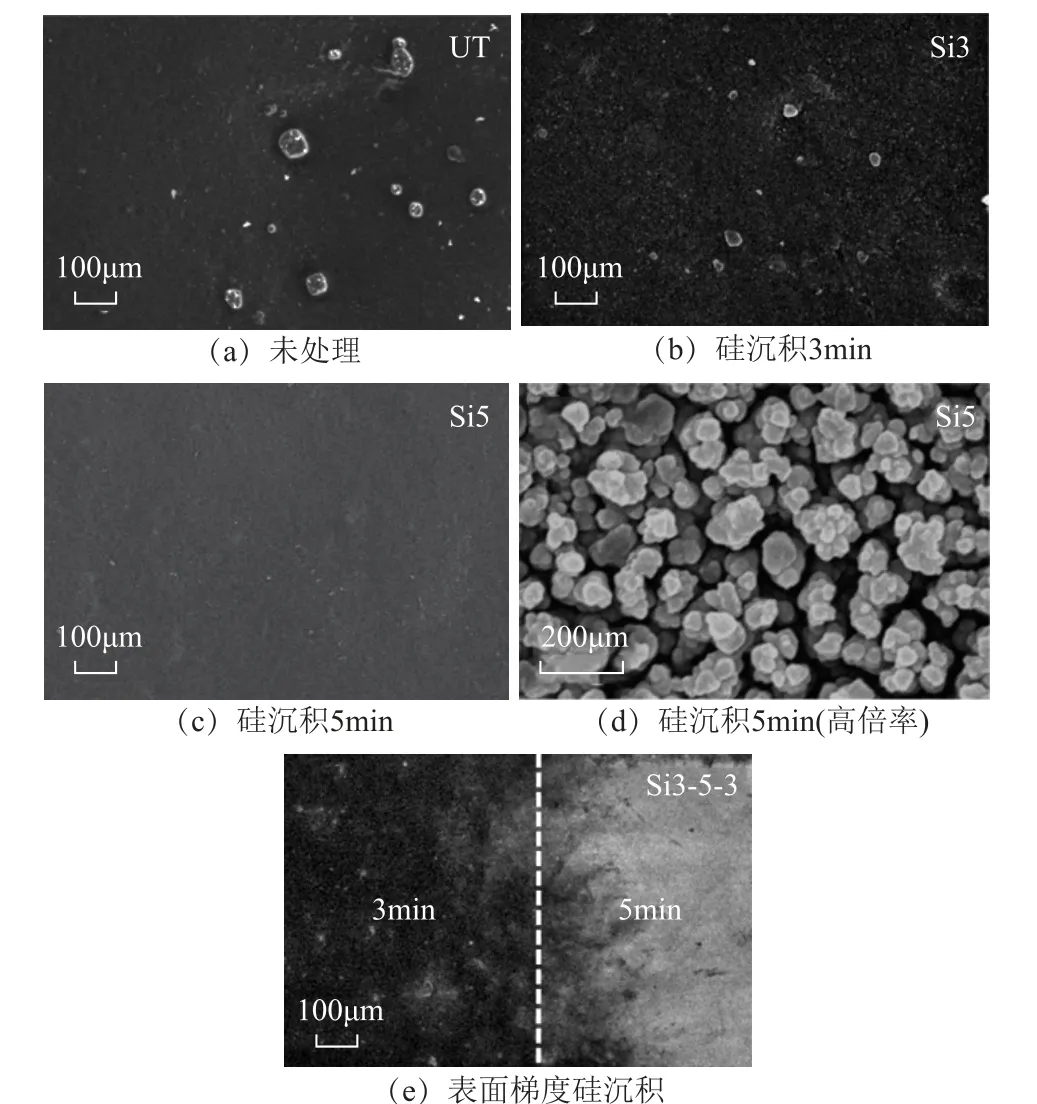

图5为等离子体改性前后样片SEM图。可以发现,图5a所示的未处理样片上存在少许微米级别的颗粒,可能是样片制备时部分氧化铝填料沉积在材料表面。这类缺陷会畸变外部电场并促进局部放电,成为绝缘性能的薄弱环节[8]。图5b所示的Si3样片表面上有部分缺陷被覆盖,表面凸起减少并趋于平整。图5c表明,当硅沉积时间达到5min时,大多数缺陷均被覆盖,表面平整度更高。图5d为Si5样片的高倍放大图,发现样片表面生成了由纳米级珊瑚状颗粒组成的薄膜[30]。图5e展示了等离子体表面梯度硅沉积样片(Si3-5-3)的梯度分面界情况。分界面左侧采用3min硅沉积处理,右侧硅沉积时间为5min。由于不同沉积时间生成的薄膜厚度有所区别,导致图中呈现明显的亮暗分界。暗区有部分凸起存在,而亮区表面更加平整,这与相同处理时间下均匀硅沉积的表面形貌相近。该图表明本文成功实现了Al2O3-ER的表面梯度硅沉积。

图5 改性前后样片SEM图 Fig.5 The SEM images before and after modification

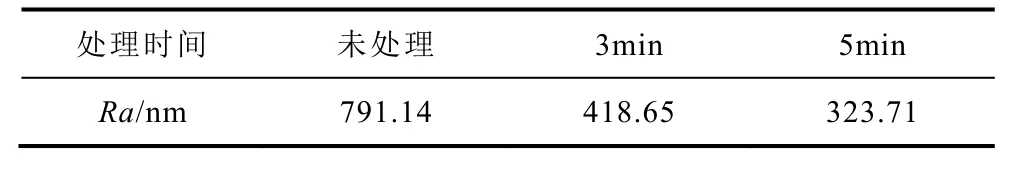

为进一步研究改性前后样片表面平整程度的变化,本文测量了未处理样片以及阶跃型梯度硅沉积样片不同区域的表面粗糙度情况。以轮廓算数平均偏差值Ra来衡量样片表面粗糙度,改性前后样片表面粗糙度结果见表2。结合样片表面SEM图可知,未处理的样片表面存在因少量填料沉积而形成的突起,表面粗糙度较高;经3min的等离子体硅沉积后样片表面表面粗糙度明显降低,部分表面缺陷也被薄膜覆盖;处理时间延长到5min时,样片表面粗糙度进一步下降,多数缺陷已被完全覆盖。综上可知,等离子体硅沉积可降低材料表面粗糙度,并修复部分表面缺陷。

表2 改性前后样片表面粗糙度 Tab.2 The surface roughness of all samples

2.2 表面化学成分测试结果

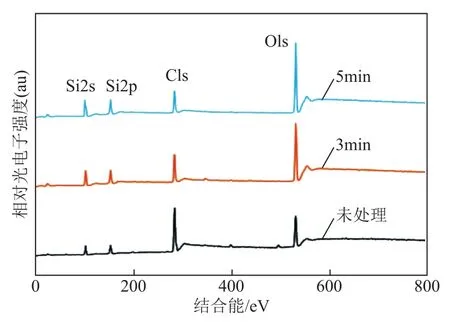

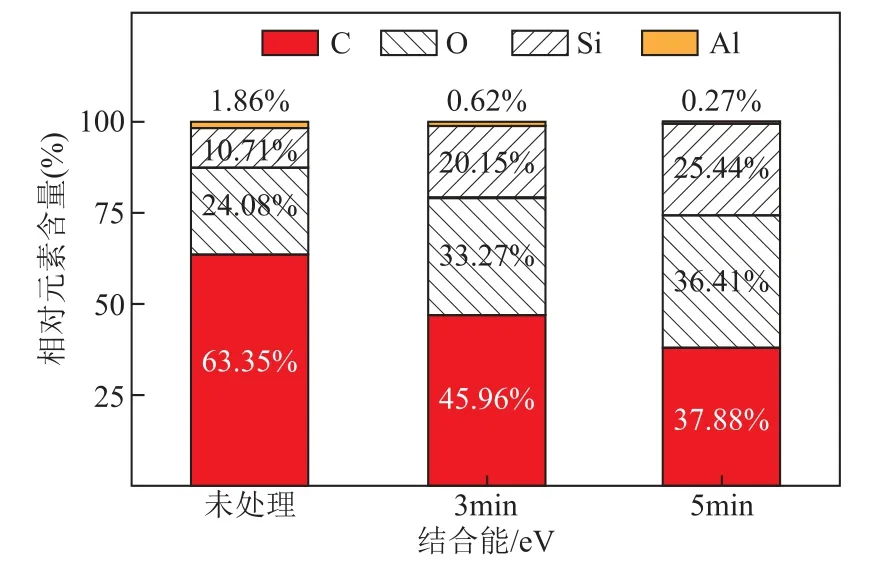

对Si3-5-3样片硅沉积3min区和5min区进行XPS测试,并与未处理样片进行对比,测试结果如图6所示。由于氧化铝填料使用了硅烷偶联剂进行预处理,因此未改性样片的XPS谱图也有Si2s和Si2p峰存在。而Si3-5-3样片上3min区和5min区的C1s峰的峰值显著下降,Si2s、Si2p和O1s峰的峰值有所上升。图7给出了改性前后样片相对元素含量的变化情况。发现Si3-5-3样片不同区域的化学元素占比有所区别。其中硅元素和氧元素的相对含量随改性时间的增长而有所提高,并且由于含硅薄膜沉积在样片表面,使一部分暴露的氧化铝填料被重新覆盖,导致铝元素含量下降。

图6 改性前后样片XPS谱图 Fig.6 The XPS spectra of samples

图7 改性前后样片相对元素含量 Fig.7 The relative element content of samples

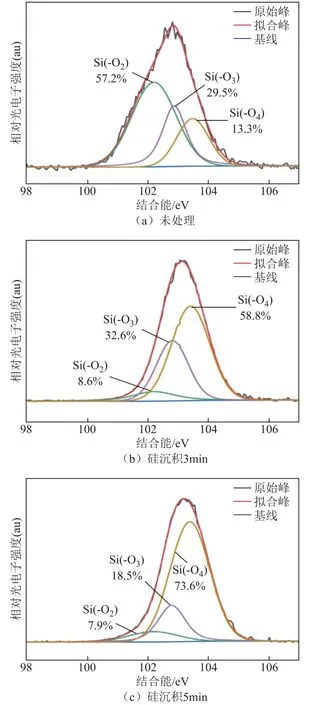

为进一步分析样片表面含硅基团的变化情况,对改性前后样片的Si2p峰进行分峰处理,如图8所示。发现所有样片的Si2p峰可分解成Si(-O2)峰(102.2eV)、Si(-O3)峰(102.8eV)和 Si(-O4)峰(103.4eV),但各峰相对面积占比有所不同。等离子体硅沉积可以提高Si(-O3)和Si(-O4)峰的相对含量,这是因为Si(-O2)官能团与氧化裂解的TEOS进一步发生反应,生成氧化程度更高的Si(-O3)和Si(-O4)官能团并沉积到材料表面,并且随着处理时间的增加使反应更加充分[28]。

图8 不同样片Si2p峰的分峰处理结果 Fig.8 The XPS-peak-differenating results of samples

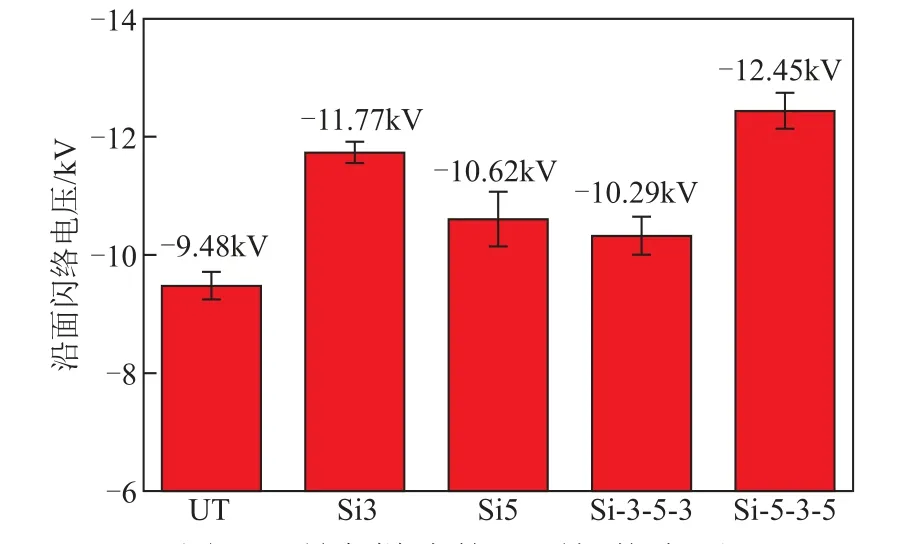

2.3 沿面闪络测试结果

对未处理、均匀硅沉积和阶跃型梯度硅沉积样片的沿面闪络电压测试结果如图9所示。可以发现,Si3样片的闪络电压相比未处理样片提升了24.1%,虽然Si5样片延长了硅沉积时间,但闪络电压仅提升了12%。此外,采用等离子体表面阶跃型梯度硅沉积虽然也提高了闪络电压,但不同梯度分布对闪络电压的影响有着显著区别。当高场强区采用长时间硅沉积处理、低场强区进行短时间的硅沉积时,样片闪络电压的提升效果最好,可达31.3%。然而,当低场强区使用5min的硅沉积时,虽然闪络电压仍高于未处理样片,但最低仅提升8.5%。

图9 所有样片的沿面闪络电压 Fig.9 The surface flashover voltage of all samples

2.4 表面电位衰减测试结果

本文对Si3-5-3中的3min区和5min区进行了表面电位衰减测试,并且同样与未处理的样片进行对比,样片表面电位衰减曲线如图10所示。充电条件相同时,等离子体硅沉积区域的初始表面电位要低于未处理样片,并且5min区的初始表面电位值相比未处理样片降低了39%。这说明等离子体硅沉积可以减少表面电荷积聚,并且使Si3-5-3样片上的表面电荷积聚能力不均匀。另一方面,Si3-5-3样片不同区域的表面电位衰减速率有所不同,但相比未处理样片均有明显提升。其中5min区的表面电位下降最明显,这意味着该区域的表面电荷消散最快,同样意味着等离子体表面阶跃型梯度硅沉积可以使样片表面上有不同的电荷消散速率。

图10 样片表面电位衰减曲线 Fig.10 The surface potential decay curves of samples

为进一步探索表面电荷消散加快的原因,本文采用文献[42]提到的等温表面电位衰减(Isothermal Surface Potential Decay, ISPD)理论计算出不同样片的陷阱能级分布情况,如图11所示。发现未处理样片的深陷阱密度较大,陷阱中心能级可达1.1eV。Si3-5-3样片上3min区的深陷阱中心能级明显降低,并且出现了中心能级0.95eV左右的浅陷阱峰。5min区的深陷阱中心能级继续降低,并且浅陷阱密度进一步升高。以上分析表明等离子体硅沉积可以降低样片表面深陷阱能级并引入浅陷阱,并且阶跃型梯度硅沉积可以使样片的陷阱能级呈非均匀分布。

图11 样片陷阱能级分布曲线 Fig.11 The trap level distribution curves of samples

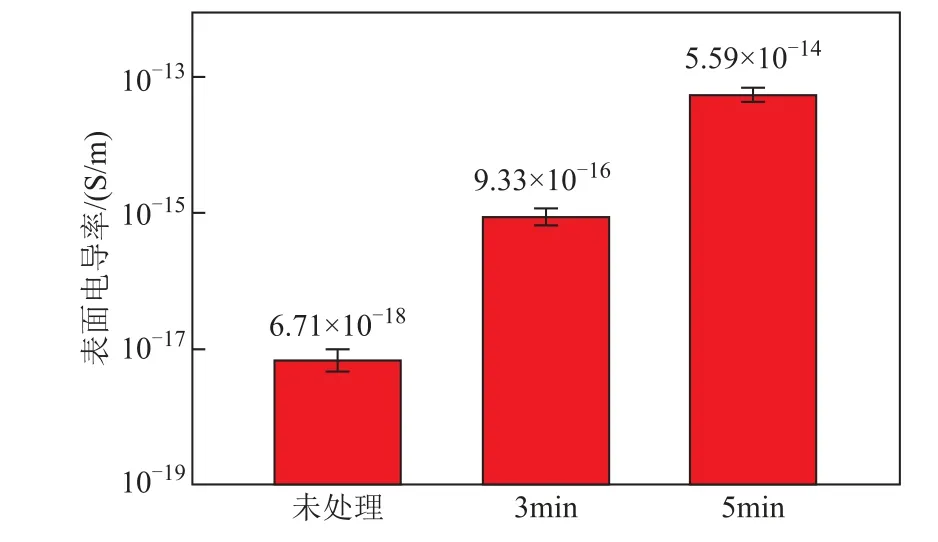

2.5 表面电导率测试结果

表面电导率不仅是绝缘材料的重要指标,也影响着材料表面电荷的消散能力[38]。Si3-5-3不同区域以及未处理样片的表面电导率测试结果如图12所示。发现随着硅沉积时间的增加,样片的表面电导率逐渐提高。其中硅沉积3min区域的表面电导率提升了2个数量级,而5min区相比未处理样片提升了4个数量级。这表明Si3-5-3样片整体的表面电导率呈阶跃型梯度分布。

图12 样片表面电导率 Fig.12 The surface conductivities of samples

2.6 电场仿真结果

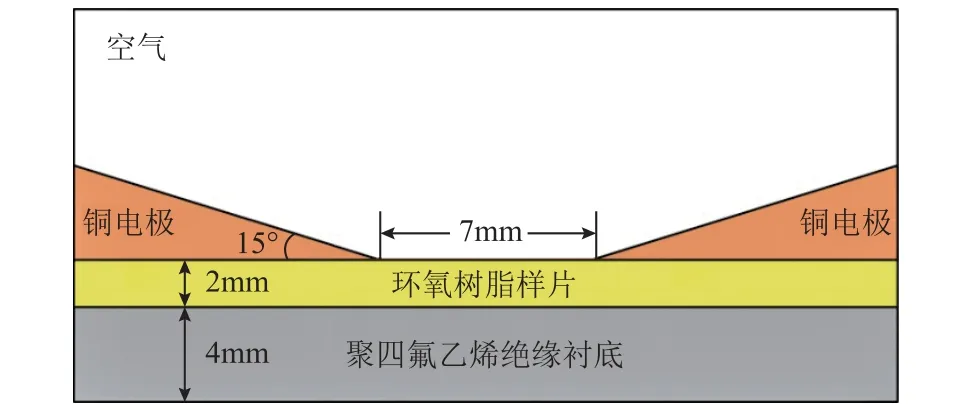

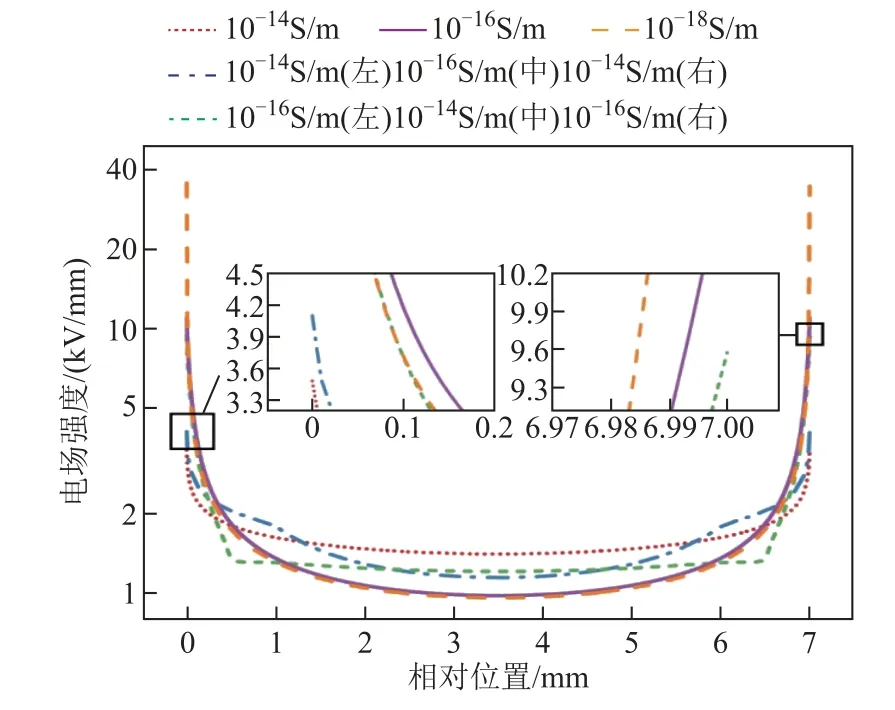

由2.5节可知,等离子体表面阶跃型梯度硅沉积可以得到表面电导率呈阶跃型梯度分布的样片。为研究阶跃型表面电导率对针-针电极电场强度分布的影响,本文使用COMSOL Multiphysics软件搭建了针-针电极的瞬态场仿真模型。几何模型如图13所示。各元件尺寸与沿面闪络实验的参数相同,即设置针-针电极间距为7mm,针尖尖端倾斜角为15°,材料为铜;设置样片厚度2mm,材料为环氧树脂;设置绝缘衬底厚度4mm,材料为聚四氟乙烯;环境气体设置为空气;左侧电极设置-10kV直流电压,右侧电极接地。

图13 电场仿真几何模型 Fig.13 The geometric model of electric field simulation

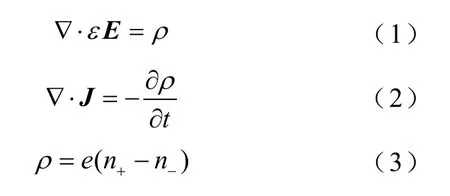

本文采用静电场模型计算电场分布,即电场强度E满足关系

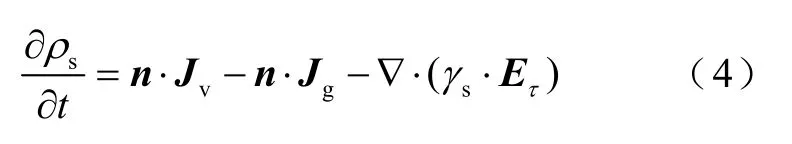

式中,ε为绝缘材料的介电常数;ρ为空间电荷密度;J为传导电流密度;n+和n-分别为正、负离子浓度;e为元电荷量。由于直流电场中气-固界面电荷主要来自气体侧的离子输运以及固体侧和表面上的传导[8],根据电流的连续性,气-固界面电荷密度ρs可表示为

式中,n为气固界面单位法向矢量;Jv为固体侧电流密度;Jg为气体侧电流密度;sγ为绝缘材料的表面电导率;Eτ为气-固界面电场的切向分量。式(4)考虑了固体侧传导、气体侧传导和表面传导三种途径对表面电荷积聚过程的影响。对于固体侧传导,忽略环境温度对材料的影响,即材料的体积电导率vγ为常数,则固体侧电流密度Jv为

对于电荷在气体中的运动特性,本文采用稀物质场传递模型模拟电荷的产生、扩散和复合。根据文献[43],电荷运动方程为

式中,nIP为正负离子产生率;kr为正负离子复合系数;b+和b−为正负离子迁移率;D+和D−为正负离子的扩散系数。进一步可知气体侧电流密度Jg为

对于表面电导率sγ,本文根据图12所示的改性前后样片表面电导率测试结果,设置表面电导率为阶跃型梯度函数,即按照图2所示划分方法,对高低场强区设置不同的表面电导率,研究此时电场分布的变化情况,并对比均匀表面电导率下的电场。仿真结果如图14所示。图14结合文献[44-45]可知,针-针电极阴极三结合点处的电场强度要远高于两电极间,两类区域场强的明显差异会导致大量表面电荷积聚在针尖附近,进一步畸变外部电场并引发闪络。即针-针电极产生的极不均匀电场可离散化的看成高低场强的阶跃变化,高低场强对应的区域对表面电荷消散速率的需求有所区别,因此本文针对这一特点进行了高低场强区域的划分。此外,考虑到改性区域交界处对急剧变化的高场强区的影响,预留了1mm左右的处理裕度来使交界处尽量落在低场强区,从而将交界处的影响降至最低。由于针-针电极产生的最大场强决定了材料的表面绝缘性能,因此表3列出了各种表面电导率分布下的最大 场强值。发现提高材料整体的表面电导率以及采用阶跃型梯度表面电导分布均可大幅降低电场强度。结合等离子体硅沉积对材料表面电导率的影响,可以认为等离子体表面均匀硅沉积和阶跃型梯度硅沉积均可抑制针-针电极的电场畸变。

图14 不同表面电导率分布下的电场仿真 Fig.14 The electric field simulation of different surface conductivity distributions

表3 不同表面电导率分布的最大场强 Tab.3 The maximum electric field strength of different surface conductivity distributions

3 分析与讨论

研究表明,减小外部电场的畸变可以有效提升材料表面的绝缘性能[39]。从电场仿真结果来看,样片表面电导率呈阶跃型梯度分布可以有效降低最大场强,减小电场的畸变率。然而,提高样片整体的表面电导率对场强的均化效果更好,从仿真的角度来讲均匀改性似乎更能提高样片的闪络性能。但从沿面闪络的测试结果看来,提升效果最好的改性方法仍然是阶跃型梯度硅沉积,并且表面电导率过大反而会降低闪络电压的增长率。这是因为影响绝缘材料沿面闪络性能的因素不仅包括外部电场和表面电导率,还有表面粗糙度、表面化学成分、表面电荷的积聚与消散等[7,41]。由图10可知,所有采用等离子体硅沉积处理的样片,其闪络电压均高于未处理样片。除了表面电导率提升这一因素外,等离子体硅沉积方法会在Al2O3-ER表面生成均匀致密的薄膜,一方面会覆盖材料表面原有的毛刺、凸起等表面缺陷,降低表面粗糙度进而削弱表面缺陷对电场的畸变作用。另一方面,未改性材料表面存在大量的深陷阱,表面电荷被深陷阱捕获后难以脱陷,导致宏观上的表面电荷积聚现象。而表面沉积硅氧类薄膜会改变材料表面陷阱分布,使原有的深陷阱中心能级逐渐变浅,并且接枝在材料表面的SiOx基团会引入能级更低的浅陷阱,表面电荷被浅陷阱捕获后所需的逸出功更低,因此更容易脱陷并跃迁至其他区域,从宏观上看即为表面电荷积聚量减少并且消散速率加快,进而抑制了表面电荷对外部电场的畸变作用。抑制表面缺陷和表面电荷对电场的畸变可显著提升材料的沿面闪络性能。

进一步研究闪络电压测试结果,发现对低场强区使用长时间的等离子体硅沉积会显著抑制闪络电压的提升(Si5和Si3-5-3),只有高场强区长时间硅沉积、低场强区短时间硅沉积才能最大程度地提升闪络电压(Si5-3-5)。由针-针电极的电场分布可知,三结合点处附近为高场强区,大量的空间电荷受电场力和气体电离等作用而积聚在该区域,使高场强区的表面电荷量要远大于低场强区,从而进一步畸变高场强区的电场,加剧气体电离甚至产生局部放电[40]。因此高场强区对表面电荷快速消散的需求更加迫切。与之相对的是,低场强区的表面电荷积聚量相对较低,适当加快该区域的电荷消散有利于提高闪络电压,但低场强区的表面电荷消散过快反而为样片整体的放电发展提供了种子电荷,促进了贯穿性导电通道的形成,不利于样片的表面绝缘性能[31]。因此,加快高场强区表面电荷的消散并适当控制低场强区的消散速率可以最大限度地提升样片整体的沿面闪络性能。由于等离子体硅沉积与表面电荷消散速率正相关,因此对高场强区使用长时间硅沉积、低场强区短时间硅沉积的(Si5-3-5)样片闪络电压最高。

4 结论

本文根据针-针电极的电场特性,将样片表面划分为高场强区和低场强区,并通过APPJ硅沉积技术,实现了Al2O3-ER表面阶跃型梯度硅沉积,以均匀硅沉积样片和未改性样片为对照组,测试了样片的理化特性和电气参数。对不同表面电导率分布进行了电场仿真,并结合电场分布和电荷运动特性,分析了表面阶跃型梯度改性对沿面闪络性能的提升机理。主要结论如下:

1)等离子体硅沉积技术可以在改性区域表面沉积硅氧类薄膜,从而降低该区域的表面粗糙度、提高硅元素含量、引入浅陷阱并加快表面电荷消散速率,并且改性效果与处理时间呈正相关。

2)等离子体硅沉积可以提高样片的闪络电压,其中高场强区长时间硅沉积、低场强区短时间硅沉积的样片闪络电压最高。相反,对低场强区采用长时间硅沉积会明显抑制闪络电压的提升。

3)样片的不同区域对表面电荷消散速率的需求有所区别。加快高场强区的表面电荷消散并适当调控低场强区的消散速率,可以显著提升样片整体的闪络性能。反之,高场强区则会因为表面电荷积聚过多而畸变外部电场,同时低场强区表面电荷过快的消散会为放电发展提供种子电荷,为贯穿性导电通道的形成提供有利条件。

4)采用等离子体表面阶跃型梯度硅沉积方法,一方面使样片的表面电导率呈阶跃型梯度分布,可以有效减小针-针电极的最大场强;另一方面,相比于均匀处理,该方法可以针对性地调控样片表面不同区域的电荷消散速率,充分发挥等离子体硅沉积对提高闪络性能的优势并减少不利影响,进而最大程度地提升沿面闪络电压。