基于V93000的模数转换器ADS8364的测试方法研究*

2021-10-09王庆

王 庆

(武汉数字工程研究所 武汉 430205)

1 引言

ADS8364是德州仪器生产的一款250kSPS、16位、6通道同时采样模拟到数字转换器(ADC)[1]。ADS8364应用广泛[2~3],它可以用在电机控制、三相电源控制以及多轴定位系统等领域[4~5]。本文基于V93000自动测试系统,进行ADS8364测试程序的设计和开发。

2 ADS8364的内部结构

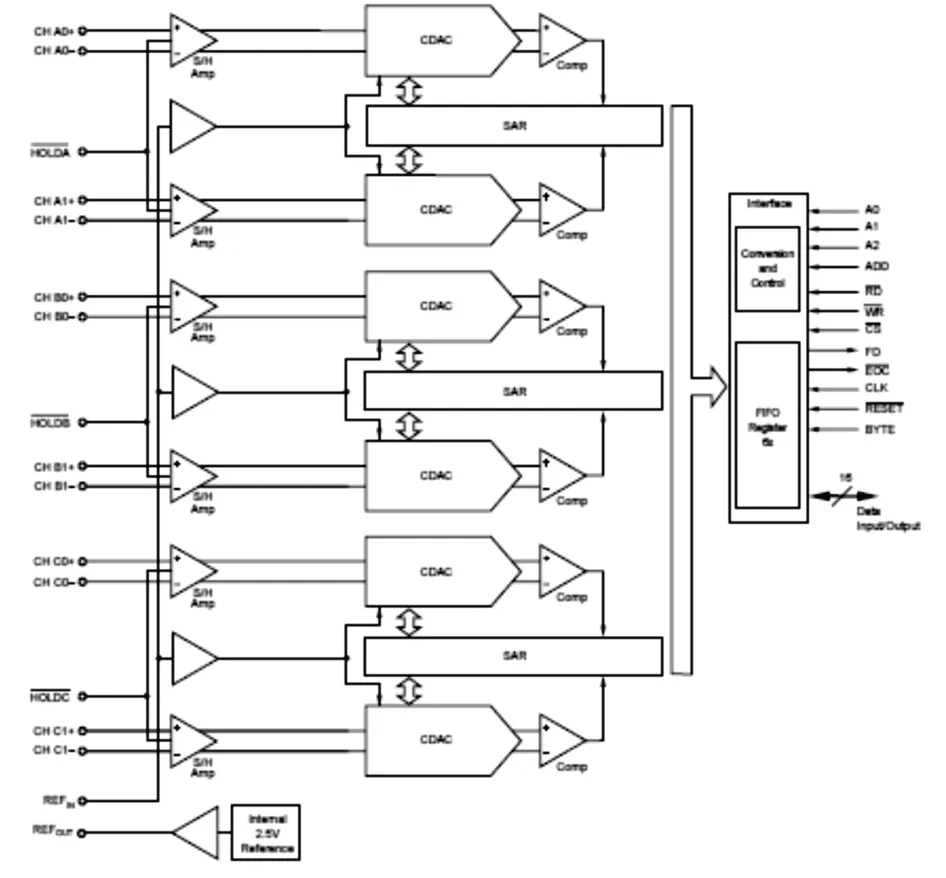

ADS8364的内部结构如图1所示,它主要由差分输入、ADC和FIFO组成。

图1 ADS8364的内部结构

ADS8364的输入为6对差分通道,用于高速同步信号采集,差分通道的使用使ADS8364在50KHz时有出色的80dB共模抑制性能,能让ADS8364在高噪声环境中使用。每对差分通道都连接到内部的一个模拟到数字转换器(ADC),内部ADC是16位的,是独立的,能够同时进行采样和转换。共有6个,是独立的16连接至一个独立的16位250kSPS的SAR型ADC。

ADS8364的内部ADC为16位SAR(Successive Approximation register,逐次逼近寄存器)型电容式ADC。每个ADC主要由SAR、电容式数模转换器(CDAC)和高速比较器组成。SAR型ADC的工作流程是,模拟输入电压(VIN)经采样保持后,逐次与D/A转换器输出对应电压进行比较[5]。首先逐次比较寄存器最高位置1,指示D/A转换器输出对应电压到比较器反相端与Vi比较,如果Vi大于该电压,则比较器输出为1,逐次比较寄存器采样到1保存最高位为1,反之为0。依次比较直到最后一位,届时所存数据并输出。

ADS8364提供了灵活的高速并行接口,具有直接地址模式、周期和FIFO模式。每个通道的输出数据均以16位字的形式提供。ADC的模数转换后的值保存在六个FIFO寄存器中。对于每次读取操作,ADS8364输出16位信息(16个数据或3通道地址,数据有效以及一些同步信息)。地址/模式信号(A0,A1和A2)选择如何从ADS8364读取数据。这些地址/模式信号可以定义单个通道的选择,循环通过所有通道的循环模式或对由保持信号的顺序确定的数据进行排序的FIFO模式。FIFO模式将允许单个通道对使用六个寄存器,因此,在从器件中读取CH X0的三个位置和CH X1的三个位置之前,可以对其进行更新。

3 测试内容

ADS8364的测试内容与其他集成电路芯片的测试内容一致,主要可以分为连通性测试、功能测试和参数测试[6~7]。

1)连通性测试

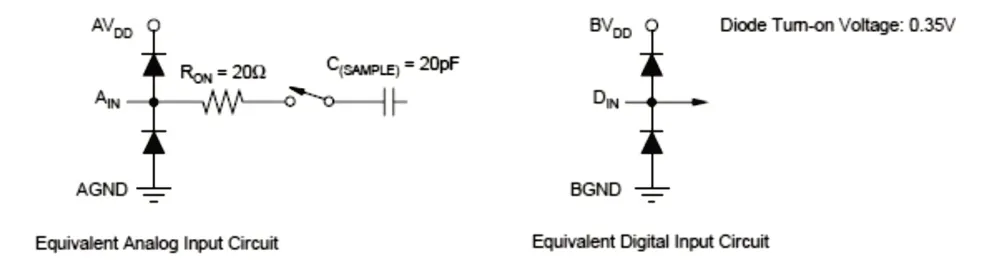

在连通性测试中,我们主要是检测管脚是否有开路(引脚未与内部资源连接)、对地短路、对电源短路等故障[8]。ADS8364的输入管脚的等效电路图如下图所示,在AVDD和BVDD等于0V时,管脚与测试系统的通道正常连接时,驱动小电流可以测得二极管的压降。如果管脚开路或短路,测量结果为0或极值(测试系统的电压钳位设置值)。

图2 ADS8364输入管脚的等效电路

2)功能测试

在功能测试时,我们主要是检测芯片是否能够正常工作,芯片基本的性能能够得到保障。在测试时主要依据芯片的数据测试所描述的功能进行遍历测试。在测试过程中依据芯片功能描述和波形图,用自动测试系统还原芯片工作时各输入管脚的工作状态,并验证各输出管脚的数据。对功能比较复杂的芯片,主要是逐次逐个的对各项功能进行遍历测试[9]。

对ADS8364来说,主要验证ADC转换的正确性和各IO功能的正确性。ADS8364提供了灵活的高速并行接口,具有直接地址模式,周期和FIFO模式。每个通道的输出数据可以16位字或8位的形式提供。

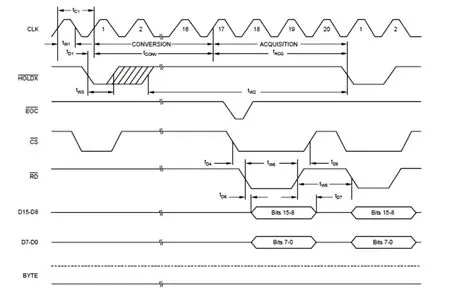

在对ADC设置时,只有正确的时序控制,才能获得正确的转换结果。ADS8364内部的ADC为16位SAR型电容式模数转换器,这种ADC主要由逐次逼近型寄存器、电容式数模转换器(CDAC)和高速比较器组成,并采用二进制搜索算法进行工作[10]。ADS8364是十六位ADC,其输出原码范围应为(h0000至hFFFF)。在工作时,逐次逼近型寄存器首先设置为中间刻度,即h8000,是CDAC的输出VCDAC被设置为VREF/2,芯片的输入模拟电压VIN与VCDAC将进入比较器进行比较,VIN大于VCDAC时,比较器输出高电平,VIN小于VCDAC时,比较器输出低电平。比较的结果存入芯片的输出寄存器的最高位(MSB)。根据比较结果,随后的SAR将被设置为hC000或4000,相应地CADC的输出值被设置为3*VREF/4或1*VREF/4,VIN再次与VCDAC进行比较,比较结果存入次高位。依次内推,完成16次的比较过程。最后,芯片从输出寄存器中读取转换结果,在输出管脚中显示出来。从原理分析容易看出,该种ADC是一位一位比较,则每个时钟周期只能比较一次,N位则需比较N次。因此,对16位的ADS8364来说,其转换时间至少为16个周期。另外,每次转换结束后CDAC的电容的充电时间至少为800ns。保证了这两个时间参数,才能保证采样结果的正确性。ADS8364工作时序如图3所示。

图3 ADS8364的工作时序

3)参数测试

参数测试用于验证芯片指标是否符合器件手册的要求。在参数测试之前,往往要将芯片设置在指定的工作状态。只有芯片的功能测试正确了,参数测试才有意义[11]。ADS8364的参数测试主要分为ADC参数测试、数字IO参数测试和电源电流测试。

ADC的参数主要有静态参数和动态参数之分。静态参数一般在低频下进行测试,而动态参数在相对高频的情况下进行测试。ADC的静态参数一般包括INL(Integral Nonlinearity,积分非线性)、DNL(Differential Nonlinearity,差分非线性)、满量程误差、增益误差等[12~13],一般通过输入低频斜波进行测试。ADC的动态参数与ADC的输入信号有关,并且它们的影响在更高的频率下也很重要。其参数主要有THD(Total Harmonic Distortion,总谐波失真)、SNR(Signal Noise Ratio,信噪比)等。一般通过输入高频正弦波进行测试。

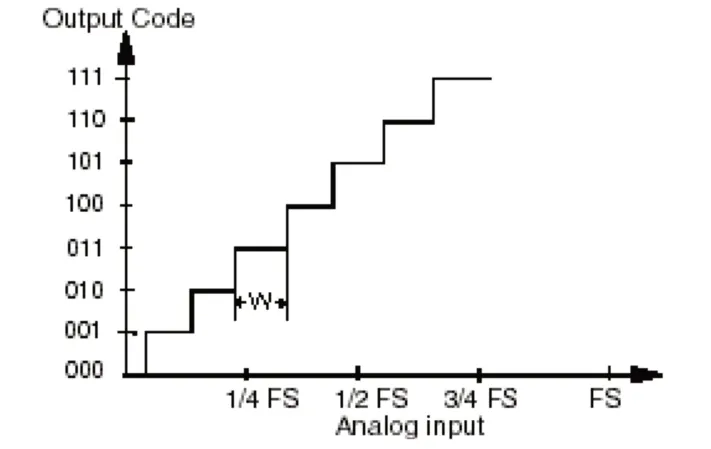

微分非线性是指实际传递阶跃电压与理想阶跃电压之间的差值[14]。如图4所示,对理想的ADC来说,ADC的每个输出码所能转换的电压范围宽度应该都是一致的,理想宽度均为Vwideal。但实际上,每个码值的宽度Vwn与理想值有变差。若码值n对应的宽度为Vwn,则该码值对应的DNL为Vwn和Vwideal之差。积分非线性为所有DNL的总和[15]。

图4 ADC的转换曲线

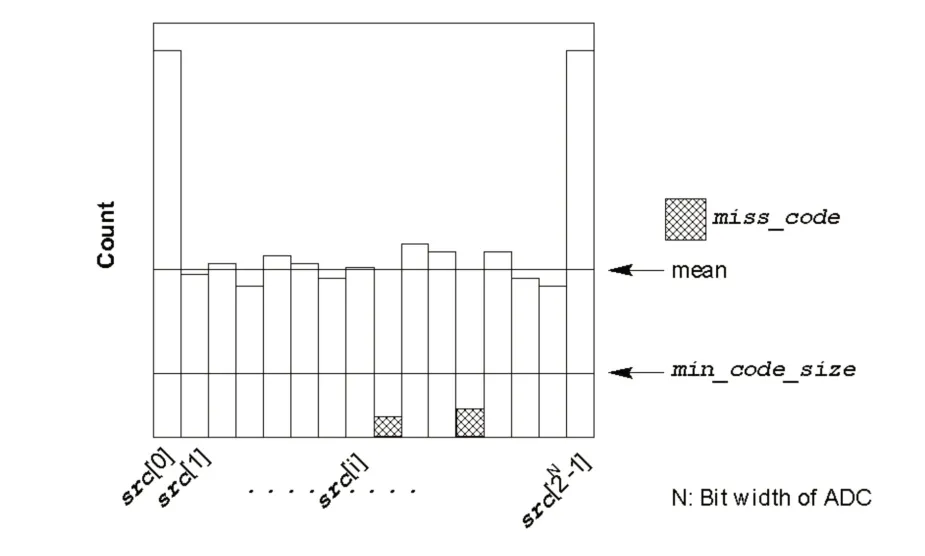

本文采用码密度直方图法来测试ADC的非线性参数。由自动测试系统提供低频周期斜波信号,经ADC采样后输出一系列码值,每个码值出现的次数称之为码密度。对理想情况下,每个码值出现的次数应该是相同的,但由于微分非线性误差的存在,每个码值出现的次数不同。以码值为横坐标,码密度为纵坐标,绘制的图形为码密度直方图,如图5。根据码密度直方图,通过计算可以估计出ADC静态参数的值。

图5 码密度直方图

4 程序设计

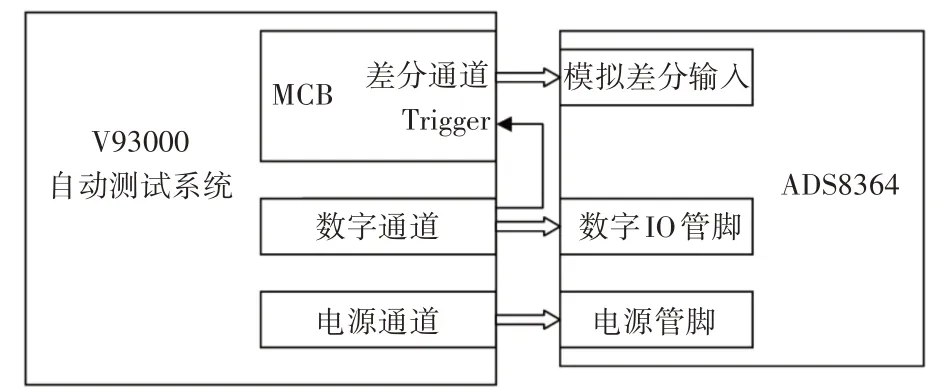

本文中ADS8364的测试在V93000自动测试系统上进行测试。硬件设计方案如图6所示。V93000的MCB模拟板卡可以输出4路差分或单端AWG信号[16]。四路差分通道通过开关多路复用,连接到ADS8364的差分输入管脚。ADS8364的数字输入/输出管脚连接到V93000的数字通道。ADS8364的电源管脚连接到自动测试系统的DPS电源通道。

图6 ADS8364测试硬件设计方案

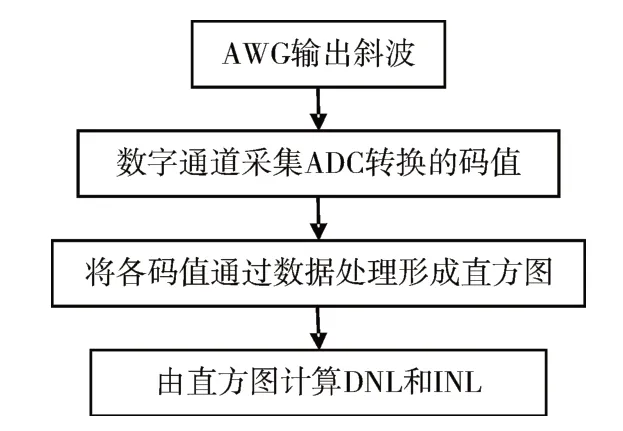

测试程序中,连通性测试、功能测试、IO参数等测试项以V93000测试系统自带模板为基础进行测试。ADC参数测试采用基于C++语言的自定义测试方法API(Application Programming Interface,应用程序编程接口)进行测试。以DNL、INL测试为例,在V93000自动测试系统上测试ADC的流程如下图所示。在V93000中的TestMethod窗口中进行编程,对ADC进行码密度直方图法测试。

图7 DNL、INL测试流程图

1)AWG输出斜波。将ADC的模拟差分输入管脚连接至MCB板卡的AWG差分输出通道。通过设置AWG的LF(低频)通道,使AWG输出低频斜波。

在TestMethod中,其代码如下,将ADC的模拟输入管脚“Ap”连接到MCB的输出通道,在程序中只需连接正向输入通道,负向输入通道自动连接。

Routing.pin(“Ap”).connect(TM::DIFFERNTIAL);

AWG(“Ap”).enable();

2)数字通道采集ADC转换的码值。在V93000的时序文件(timing)中,设置数字输出D15~D0为采集波形模式。在测试向量文件(Pattern)中,设置图形变量(Vector Variable),将测试过程中对D15~D0采集的波形存储到图形变量中。在Test-Method中,执行数据采集的代码如下。

DIGITAL_CAPTURE_TEST(1.0);

3)将各码值通过数据处理形成直方图。

第一步,读取图形变量文件,存储为数组。在TestMethod中设置代码如下,读取波形变量文件capture_variable,将向量变量数据复制到数组中,以便以后进行测试方法处理。

第二步,以ADC输出的数字码及其发生次数为坐标绘制图形,得到直方图histogram。对16位ADC来说,需要设置216=65536个码箱,最小的码箱<1,即为0,最大的码箱≥65535,码箱的数量为65536个。在TestMethod中设置代码如下。

DSP_HISTOGRAM(adc_wave,histogram,1,65535,65536);

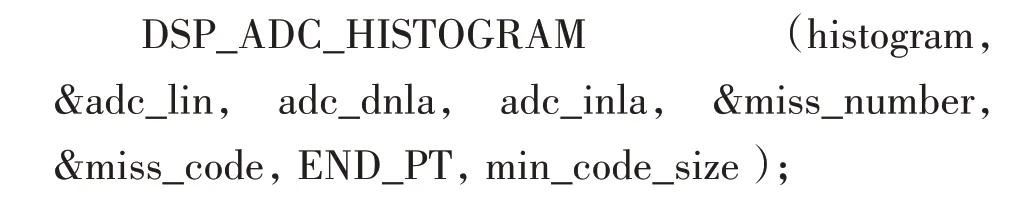

4)由直方图计算DNL和INL。根据直方图先拟合出ADC的输出曲线,再根据输出曲线和每个数字码对应的码密度计算出DNL和INL。

5 测试结果

在V93000测试系统的测试流程文件testflow中调用已编程好的TestMethod文件,并配合正确的时序控制和输入输出电平设置,可以得到ADS8364测量结果,测量结果显示该芯片满足技术指标要求。

6 结语

本文针对模数转换芯片ADS8364,分析了该ADC芯片的内部结构组成,并基于V93000测试系统进行了编程测试,测试结果良好。对其他ADC芯片的测试开发有借鉴意义。