基于CSPI传输协议的自适应均衡器设计

2021-03-02张裕桦徐枫程

赵 斌, 张裕桦, 王 照, 徐枫程*

(1. 华南理工大学 电子与信息学院,广东 广州 510640;2. TCL华星光电技术有限公司,广东 深圳 518107)

1 引 言

由于TFT-LCD显示在尺寸、分辨率和刷新率方面的飞速发展,大量信号的快速传输要求使得高速串行传输逐渐取代传统的并行传输。CSPI是一种点对点高串行速传输协议,在超高清显示(UHD)中有着优秀的表现[1]。然而随着高分辨率(e.g. 8 K)和高刷新率(e.g. 120 Hz)面板需求的出现,使得串行通道的数据传输速率急速上升。由于趋肤效应和介电损失的存在,高速数据在通过信道(e.g. FR-4)时,不可避免地出现幅值衰减和码间干扰(ISI)等问题。为了解决这种与频率强相关的信号损失问题,发送器Tx(Transmitter)使用预加重技术[2-3](Pre-emphasis)提前对可能遭受损失的频段进行增强,接收器Rx(Receiver)使用均衡器技术[4-5](EQ)对接收信号中已损失的频段进行补偿。通常来说,二者的增益值是由人根据信号眼图质量手动进行更改的。在TFT-LCD调试中,PVT(Process Voltage Temperature)的存在使得相同产品不同个体的最优增益值有差别[6]。因此在大规模制造时,自适应调节将替代手动调节。

在系统层次,针对Rx的自适应设计方法可以被分类为两种:前馈均衡器(FFE)和决策反馈均衡器(DFE)。FFE占用面积和能耗较小,然而由于缺少反馈,均衡器增益也将施加于噪声,系统的信噪比(SNR)变差。DFE可以改善SNR问题,但操作速率被反馈环延时所限制[7]。在信号处理层次,均衡方式可以被分类为两种:连续信号均衡和离散信号均衡。连续信号均衡的实现独立于时钟恢复机制之外,不受其影响[8]。离散信号均衡的实现需要恢复时钟信号参与采样,有高速处理能力。因采样时钟信号是由高速串行信号恢复所得,则由于高频衰减问题,恢复时钟本身的精确性难以确保,均衡器工作不稳定[9]。本文提出把伪随机二进制序列(PRBS)作为训练数据,使用DFE,并以离散信号均衡的方式进行自适应调整的均衡器设计。在Rx至Tx方向架设单向低速通道,在初期无法获得较为精确的时钟信号时告知Tx提升预加重增益,由此解决离散信号均衡方式中恢复时钟不精确带来的问题。

2 信道特性

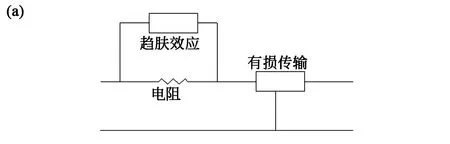

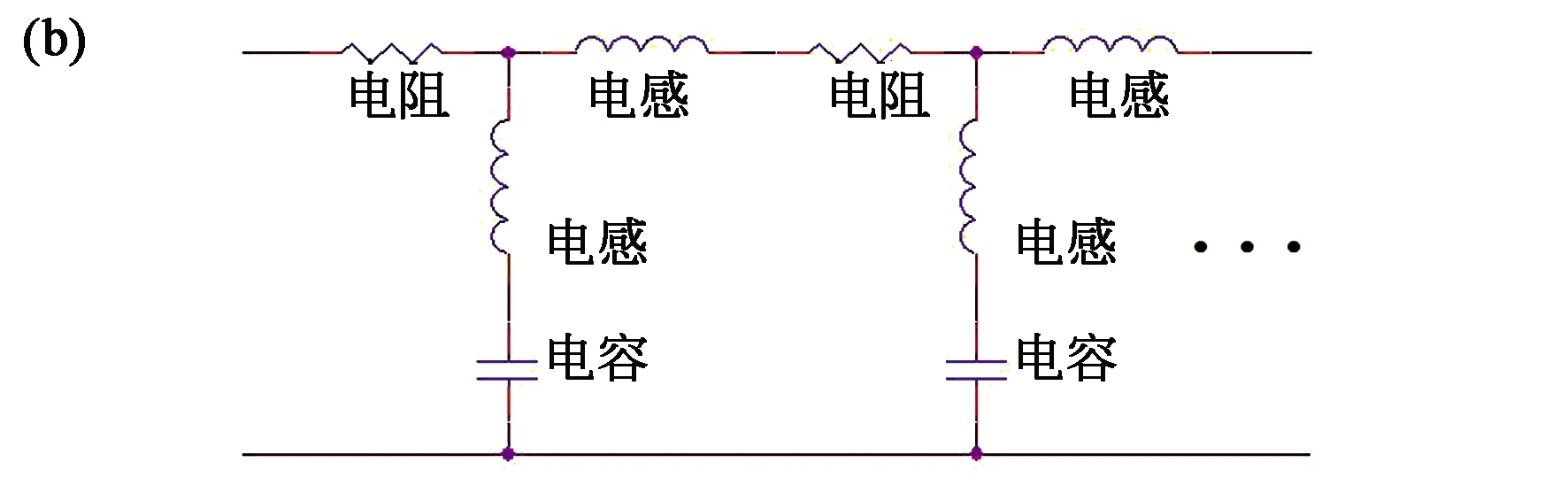

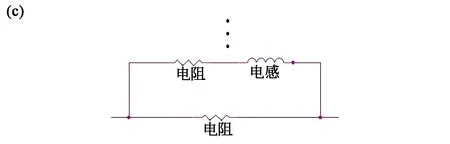

为了量化信道对信号的幅值衰减作用,必须先对信道本身的特性有所了解。图1为传输模型。

图1 (a) 传输模型;(b)有损传输模型;(c)趋肤效应模型。

在信道(e.g. RG-58,FR-4)上的信号损失取决于信号的频率和信道的长度,高频下损失函数由式(1)表示[10]:

(1)

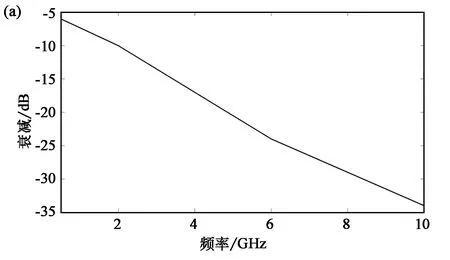

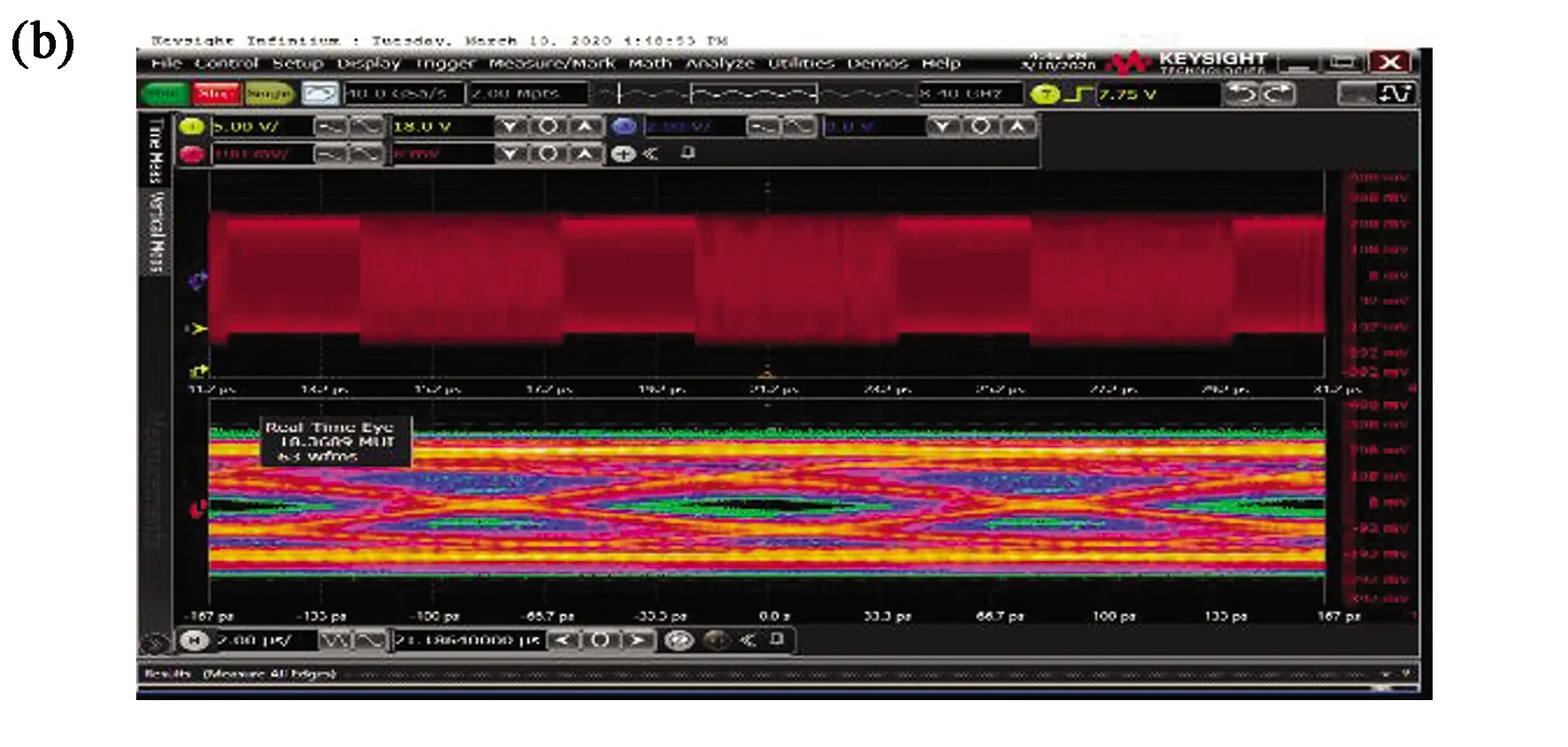

其中Loss(f)表示损失函数,k表示趋肤效应系数,l表示信道长度,f表示信号频率。信号在信道长度为3 000 mil的FR-4板上的衰减如图2(a)所示。对于工作频率在1.5 GHz的信号,衰减为8 dB。如图2(b)所示,此时眼图质量差,Rx端不足以准确还原信号。

图2 (a) 3 000 mil FR-4下的信号衰减;(b)1.5 GHz工作频率下的眼图。

3 自适应均衡器设计方案

3.1 自适应均衡器架构

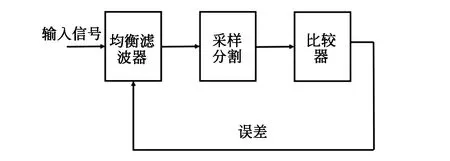

自适应均衡器的总体设计如图3所示。均衡滤波器起到高频增益的作用;采样分割负责将经过增益的信号转化为标准二进制代码输出[11];比较器通过比较实际输入与理想值,计算误差。比较器控制反馈回路更新滤波器增益。

图3 自适应均衡器架构图

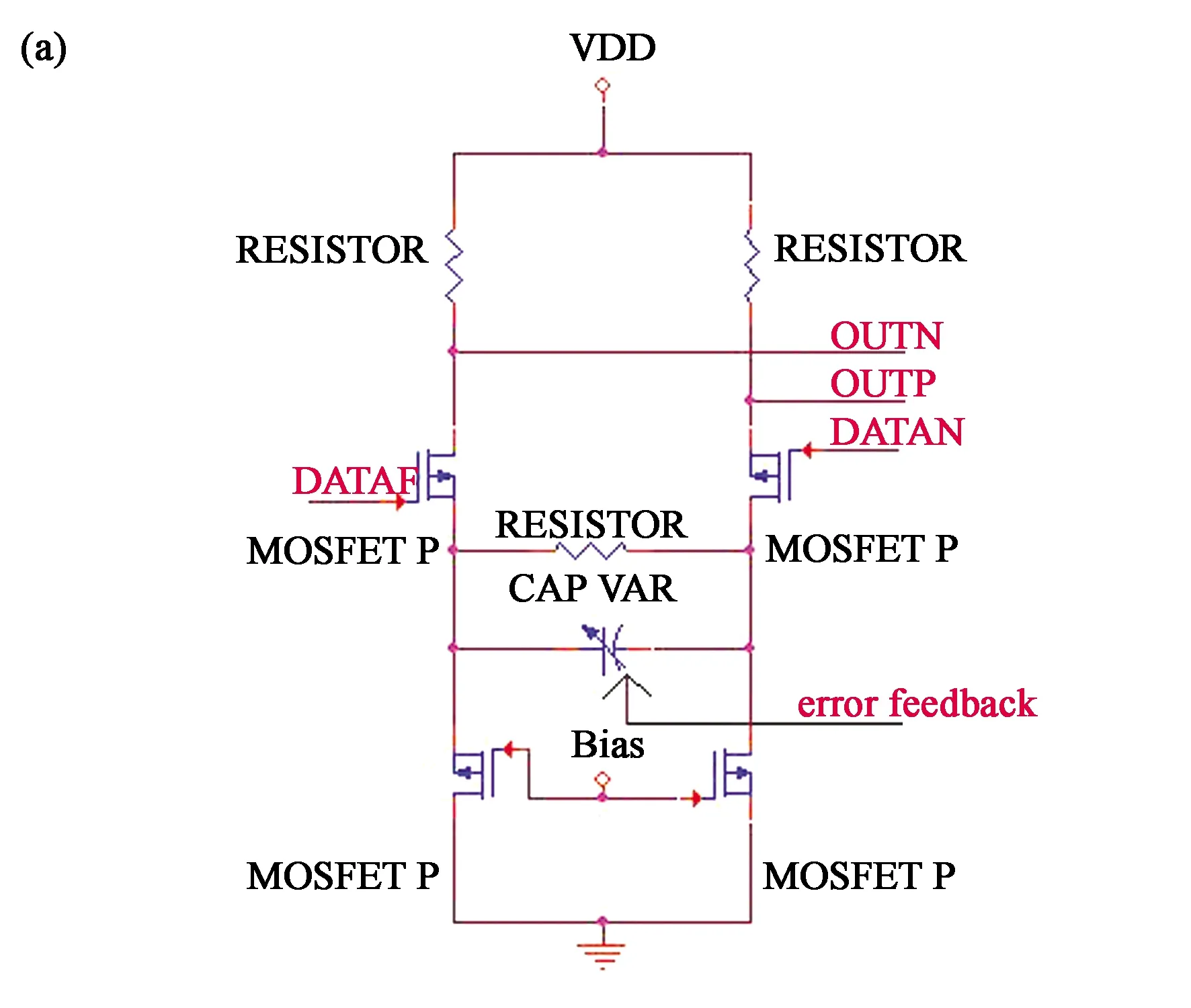

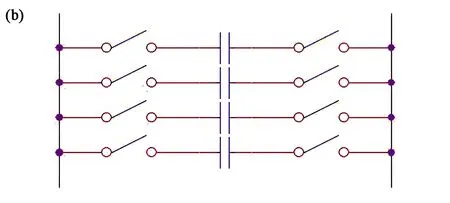

3.2 均衡滤波器

图4(a)为均衡滤波器,为受到衰减的高频信号提供增益。为了获得更大的带宽与增益,采用串联多个均衡滤波器的做法。图4(b)为电容阵列(即图4(a)中的可变电容部分),根据反馈误差转换的档位决定接入电路的电容值。本文采用4 bit~16档位可选机制,每一个档位补偿1 dB增益。

图4 (a) 均衡滤波器;(b) 电容阵列。

3.3 采样与分割

采样时钟信号由Tx端锁相环模块产生,抵消差分信号耦合。信号眼图的中央进行采样,并保持采样结果一段时间直到分割器完成工作。分割器作用与鉴幅器原理相同,使得信号具有较陡峭的上升下降沿,方便比较器获得精确的比较结果。

3.4 比较器

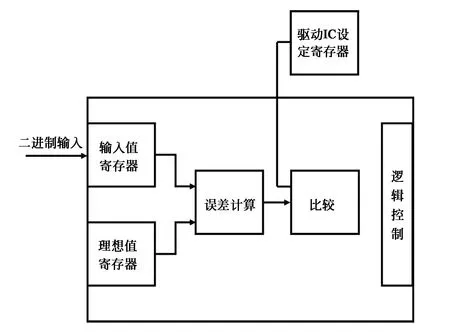

图5 比较器框图

比较器实际为一个数据处理单元,如图5所示。在进行自适应调整期间,Rx接受的数据均为PRBS码,码型已经由生成多项式决定,因此在理想值寄存器中可存入Tx送出数据的理论值。在计算得到实际输入与理想输入的误差后,比较器向驱动IC设定寄存器查询误差阈值。若误差超过设定阈值,则向均衡滤波器发出增加增益档位的需求;若没有超过,也会发出增加档位需求,同时将该档位记录为可用档位。

4 基于CSPI的应用

4.1 系统结构

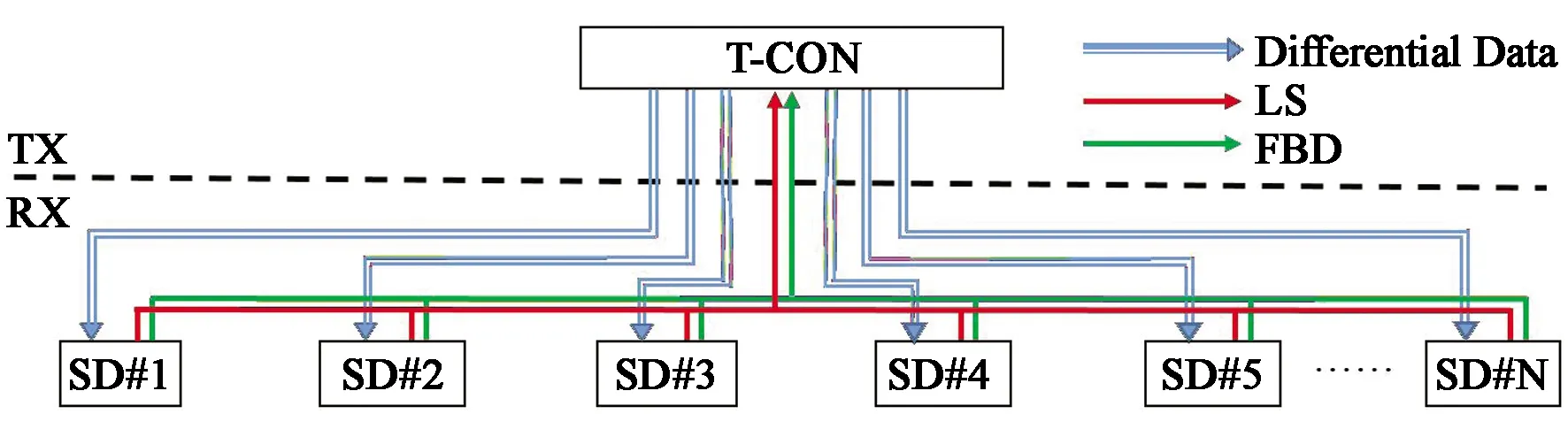

基于CSPI协议的系统架构图如图6所示,自适应设计位于源驱动芯片(Source IC)Rx端。在系统开机时,时序控制器(Tcon)Tx端通过差分信号线DATA P/N向Source IC传输训练协议,source IC依次进行自适应调节。在调节过程中,source IC通过LS信号线与Tcon完成预加重(Pre-emphasis)和均衡器(Equalizer,EQ)的协同调节,通过FBD-Link信号线告知Tcon当前EQ状态。当所有source IC完成自适应调节后,系统进入正常显示模式。

图6 基于CSPI的系统架构图

4.2 系统自适应调节机制

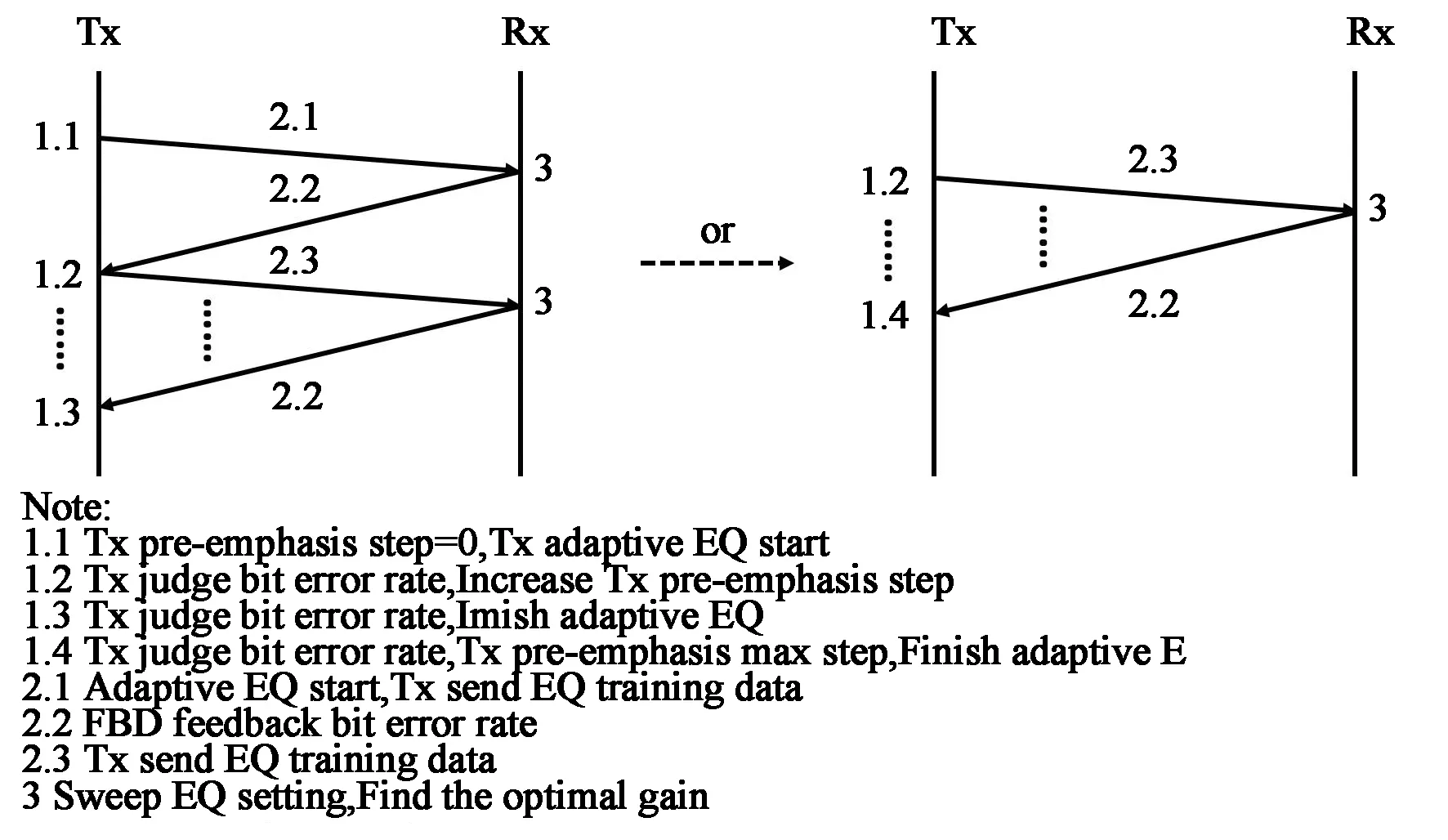

系统自适应调节机制如图7所示。系统的自适应调节包含Tcon到source IC以及source IC到Tcon两种数据发送机制。根据发送数据的主体,系统自适应调节机制又分为训练机制和回传机制。

图7 系统自适应调节机制

4.2.1 训练机制

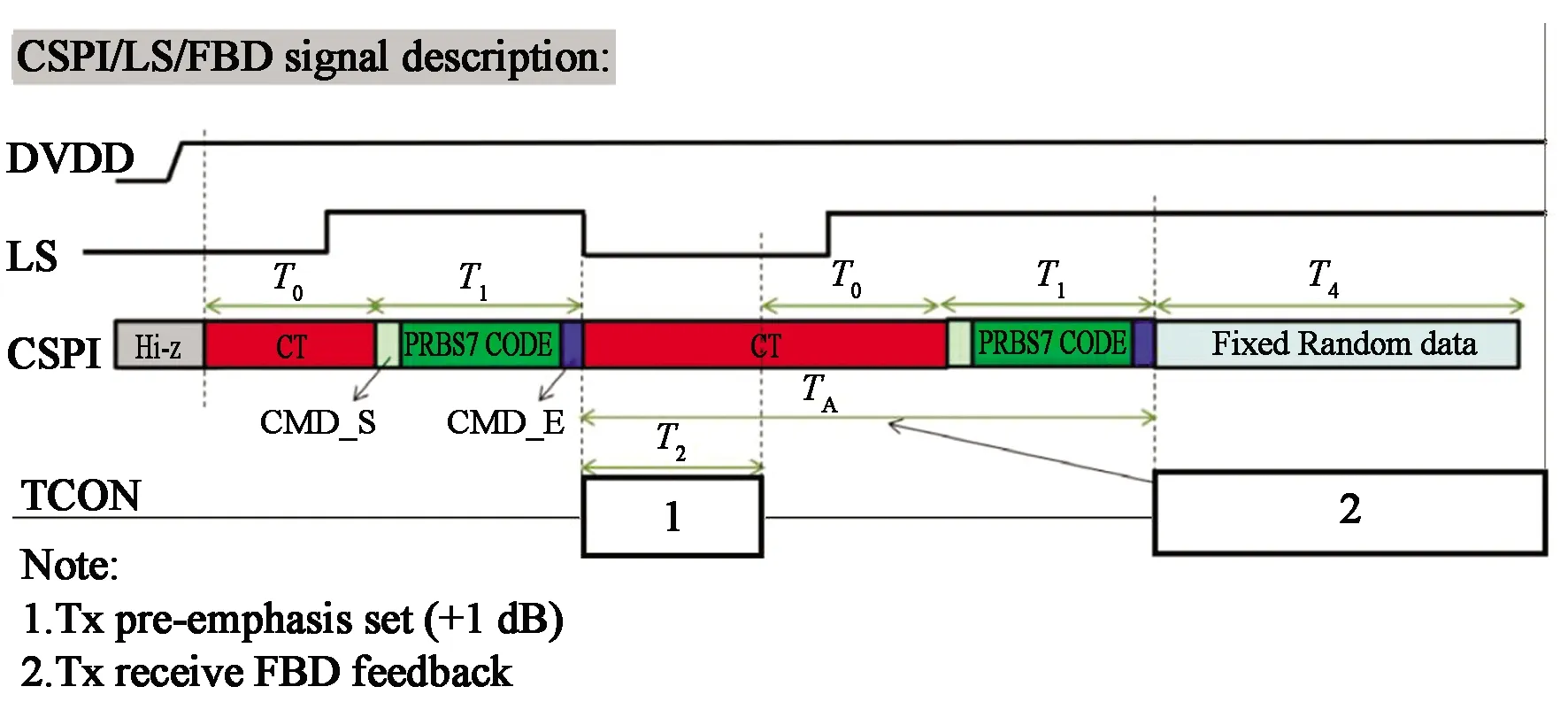

图8是自适应调节训练机制。开机时Tcon通过差分信号线发送CT信号给所有source IC,使其建立内部时钟[1]。成功后,LS信号被拉至高电位,Tcon发送CMD_S信号通知source IC准备接受PRBS码,source IC通过PRBS训练找到最佳EQ设定。如果source IC无法找到任何最佳设定或突然受到外部干扰导致Rx接收状态失锁[1],则将LS拉至低电位,通知Tcon增加预加重,同时重新发送CT。source IC将重复之前步骤直到找到最佳EQ,此时source IC通过FBD-LINK告知Tcon现在的设置档位。Tcon向下一颗source IC重复以上步骤。

图8 训练机制

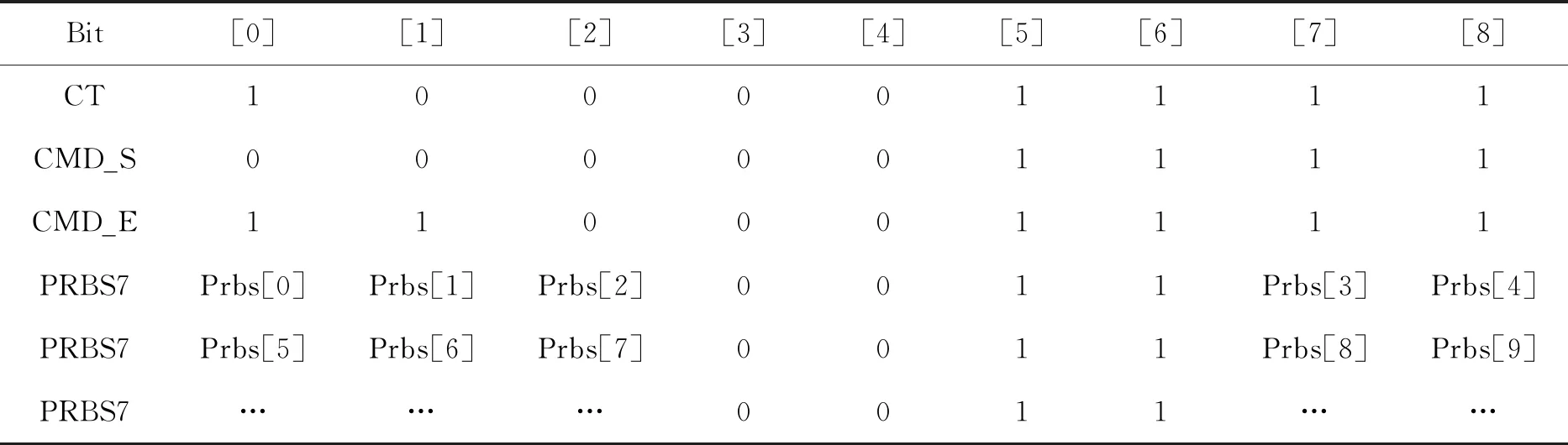

训练码内容如表1所示。由于LS与FBD-LINK存在多个子机复用的情况,如表2所示,对于协议中各段代码的时间长度有最小值的要求, 这样可以保证source IC在训练和回传时留有时间裕量,提高系统的稳定性。其中,T2仅与Tx端相关,无最小值要求。

表1 训练码

表2 训练码最小时间要求

4.2.2 回传机制

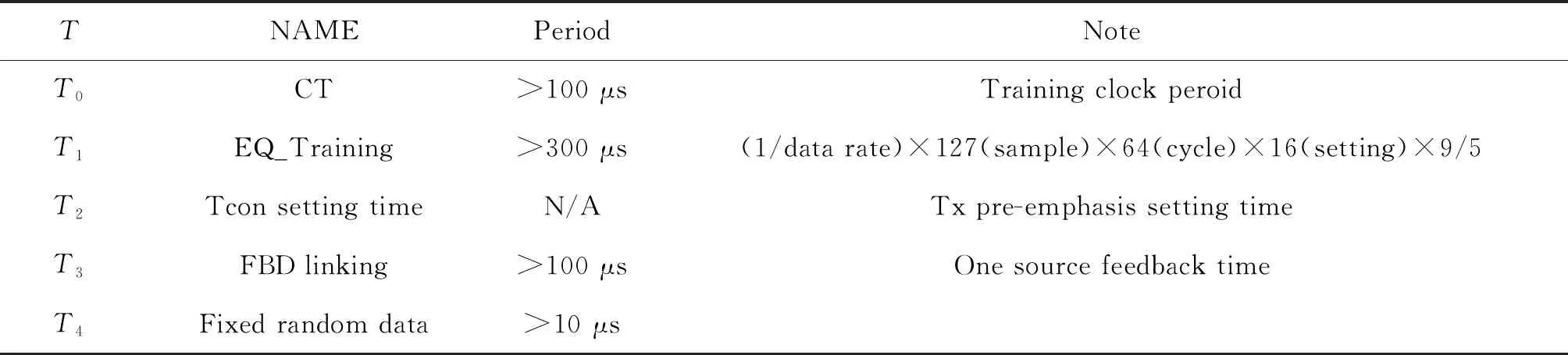

如图9所示,source IC通过FBD-LINK信号线向Tcon回传当前EQ设定的机制。FBD-LINK回传协议由idle、preamble、header、data、end组成。

图9 FBD-LINK回传机制

表3 回传码

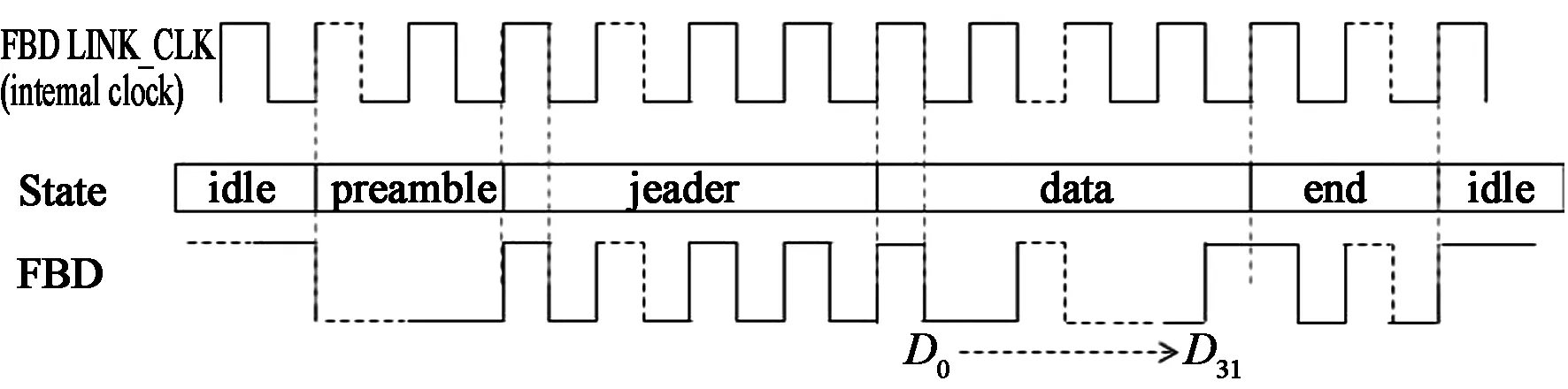

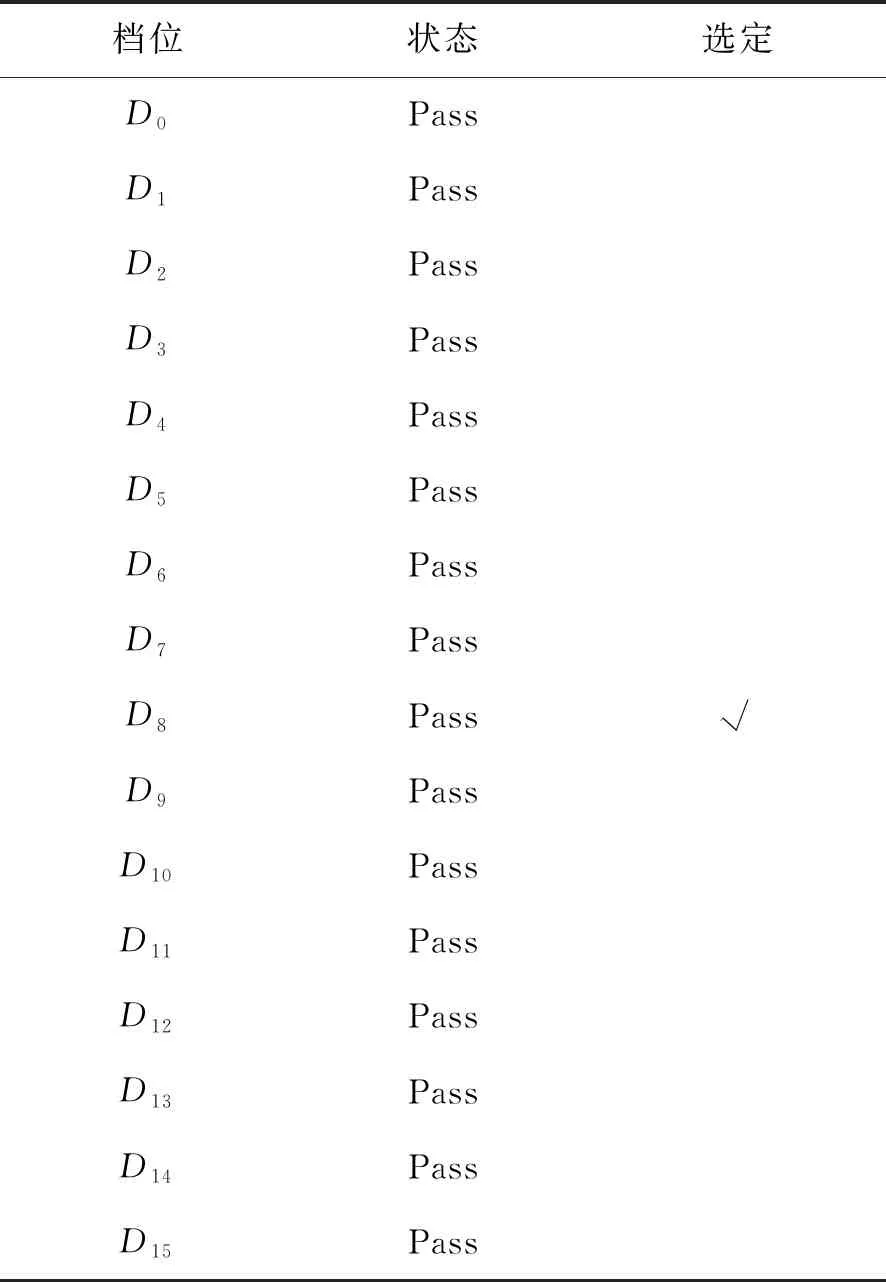

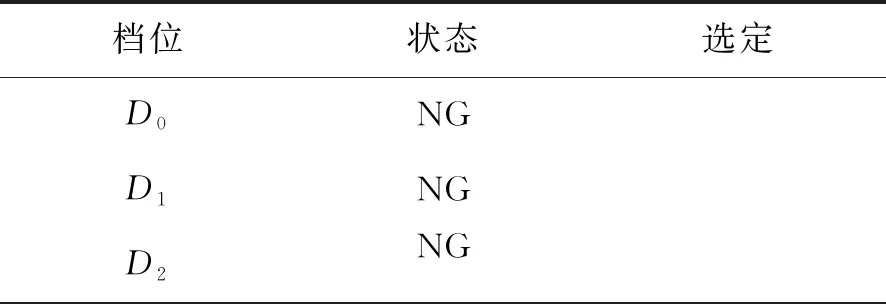

如表3所示,header、data与end采用曼彻斯特编码方式。由于这3个部分可能存在长时间电平不跳变的情况,使用具有自定时功能的曼彻斯特编码可以防止同步时钟的丢失以及低频直流漂移造成的比特错误。Data部分内容决定EQ设定。在32位Data中,前16位用于表示可用EQ设定,17~20位用于表示最终的EQ设定,其余位无内容,默认为0,用于满足FBD最小时间要求。此处,我们选择将可用EQ设定中的中位数作为最终档位,因为增益与信号改善效应的关系可概括成二次项系数为负的二次函数,通常情况下中位数档位最接近拐点。注意,当预加重值与EQ值都为最大值仍不能满足要求时(即无合适档位可选),source IC将默认设置为第8档位。此时表明仅从信号本身进行加强已无法弥补信道带来的损耗,需要同时优化改善信道设计。如表4所示,Data的0~15位每一位对应EQ增益的一个档位。0为不通过(Fail),1为通过(Pass)。

表4 Data与EQ联系

FBD-LINK有两个作用:(1)帮助判断自适应机制是否正常工作。在实际系统中,无法对IC内部的Rx端对经过AEQ后的信号进行测量。因此需要借助FBD-LINK的回传机制来判断系统设计的有效性。若Tx端接收不到回传值或者接收到的回传值内容不符合设计原理要求,则证明系统设计失效。(2)下一颗D-IC自适应调节的使能。LS为多子机复用,使用同一根LS信号线的source IC无法同时进行EQ训练,否则存在总线竞争。因此,对于one-by-one训练的系统来说,FBD-LINK起到告知Tx当前IC已完成训练需要启动下一颗IC训练的作用。

5 实验结果与分析

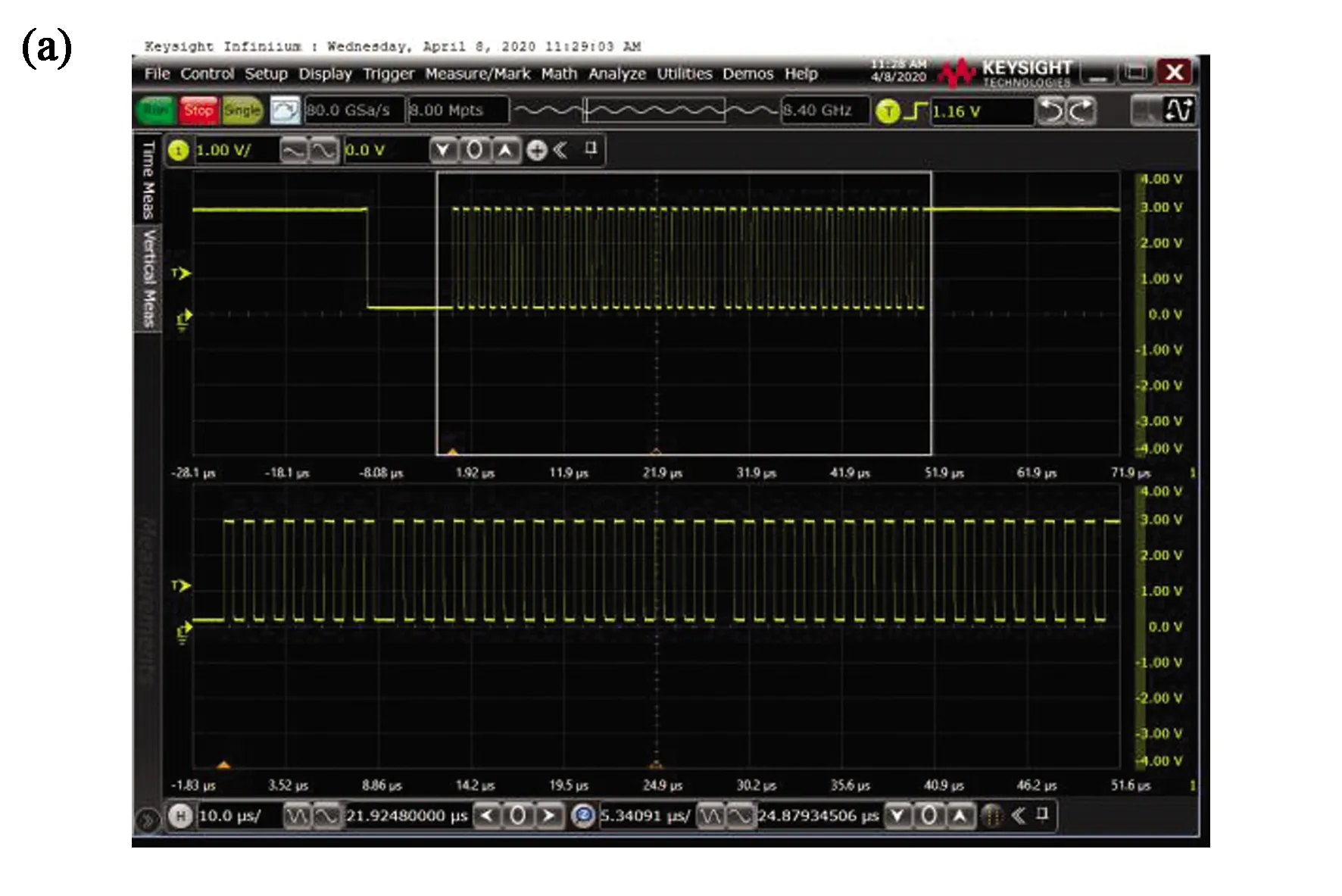

如图10所示,分别选取信号走线最短和最长的两端D-IC进行FBD-LINK回传信号读取。根据系统设计原理,A端信道传输距离最短,信号衰减低,FBD-LINK返回的EQ设定中,较小的档位也能通过,通过的档位数较多,最后在通过档位中选取中位数作为EQ设定。B端信道传输距离最长,信号衰减高,FBD返回的EQ设定中,只有一定增益以上的档位可以通过,通过的档位数较少,最后在通过档位中选取中位数作为EQ设定。

图10 PCB板量测

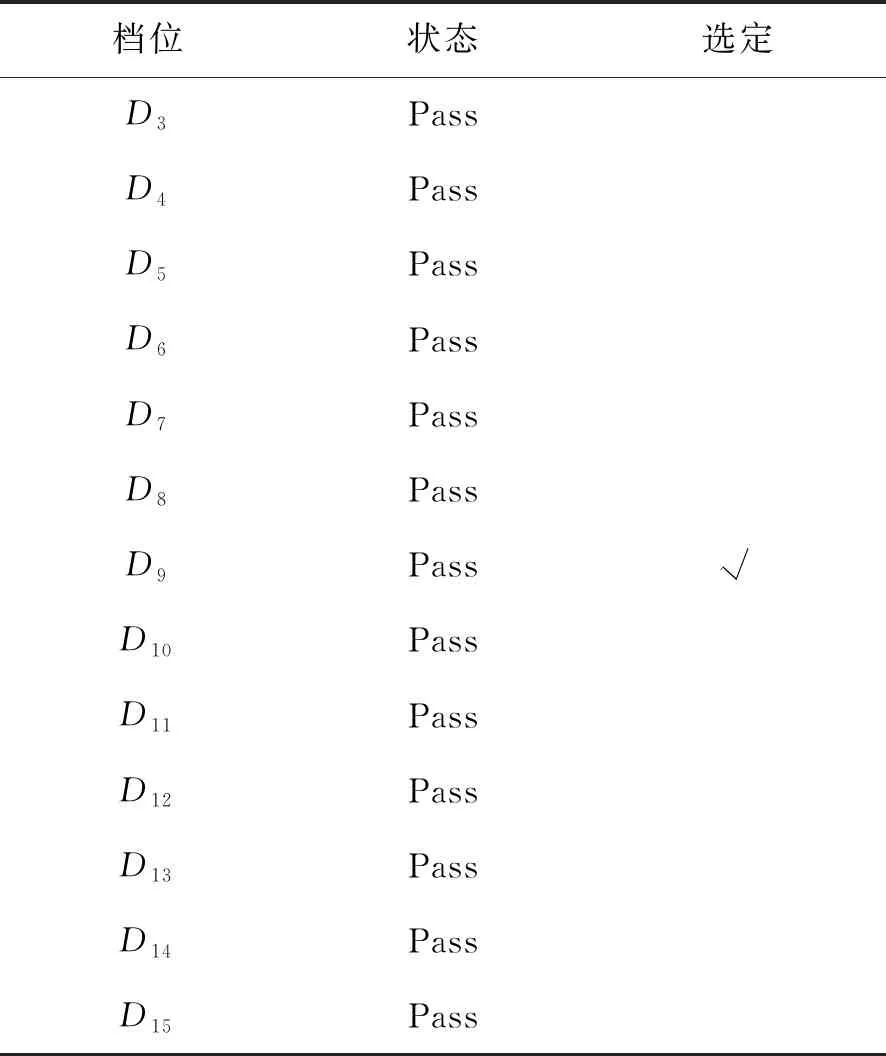

图11(a)、(b)分别为D-IC A和B位置量测的FBD反馈信号。将其中Data的内容转化为表5与表6。A端所有档位通过,设定值为第9档。B端4~16档通过,设定为第10档。实测档位选择符合设计理论,证明自适应均衡器工作正常。

图11 (a) D-IC A FBD信号量测;(b) D-IC B FBD信号量测。

表5 A端EQ档位状态及选择

表6 gB端EQ档位状态及选择

续 表

6 结 论

本文提出一种基于CSPI协议的自适应均衡器设计。在Rx设计层面,DFE的引入消除了噪声带来的影响,离散信号处理的均衡方式改善了反馈引入后的延时效应。在系统层面,加入FBD-LINK机制以解决对信号采样时采样时钟精确性的问题。最后在实验中通过检查Tx端的回读值证明了系统的有效性。该设计补偿了高频信号的衰减,对于Rx端准确恢复高速信号有重要意义。