挠性印制板高精度阻抗设计影响因素研究

2020-07-18黄建娣彭罗平肖治理

黄建娣 彭罗平 肖治理

(景旺电子科技(龙川)有限公司,广东 河源 517362)

0 前言

要使印制电路板(PCB)传输信号保持完整,并得到可靠、精确的传输,对PCB工艺流程上所使用的材料及其设计搭配非常严格。挠性印制板(FPC)的特性阻抗受材料及设计搭配复杂许多因素影响,如线宽、覆盖膜厚度、PI(聚酰亚胺)厚度、不同电磁膜、不同参考层等一种或多种材料和设计搭配等,阻抗难以精确管控。现通过试验不同参考层相同线宽、参考层相同不同线宽、同等规格不同供应商基材、不同基材PI厚度,以及不同品牌型号屏蔽膜、不同覆盖膜胶厚等因素对阻抗的影响,为FPC高精度阻抗设计提供最佳建议方案。

1 试验方法

1.1 设备与材料

设备:安捷伦阻抗测试仪、二次元、金相显微镜1000倍。

材料:挠性覆铜板(铜箔:12 μm、双面无胶ED铜,聚酰亚胺(PI)厚度:12.5 μm/20 μm/25 μm)、电磁膜(型号A/B/C/D)、覆盖膜(黄色PI:12 μm,粘合剂:15 μm/20 μm/25 μm)。

1.2 试验流程

开料→钻孔→镀铜→图形→覆盖膜→沉金→电磁膜/钢片(各工序正常参数,图形蚀刻量为20 μm)

1.3 试验方法

(1)参考层实铜相同,不同线宽的影响;(2)参考层的网格相同,不同线宽的影响;(3)参考层网格,线宽相同,不同胶厚覆盖膜的影响;(4)参考层网格,线宽相同,不同型号电磁膜影响;(5)参考层网格,线宽相同,不同供应商基材特性影响;(6)参考层网格,线宽相同,不同基材PI介质层影响;(7)参考层网格,线宽相同,阻抗线面不同背胶方式钢片影响;(8)线宽相同,不同参考层影响。测试项目设计方案见表1所示。

2 结果与讨论

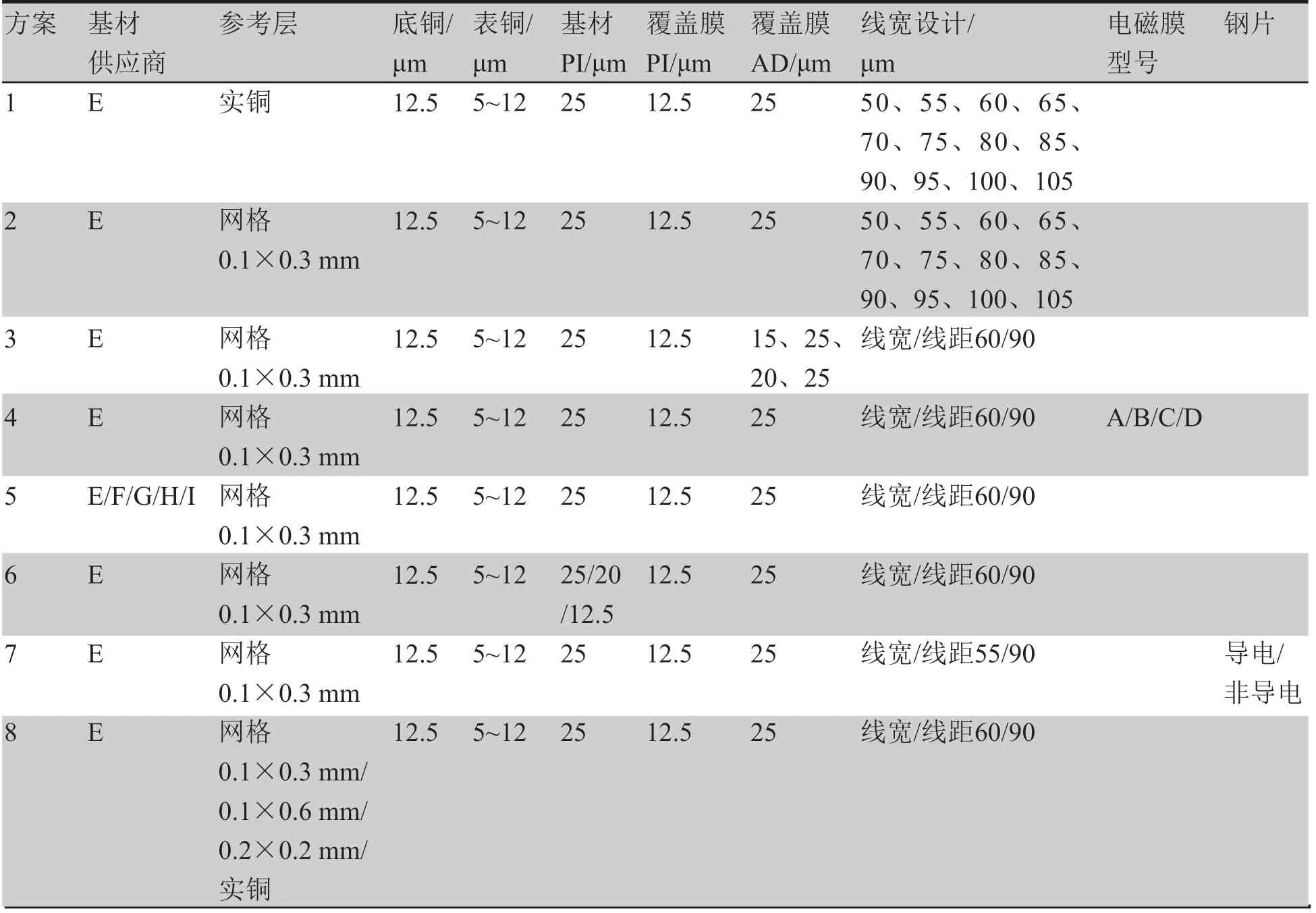

2.1 参考层实铜,不同线宽对阻抗的影响

参考层实铜,不同线宽阻抗试验结果如图1所示。参考层为实铜设计时,线宽对阻抗的影响约1 μm线宽=0.7Ω阻抗变化值。贴膜后阻抗比贴膜前平均约小10Ω,且线宽越大差值越小。沉金后沉金前约小3.4Ω,且线宽越大,沉金对阻抗的影响越小,贴电磁膜后比贴电磁膜前平均约小18.9Ω,且线宽越大,电磁膜的影响越小。贴电磁膜后与蚀刻后的光板阻抗平均约小33Ω,且线宽越大,阻抗差值越小(见图1所示)。

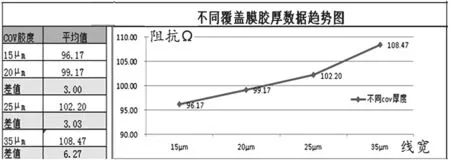

表1 测试项目设计方案

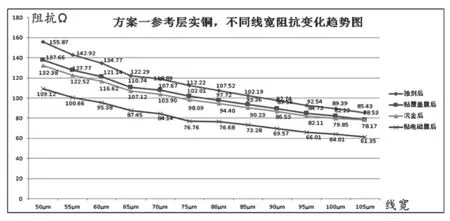

2.2 参考层0.1 mm×0.3 mm网格,不同线宽对阻抗的影响

参考层0.1 mm×0.3 mm网格,不同线宽阻抗的试验结果如图2所示。参考层层为网格时,线宽对阻抗的影响约为1 μm线宽=1Ω阻抗变化值。对比得知,贴膜后阻抗比贴膜前平均约小19Ω,且线宽越大差值越小。沉金后比沉金前约小3.5Ω,且线宽越大,沉金对阻抗的影响越小。贴电磁膜后比贴电磁膜前平均约小24Ω,且线宽越大,电磁膜的影响越小。贴EMI(电磁膜)后的半成品与蚀刻后的光板阻抗平均约小47Ω,且线宽越大,阻抗差值越小。

图1 参考层实铜,不同线宽阻抗Ω数据趋势图

图2 参考层网格,不同线宽阻抗数据趋势图

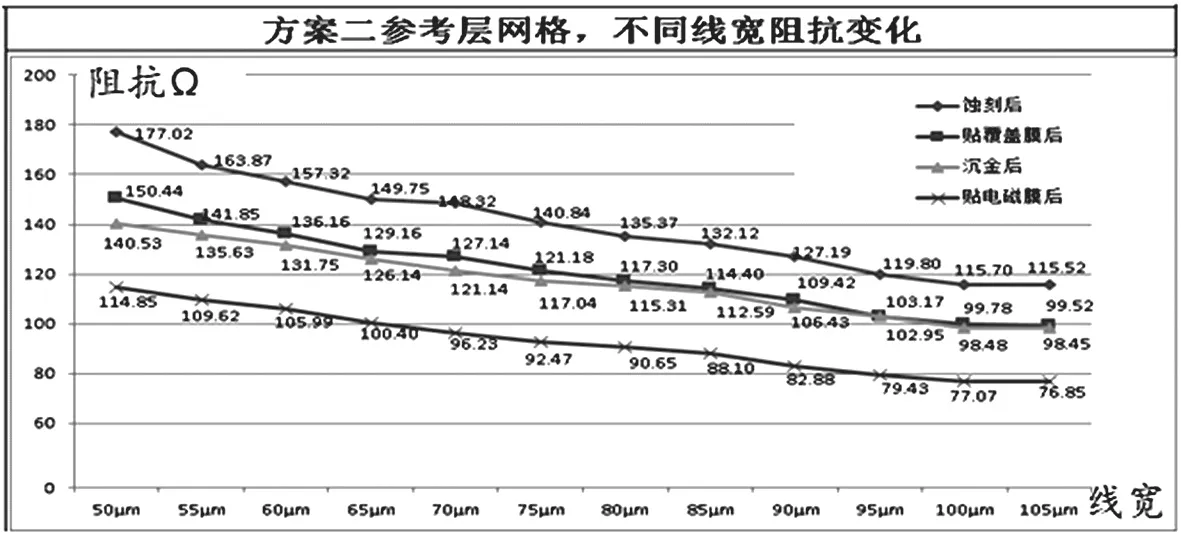

2.3 参考层网格,线宽相同,不同胶厚覆盖膜的试验

参考层网格,线宽相同,不同胶厚覆盖膜的试验结果如图3所示。在参考层网格设计时,不同厚度的覆盖膜搭配相同的电磁膜,随着覆盖膜胶厚的增加阻抗值会越来越大,差异值为5 μm≈3Ω,覆盖膜胶厚度与阻抗成正比。

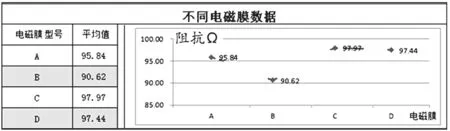

2.4 参考层网格,线宽相同,不同型号电磁膜的试验

参考层网格,线宽相同,不同型号电磁膜的试验结果如图4所示。不同型号电磁膜对阻抗影响不同,其中C≈D≤A≤B。

图3 参考层网格,不同覆盖膜胶厚度阻抗趋势图

图4 参考层网格,不同电磁膜型号阻抗趋势

2.5 参考层网格,线宽相同,不同铜箔介质层的测试

参考层网格,线宽相同,不同供应商基材特性测试结果如图5所示。对比同等规格供应商基材阻抗数据,蚀刻后不同供应商阻抗H≥E≥G≈I≈F。从数据上分析不同材料供应商之间,铜箔厚度12 μm双面无胶ED铜 基材不同供应商,各家略有差异,差异3~5Ω。目前我们使用的常规无胶主要是TPI材料,TPI材料介电常数一般≤4,实际上是在3.1~3.3,同等规格普通PI系,影响在3~5Ω。

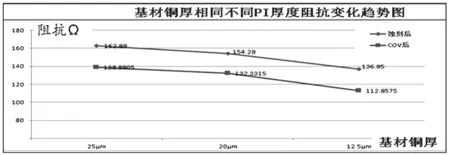

2.6 参考层0.1×0.3 mm网格,线宽相同,不同基材介质层测试

参考层0.1 mm×0.3 mm网格,线宽相同,不同基材PI厚度测试如图6所示。不同基材PI厚度阻抗数据对比25 μm≥20 μm≥12.5 μm从数据分析得出,基材PI介质层厚度是影响阻抗重要因素,增加介质层厚度可以提高阻抗,阻抗与材料介质层厚度成正比,PI越厚阻抗越大(见图6所示)。

2.7 参考层0.1×0.3 mm网格,阻抗线面不同钢片背胶方式测试

参考层0.1 mm×0.3 mm网格,不同钢片背胶方式测试结果如图7所示。从数据可以看出导电胶钢片对阻抗的影响大于非导电胶钢片,当阻抗线面贴钢片,非导电胶阻抗比导电胶阻抗大,参考层网格0.1 mm×0.3 mm时,1 μm约影响约1Ω。

2.8 测试不同参考层,相同线宽设计,参考层对阻抗及阻抗线背面贴EMI的影响

测试不同参考层,相同线宽设计,参考层对阻抗及阻抗线背面贴EMI的影响,如图8所示。

阻抗与参考层越大,阻抗越大,参考层阻抗关系:实铜≤0.2 mm×0.2 mm≤0.1 mm×0.3 mm≤0.1 mm×0.6 mm≤0.1 mm×0.9 mm。

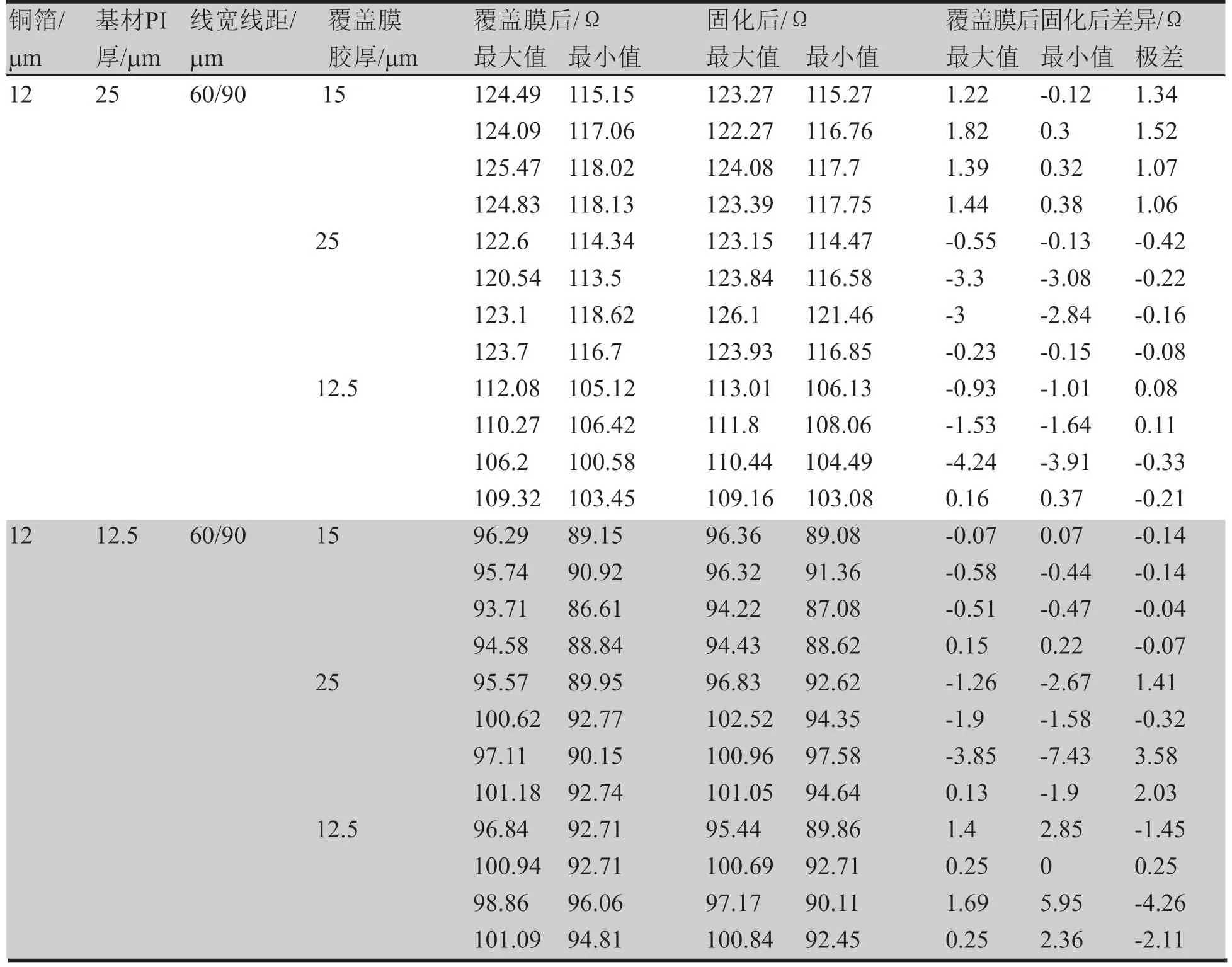

2.9 覆盖膜快压后与固化化差异

相同铜箔,不同基材PI厚度匹配不同覆盖膜胶厚,快压后与固化后阻抗变化测试,如表2所列。在同等厚度铜箔下,不同厚度覆盖膜下降的阻抗值无差异。两种基材贴覆盖膜后与固化后阻抗无太大变化。

图5 双面无胶ED不同供应商基材阻抗变化趋势图

图6 基材铜厚相同不同PI厚度阻抗变化趋势图

3 结论

图7 0.1 mm×0.3 mm网格不同钢片背胶方式

图8 相同线宽,不同参考层阻抗变化

表2 覆盖膜快压后与固化后差异测试

通过上述试验和分析,影响阻抗的因素主要有参考层、线宽、铜箔介质层、铜箔PI厚度、覆盖膜胶厚,阻抗线面有无EMI,钢片/非钢片等,影响阻抗因素关系:阻抗线面电磁膜≈阻抗线面导电钢片≥阻抗线面非导电钢片>参考层>铜箔PI厚度高>覆盖膜胶厚>线宽>介质层(普通PI系)。精度FPC阻抗在设计时需同时考虑以上因素进行阻抗线匹配设计。

(1)铜箔厚度、介质层、PI厚度、覆盖胶厚、参考层相同时,每增加1 μm线宽,减少1 Ω阻抗进行补偿。线宽与阻抗成反比。

(2)铜箔厚度、介质层、PI厚度、覆盖胶厚、参考层相同时,导电钢片比非导电钢片小10 Ω,导电钢片阻抗线宽需比非导电钢片设计小10 μm。

(3)铜箔厚度、介质层、PI厚度、覆盖胶厚、参考层网格越大,阻抗越大。

(4)铜箔厚度、介质层、PI厚度、覆盖胶厚、参考层网格越大,覆盖膜胶厚越厚,实铜阻抗比0.1×0.3网格偏小。

(4)基材PI越厚,阻抗越大。增加基材PI厚度,可以增加阻抗。

(5)不同基材、不同胶厚快压后与固化后无差异,图形蚀刻后模拟流程仿成品快压后测试阻抗,通过蚀刻速度调整阻抗线宽,管控成品。