基于Spartan-6的微结构探测器APV25数字化系统设计

2018-05-03李兴隆胡守扬周静智宇陈雷刘雯迪赵明锐李沛玉李笑梅

李兴隆,胡守扬,周静,智宇,陈雷,刘雯迪,赵明锐,李沛玉,李笑梅,2

基于Spartan-6的微结构探测器APV25数字化系统设计

李兴隆1,胡守扬1,周静1,智宇1,陈雷1,刘雯迪1,赵明锐1,李沛玉1,李笑梅1,2

(1. 中国原子能科学研究院 核数据重点实验室,北京 102413; 2. 中国科学技术大学 核探测与核电子学国家重点实验室,合肥 230026)

为满足微结构气体探测器多通道信号高速读出的需求,文章基于现场可编程门阵列(FPGA)Spartan-6设计了128通道前置放大芯片APV25的数字化系统。该系统中,APV25输出的串行模拟信号经模/数转换芯片ADS5242进行模/数转换,由Spartan-6接收、解串、缓冲和打包后,经千兆以太网传送至计算机进行存储和分析。经测试,该系统可实现APV25的最大采样速率280kHz,基线噪声低至716e-。输入电荷量低于75000e-时,电荷响应线性良好。由于APV25的抗辐射特性,该系统有望用于空间多通道辐射探测系统。

APV25芯片;Spartan-6;数字化系统;千兆以太网;硬件设计

0 引言

核辐射探测器是人们认识核辐射的“眼睛”,其多以电信号输出,需专用核电子学电路进行放大滤波等处理。APV25是一款128通道集成的模拟前置放大电路芯片,可对探测器输出的信号进行前置放大和滤波等处理;它为大型强子对撞机(LHC)上的紧凑μ子线圈(CMS)探测系统中的硅微条探测器设计[1],具有较强的抗辐射性能,也可以应用到GEM等微结构气体探测器的多通道信号读出中[2]。APV25将128道模拟信号串行输出,国外RD51合作组和意大利国家核物理研究院(INFN)分别为其设计了SRS(scalable readout system)和MPD(multi-purpose digitizer)2套数字化系统[3-4],国内则有中国科技大学设计的多通道读出电子学系统[5],三者皆采用了现场可编程门阵列(FPGA)控制高速模/数转换芯片(ADC)的方案。这主要得益于FPGA开发迅速、配置灵活的特点。中国原子能科学研究院核物理研究所中高能物理组(作者所在实验室)实际测试了MPD V3.0系统,其采用VME总线传输数据,信号触发率上限为3kHz,远低于APV25的理论触发率极限280kHz,这给高计数率应用带来了一些限制。因此,我们开始自主研究设计数字化系统,以低成本Spartan-6 FPGA为核心,通过采用千兆以太网传输数据,提高触发率。

1 系统结构

如图1所示,该系统主要由APV25前端板、模/数转换板、FPGA板和计算机构成。APV25前端板上载有APV25芯片,主要有稳压供电、输入耦合及保护、温度检测和地址设置等功能。前端板下通过板对板连接器连接至自主设计的背板,其主要作用为供电稳压和接口转换,背板与自主设计的模/数转换板通过单根19芯HDMI A型线缆连接。该线缆同时传输APV25的模拟信号、FPGA对APV25的控制命令、时钟信号和触发信号。模/数转换板上载TI的12位ADC芯片ADS5242以及相应的输入信号缓冲、时钟触发单端信号转差分信号、I2C信号电平转换等电路。模/数转换板板对板连接到黑金(ALINX)设计的Spartan-6 FPGA电路板,板载FPGA XC6SLX45、千兆以太网芯片及时钟电源等电路。FPGA电路板经千兆以太网线连接至计算机的千兆网卡,计算机端采用C语言设计了数据采集软件,通过网络通信发送控制命令并接收数据。

图1 APV25数字化系统结构框图及实物图

2 系统实现

下面将从APV25前端板及背板、模/数转换板、FPGA板及逻辑设计、计算机端程序等4个部分详细介绍该APV25数字化系统。

2.1 APV25前端板及背板

本系统采用了MPD设计方INFN设计的APV25前端板[4],由于接口不同,我们设计了新的背板进行接口转换。考虑到芯片封装会增大噪声,该前端板通过金线键合工艺将APV25芯片裸片直接连接至印刷电路板(PCB),芯片上覆一小块单面覆铜板进行保护和屏蔽。在输入端,探测器的输出信号首先经过静电放电(ESD)保护芯片后,经电容耦合至APV25的信号输入引脚。在输出端,该板通过MOLEX 54722-0304板至板连接器输出经放大、滤波等处理后的模拟信号,同时与FPGA通信,接收时钟信号和触发信号。

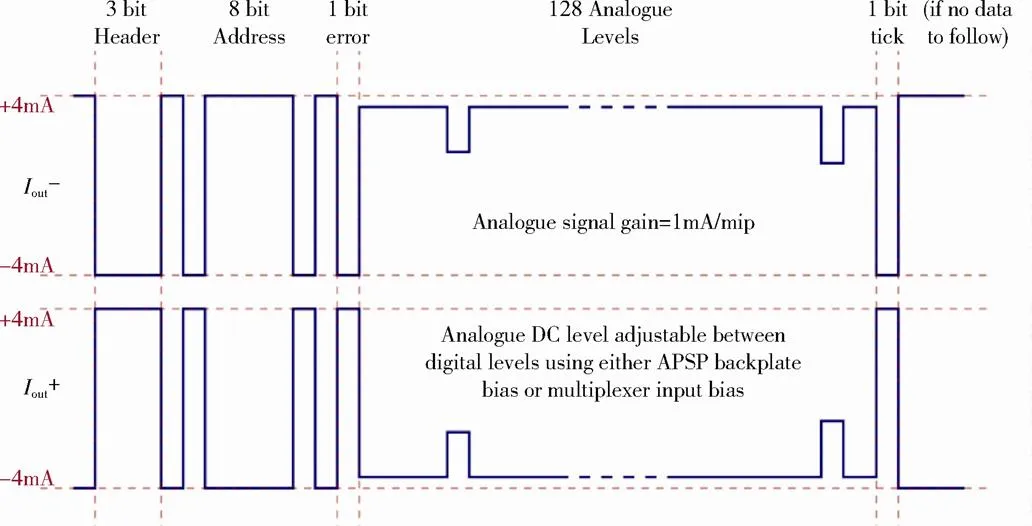

APV25芯片采用0.25μm CMOS工艺制成,其单通道的原理如图2所示。输入信号经增益可控的低噪声电荷灵敏前置放大器放大后,由CR-RC成形电路进行成形滤波,输出达峰时间50ns的脉冲信号,反相器则使得APV25可处理正负脉冲2种输入信号。192单元的模拟管道则以40MHz的频率对成形脉冲进行模拟采样并缓存,模拟脉冲形状处理器使得该芯片可工作于峰采样、卷积和连续3次采样3种模式。APV25的128个通道采用128∶1的时间复用方式输出,故其输出信号仅有1路;输出信号采用类LVDS的差分电流模拟信号形式,故可用一般HDMI线缆进行信号传输,其信号构成如图3所示[1],由起始位、地址位、错误位、128道模拟电平和滴答(tick)位组成,其中128道模拟电平对应各通道信号大小,其他位皆为数字电平。这种时间复用的传输方式,优点是简化了系统连接,缺点是限制了事件率,当工作在峰采样模式时,一次触发将需要140个时钟周期传输信号,即3.5μs,故其最高触发率约为280kHz。

图2 APV25 芯片单通道的原理框图

图3 APV25输出信号结构

背板主要的作用是接口转换和电源稳压,19芯HDMI A接口稳定易用,其中的3组差分信号线(4、5、6;7、8、9;10、11、12)分别用于APV25模拟信号输出、触发信号和时钟信号,15、16线用于APV25与FPGA的I2C通信。背板供电电压为5V,经低噪声线性稳压器LT1965稳压至3.3V,为APV25前端板供电。

2.2 模/数转换板

模/数转换板(图4)的核心器件为TI公司的ADS5242芯片,该芯片为4通道12位ADC,最大采样率为65MSPS,以串行LVDS信号输出转换后的数据,1对差分线传输1个通道的转换结果,简化了系统连接和PCB布线。该系统现连接1片APV25芯片,故只用到了4个ADC通道中的1个。APV25的输出信号为幅值8mA的差分电流信号,该电流信号经板载100Ω电阻端接后,再经低失真差分ADC驱动器AD8138放大2倍,得到的最大输入电压幅值为1.6V。考虑到ADS5242最大差分输入电压为2.03V,AD8138的输出是较为合适的。ADS5242提供共模电压输出引脚VCM,其电压为1.45V,将该引脚连接至AD8138的共模输出电压设置引脚VOCM,如此二者的差分输出/输入便具有了相同的共模电压。

图4 模/数转换板实物图

模/数转换板上采用SN65LVDS9638芯片将来自FPGA的单端触发信号和时钟信号转换为APV25所需的LVDS信号,而FPGA的3.3V I2C信号则经PCA9306D转换至APV25所需的2.5V I2C信号。转换板输入电源电压为5.0V,各电路所需3.3、2.5、1.25V电压则由低噪声低压差线性稳压芯片LT1763提供。在PCB设计上,该板采用4层板结构,顶层为信号层,所有信号线均走该层,中间2层分别是地平面和电源平面,底层为各路电源走线。转换板与FPGA板的连接为双排标准2.54mm插针母座连接,ADC时钟、转换结果输出、复位使能、串行通信以及APV25时钟信号、触发信号、复位信号、I2C通信信号均通过该接口连接至FPGA。

2.3 FPGA板及逻辑设计

该系统所用黑金LX45 FPGA板上载FPGA型号为XC6SLX45,属XILINX最高成本优化的Spartan-6系列,其串行收发器和千兆以太网IP核完全满足数字化系统需求。同时,该板上的RTL8211E千兆以太网物理层芯片和RJ45接口可直接用于与计算机的网络通信。

该系统使用Verilog语言设计了FPGA的逻辑功能,如图5所示,来自ADC的LVDS串行数字信号经Spartan-6的串/并转换器ISERDES2转换为6位并行数据,后经对齐、拼接还原为12位ADC值;这些ADC数据先送入异步FIFO缓存,读出后按用户数据报协议(UDP)打包,加入奇偶校验字节,后经三模以太网介质访问控制层IP核(TEMAC)以GMII接口发送至RTL8211E PHY芯片,最后经6类双绞线传输至计算机千兆网卡。同时,利用FPGA的时钟资源为ADC和APV25提供外部时钟,方便调整时钟相位同步。I2C模块则负责配置APV25工作参数,对ADC的工作参数配置同样采用串行通信。

考虑到APV25输出的信号为40MHz的模拟信号,当APV25工作在最高触发率280kHz左右时,模拟信号帧连续输出,因此经12位ADC转换后,最大有效数据速率为480Mbit/s;再考虑到以太网数据包的封装,实际在FPGA的千兆网通信逻辑设计中,基本的要求是要能达到500Mbit/s以上的通信速度。考虑到逻辑资源的占用量,这里使用了UDP协议结合计算机端数据接收程序的累积确认机制实现。

图5 FPGA逻辑设计框图

2.4 计算机端程序

在计算机端,以C语言调用SOCKET API编写了独立的通信控制及数据存储程序,通过以太网对系统采样模式、参数等进行设置,并接收数字化后的数据。

相比于TCP协议,UDP通信协议有丢数据包的风险,因此在接收数据时,额外加入了累积确认机制[6],即计算机每接收到8个数据包后向FPGA返回一个确认信号,FPGA在接收到确认信号后再继续发送接下来的8个数据包。为尽可能提高数据接收速率,确认信号的发送在另一个线程进行。如此,既避免了丢包,也不影响高速数据传输。经此设计,在迄今为止的实际测试中,包括APV25工作在最高触发率(280kHz)的情况下,均未曾丢包。

接收到的数据经校验无误后,使用高能物理领域广泛应用的ROOT程序进行数据分析。

3 测试结果

APV25及其数字化系统在辐射探测器系统中的作用是对探测器输出的电荷信号进行测量和记录,因此电荷测量的噪声和线性范围是需要测定的基本参数。对于数字化系统,其模/数转换部分的标定是系统测试的基础。下面分别给出这3方面的测量结果。

3.1 数字化系统标定

模/数转换板将APV25输出的模拟电流信号转换为模拟电压信号后,由ADC进行模/数转换,故标定时,我们将不同大小和方向的电流输入该系统,记录并统计ADC输出值。标定结果如图6所示,线性拟合的2=0.999995。可见该系统线性很好,另外,标定中ADC值的方均根值小于0.65ADC单位。

图6 数字化系统标定及拟合结果

3.2 噪声测量

图7所示为无输入信号时该系统各通道的噪声测量结果,经统计其平均值为4.82ADC单位,远大于标定时的0.65ADC单位,故知该系统噪声主要来源于APV25前放电路,后级模/数转换部分的影响可以忽略。另外,由文献[1]可知,APV25输出1mA电流对应的输入电荷为25000e-,结合标定拟合结果知1ADC单位对应148.6 e-,4.82ADC单位噪声对应为716e-,满足一般微结构气体探测器的需求。

图7 无输入信号时APV25各通道噪声测量结果

3.3 APV25线性范围测试

APV25芯片内置有校准用的电荷脉冲产生器,产生的电荷经APV25输入端输入。调节输入的电荷量,APV25成形后的波形变化如图8所示。在无反相器的模式下,统计不同输入电荷量对应的输出波形幅值,得到APV25的电荷响应测量结果(图9)。由图9可知,在75000e-的输入电荷范围内,APV25的线性度都很好,这与APV25的设计者给出的测试结果[7]一致。

图8 不同输入电荷量时APV25的波形采样结果

图9 不同输入电荷量时APV25的输出波形幅值

4 结束语

本文以Spartan-6 FPGA为核心,采用ADS5242进行模/数转换,以千兆以太网传输数据,设计并实现了APV25数字化系统。据测试结果,该系统实现了对APV25输出信号数字化并传输存储的功能,可工作在APV25最大触发率下,累积确认机制的引入避免了UDP传输丢包问题,系统噪声主要由APV25前放产生,在75000e-的输入电荷范围内,系统线性良好。得益于APV25芯片的抗辐射性能,该系统有望用于空间核辐射监测系统或辐射探测实验的多通道探测器的信号读出上。

[1] JONES L L, FRENCH M J, MORRISSEY Q R, et al. The APV25 deep submicron readout chip for CMS detectors[C]//5thConference on Electronics for LHC Experiments. Snowmass, CO, USA, 1999: 162-166

[2] 胡守扬, 蹇司玉, 周静, 等. 基于APV25芯片的GEM探测器读出电子学系统的测试与改进[J]. 原子能科学技术, 2014, 48(6): 1143-1146

HU S Y, JIAN S Y, ZHOU J, et al. Test and improvement of readout system based on APV25 chip for GEM detector[J]. Atomic Energy Science & Technology, 2014, 48(6): 1143-1146

[3] MARTOIU S, MULLER H, TARAZONA A, et al. Development of the scalable readout system for micro-pattern gas detectors and other applications[J]. Journal of Instrumentation, 2013, 8(3): C03015

[4] MUSICO P, BELLINI V, CAPOGNI M, et al. Hybrid silicon μstrip and GEM tracker for JLab hall: a high luminosity experiments[C]//Nuclear Science Symposium and Medical Imaging Conference, IEEE. Valencia, Spain, 2011: 1306-1308

[5] 李诚, 刘树彬, 田静, 等. 基于APV25多通道读出电子学系统设计[J]. 核电子学与探测技术, 2016, 36(1): 5-9

LI C, LIU S B, TIAN J, et al. An APV25 based multi-channel readout electronics system[J]. Nuclear Electronics & Detection Technology, 2016, 36(1): 5-9

[6] CALVET D. A versatile readout system for small to medium scale gaseous and silicon detectors[J]. IEEE Transactions on Nuclear Science, 2014, 61(1): 675-682

[7] RAYMOND M, BAINBRIDGE R, CANDELORI A, et al. APV25 production testing and quality assurance[J]. Testing and Quality Assurance for Component-Based Software, 2003(3): 50

(编辑:闫德葵)

Design of APV25 digitization system for MPGD based on Spartan-6

LI Xinglong1, HU Shouyang1, ZHOU Jing1, ZHI Yu1, CHEN Lei1, LIU Wendi1, ZHAO Mingrui1, LI Peiyu1, LI Xiaomei1,2

(1. Science and Technology on Nuclear Data Laboratory, China Institute of Atomic Energy, Beijing 102413, China; 2. State Key Lab of Particle Detection and Electronics, University of Science and Technology of China, Hefei 230026, China)

To meet the demand of high-speed readout of multi-channel signals from micro pattern gas detectors, a digitization system is designed for the 128-channel preamplifier chip APV25 based on the field programmable gate array (FPGA) Spartan-6. In this system, the serial analog signal output by the APV25 is digitized by the analog-to-digital conversion (ADC) chip ADS5242. After the serial-to-parallel conversion by the Spartan-6, the data are acquired, buffered and packaged to the user datagram, and then sent to the computer via the gigabit ethernet for storage and analysis. In the test, the system reaches a maximum sampling rate of 280kHz for the APV25, and the pedestal noise is as low as 716 electrons. The linearity of the charge response is good when the input amount of charge is less than 75000 electrons. This system is expected to be used in the multi-channel radiation detection system in space thanks to the radiation tolerance of the APV25.

APV25 chip; Spartan-6; digitization system; gigabit ethernet; hardware design

O572.21

B

1673-1379(2018)02-0200-05

10.3969/j.issn.1673-1379.2018.02.017

李兴隆(1990—),男,博士研究生,粒子物理与原子核物理专业。

李笑梅(1973—),女,满族,博士学位,研究员,研究方向为中高能物理研究和先进气体探测器研制;E-mail: xiao_mei_li@foxmail.com。

2017-12-12;

2018-04-01

国家重点研发计划项目(编号:2016YFE0100900,2016YFA0400300);国家自然科学基金项目(编号:11775313);核探测与核电子学国家重点实验室开放课题基金项目