基于FPGA的多串口通讯设计

2016-07-23张春芳江南大学江苏无锡214122安徽工商职业学院安徽合肥231131

张春芳(江南大学,江苏 无锡 214122;安徽工商职业学院,安徽 合肥 231131)

基于FPGA的多串口通讯设计

张春芳

(江南大学,江苏无锡214122;安徽工商职业学院,安徽合肥231131)

摘要:在工程实现中,经常需要一个系统与另一个系统进行多串口通信,为此本文设计了基于FPGA的串行通讯模块,详述了各模块的设计思路和方法.经综合、布局布线后,将程序下载到FPGA芯片中,经测试运行,数据接收正确无误,模块工作稳定、可靠,通过复制基本模块,可满足需要多个串口场合的系统要求.

关键词:FPGA;串口;综合;布局布线

1 前言

通用异步收发器因其简单可靠而被广泛使用,各种微处理器,不论是单片机、DSP、ARM等,UART都是基本外围模块,许多场合如系统监控、数据采集、串口服务器都要用到多个串口通信,此时通常采用专用芯片扩展串口,专用芯片使用简单,然而缺乏灵活性,同时专用芯片集成的串口数量也有限,有时需使用多个芯片才能满足要求,增加了系统的复杂度,降低了可靠性.关于FPGA串口的研究已有文献[1-5],在此基础上本文提出了一种基于FPGA串口设计方案,由于FPGA的可编程性、丰富的资源,可根据系统需要,在不用更改系统硬件的条件下,随时实现多个串口,具有设计灵活、升级方便、集成度高等优点.

在设计一款电磁干扰系统时,系统监控分系统需要通过串口对后级的激励分机进行控制和监视,由于电磁干扰系统需要对多个频段进行全覆盖,如对讲机、WIFI、遥控器、2G移动通信、3G移动通信等各种频段进行干扰,系统需要多个激励分机,这样就要求监控分系统需多个串口和激励分机通信,本系统需要12个串口,同时监控系统还要和上位机通过串口通信,又需要1个串口,市面上无论是8位和32位单片机均没有这么多的串口资源.

为此我们选用由FPGA芯片来实现多串口的设计,作为一种高速、灵活、可靠的可编程逻辑器件,不仅提高了系统的集成度、灵活性、可靠性,而且降低了产品的开发周期和成本.本设计的FPGA芯片选用的是Altera公司的CycloneIIFPGA系列中的产品EP2C35F484I8,这种低成本的FPGA芯片功耗大大低于同等容量的其他FPGA,待机功耗不到200mw,非常适合集成度高和需要低功耗的多种应用.

2 功能模块设计

2.1UART通讯原理

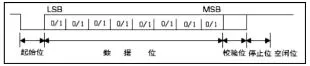

UART即通用异步收发器是一个字符接一个字符传输,一个字符的信息由起始位、数据位、奇偶校验位和停止位组成,如图1所示.字符的前面是一位起始位,用时钟下降沿通知接收方传输开始,紧跟着起始位之后的是数据位,一般由5~8位数据位组成.数据位后面是奇偶校验位,最后是停止位.停止位是高电平标志一个字符的结束,并为下一个字符的开始传送做准备.停止位后面是不定长度的空闲位.停止位和空闲位都规定高电平,这样可以保证起始位开始处有一个下降沿.方案中采用1位起始位,8位数据位,不设奇偶校验位,1位停止位,波特率可调的数据传输方式.

图1 串口帧格式

2.2UART发送模块

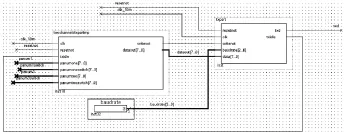

图2右边是发送模块VHDL生成的符号图,其中writenot为上级模块加载并行数据指示信号,txidle为一字节发送完指示信号,通知上一级发送下一字节数据.Writenot、txidle可以说是串口发送模块和上一级模块的握手信号,因为本设计的全局时钟为10MHz,而串口的通信波特率一般为4800bps、9600bps、19200bps等速率,远低于10M时钟速率,故需在发送模块和上一级模块之间建立握手信号. resetnot为全局复位信号,clk_10m为全局时钟,dataout[7..0]为并行数据输入端,txd为串行数据输出端,baudrate[2..0]为发送模块的波特率选择信号.

图2 串口发送模块符号图

发送模块在每个全局时钟上升沿检测是否有加载数据指示信号(writenot),若检测到其上升沿,则将并行8位数据锁存进发送寄存器,接下来在每个发送时钟(即波特率时钟)的触发下,8位移位寄存器就可以将其中的数据逐次移位发出,当一个字节数据发送结束,txidle反馈一个脉冲信号,通知上一级模块(twochanelstxpartmp)可发送下一字节,这样依次串行发送一连串字节数据.波特率的选择计算如下:以9600bps的波特率为例,需对全局时钟进行计数,并对10MHz时钟进行分频,得到9600Hz频率的时钟,10MHz/9.6KHz=1042,即对10MHz时钟进行1042分频.

2.3UART接收模块

图3左边是接收模块VHDL生成的符号图,其中resetnot为全局复位信号,clk_10m为全局时钟,baudrate[2..0]为发送模块的波特率设置,dataout [7..0]为并行数据输出端,rxd为串行数据输入端.

图3 串口接收模块符号图

UART接收模块时时检测线路,当线路产生下降沿时,即认为线路有数据传输,启动接收数据进程进行接收,按从低位到高位接收数据.将接收数据的送入8位移位寄存器中,在8比特数据采样结束后,再间隔16个采样周期采样停止位.如果采样得到的是高电平,则认为该帧数据有效,同时将输出数据标识位(rxidle)置高,将移位寄存器中的数据并行送出到下一级模块(rxpartmp)后,重新等待下一帧的到来.

接收模块设计时,我们用一个有限状态机来进行数据的接收判断,一共有S0、S1、S2、S3、S4、S5、S6、 S7、S8、send等10个状态,系统的初始状态为S0,当接收使能信号rxden为1时,即检测到数据下降沿来临,将次态rxstate1置为s1,在下一个波特率时钟上升沿来到时,将次态rxstate1赋给现态rxstate0,状态转换为s2,依次进行状态转换,当现态rxstate0为send状态时,则模块将接收到的一字节数据并行送出到下一级模块(rxpartmp),从而保证了数据的完整接收.

2.4系统测试结果

将发送模块和接收模块组合起来,如图4上图所示,就能较容易地实现通用异步收发器总模块设计,如图所示,再综合、布局、布线,在PC机上安装一个串口调试工具,通过串口调试工具向FPGA发送一串数据,再在PC机上接受FPGA发送的数据.试验结果显示串口调试工具均能正确收到发送的数据,QuartusⅡ的SignalTap数据采样结果如图4下图所示,数据在输入端和输出端是一致的,表明设计的串口传输可靠、稳定.

图4 接收发送总模块及SignalTap采样数据图

3 小结

本文详细地介绍了FPGA实现串口的整个过程,包括发送模块、接收模块的实现.本设计可作为FPGA开发多串口设备的一个基本模块,通过复制基本模块,可在一片FPGA芯片上扩展出多个串口,而数量仅与FPGA可用资源有关,满足多串口场合的需要,替代采用专用串口芯片的传统设计方案,降低多串口系统的复杂度,提高系统可靠性.

参考文献:

〔1〕沈克宁,林锦泸,等.基于的多串口服务器设计[J].武汉理工大学学报,2011,33(2):204-206.

〔2〕粟慧龙,肖辽亮.基于CPLD/FPGA的多串口设计与实现[J].电子设计工程,2011,19(2):77-79.

〔3〕刘凤新,赵坚固.基于FPGA的多路并行独立串口的实现 [J].仪表技术与传感器,2010,11(6):45-46.

〔4〕陈志逸,赵敏,等.基于并行控制的FPGA多串口拓展实现 [J].机械制造与自动化,2014,43(1):124-127.

〔5〕卢俊文,郑鹭斌.等,基于IP核的多UART扩展及其FPGA实现[J].计算机技术与发展,2010,20 (6):188-191.

中图分类号:TP368.1

文献标识码:A

文章编号:1673-260X(2016)06-0027-02

收稿日期:2016-03-11

基金项目:2015年安徽省高等学校自然科学研究重点项目 (KJ2015A450);2016年安徽省高等学校自然科学研究重点项目(KJ2016A081);2016年安徽省高等学校自然科学研究一般项目(KJ2016B001)