表面栅静电感应晶体管沟道势垒形成机理研究

2015-01-2993856部队王富强马行空瞿宜斌

93856部队 王富强 马行空 瞿宜斌

表面栅静电感应晶体管沟道势垒形成机理研究

93856部队 王富强 马行空 瞿宜斌

为了研究静电感应晶体管(SIT)势垒形成机理,本文利用Silvaco Tcad软件模拟,仿真分析了沟道势垒对栅、漏极电压的依赖关系。通过改变反偏栅压和漏偏压,得出了器件沟道在完全夹断状态下,沟道势垒成马鞍型分布。反偏栅压影响着器件导通和关断状态,漏偏压影响着势垒的高低,且二者相互依赖,共同影响着沟道势垒的形成。

静电感应晶体管;沟道势垒;鞍电势

引言

作为具有类三极管特性的静电感应晶体管[1]因其具有的高频特性、功率放大性能、高耐压、线性度好、电流容量大、阻断增益高等一系列优异性能,而被广泛应用。但是静电感应晶体管的理论研究具有唯象性[2],利用CAD软件的研究还不多见,且理论研究迟滞于实践过程。本文利用Silvaco Tcad软件的器件仿真模块Atlas[3],通过结构设计和参数设置,仿真和分析了静电感应晶体管沟道势垒形成机理。

1 器件结构设计

因表面栅结构可以制作出功率小、电流容量大和频率较高(音频范围)的静电感应晶体管,且容易在实验中制作得到,同时通过软件容易实现结构和工艺仿真,所以,本文在研究静电感应晶体管沟道势垒形成机理时选用表面栅结构。其仿真研究采用的元胞结构中,器件深度为200μm,器件宽度为15μm,栅极区和源极区离子注入窗口宽度均为1μm,栅极区扩散结深和表面掺杂浓度分别为7μm和1×1019cm-3,源极区扩散结深和表面浓度分别为1μm和5×1018cm-3,漏极区淀积深度和表面浓度分别为45μm和1×1019cm-3。

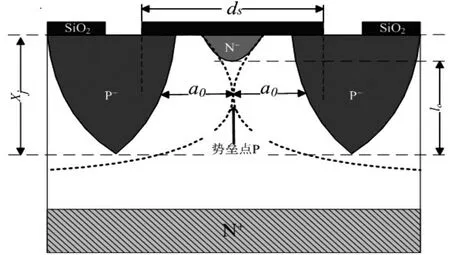

器件结构如图1所示。结构从上往下,从左往右,源极区为重掺杂的n+区,栅极区为重掺杂p+区,中间沟道区以及往下区域均为漂移区,为轻掺杂的n-区,漏极区为重掺杂的n+区。

2 势垒高度对栅极电压的依赖关系

为了更加清楚地了解栅极电压和漏极电压对沟道势垒高度的影响,如何控制和影响器件电流-电压的特性,先对沟道势垒高度进行简单的分析。对于本文研究的常开型静电感应晶体管,当反偏栅压VGS大于某一值时,耗尽区从栅极区向源极区扩展,最终汇合在沟道中心。这使得沟道状态从打开到预夹断,再到完全夹断耗尽,同时也阻断漏极区越过漂移区向沟道区漂移和扩散的电子,从而阻断电流。当漏电压一定且为一个较小数值时,纵方向沟道内耗尽区对电流产生势垒。图2仿真了静电感应晶体管势垒高度的三维分布图。

图1 器件内部相关参量示意图

图2 基于硅衬底SIT在类三极管特性下的鞍电势图

从图2中可以看出,静电感应晶体管在类三极管模式下的电势三维图的形状是马鞍型,这是因为鞍电势形成源于栅偏压VGS和漏偏压VDS两个方向,沟道内每个点的电势都是这两个垂直方向电压的矢量和。该鞍电势位于沟道的几何中心,即在沟道横向Wch和沟道纵向Lch中心线的交点处。这个势垒位置被称为“鞍点”[4-6],其峰值大小常被称为“鞍电势”,也就是常说的势垒电压[7-8],它阻止了漏极区电子向源极区的流动。

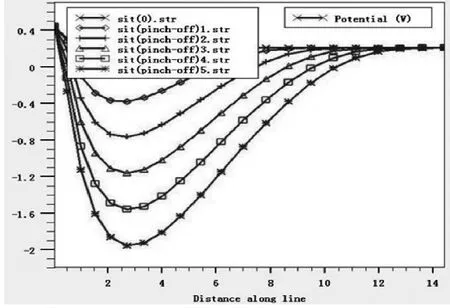

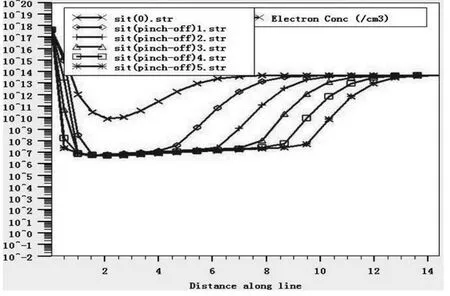

图3(a)仿真了静电感应晶体管沟道电势沿着沟道中心的分布情况(VDS=0V)。从图中可以看出,随着反偏栅压的增大,沟道电势也相应增大,曲线展宽表明沟道耗尽层长度变长;图3(b)模拟了平行于器件表面方向沟道势垒分布情况(VDS=0V),从图中可以看出,沟道势垒位于沟道中心,随着反偏栅压的依次增大,鞍型曲线更加明显。同时,图3(b)中曲线分布均匀,鞍电势的变化与反偏栅压几乎一致,所以可以肯定鞍电势和反偏栅压之间保持着线性关系。

(a)沟道电势沿沟道中心方向分布

图3 不同栅压下,沟道势垒随漏偏压变化

图4仿真了不同栅压下沟道内电子浓度的变化情况。从图中可以看出,当反偏栅压为零时,沟道电子浓度曲线最为平缓,此时沟道处于预夹断状态,较小的漏电压下,势垒高低迅速降低,漏电流达到较大值;当反偏栅压继续增大(VGS<-0.5V),电子浓度曲线在最低点重合,这表明沟道已完全夹断。横向方向上,电子浓度曲线随着反偏栅压的增大而左移,且其幅度反而变小。这表明沟道势垒屏蔽层随着栅偏压的增大而展宽,

但其展宽幅度越来越小,换句话说,耗尽层变厚,鞍电势位置点向漏极区靠近。

图4 不同栅压下,沿沟道中心电子浓度变分布

3 势垒高度对漏极电压的依赖关系

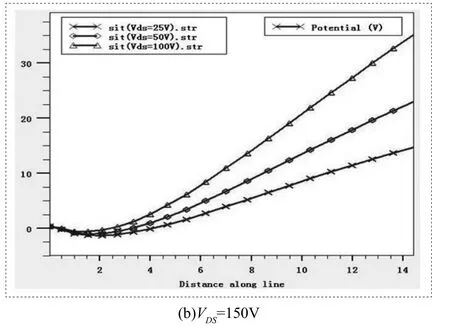

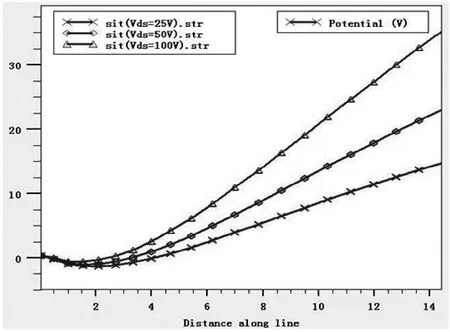

在分析了势垒对栅偏压的依赖关系时,其实已经进行了漏偏压的大小对鞍电势的影响的理论分析。图5仿真得出同一栅压和不同栅压下沟道电势随漏偏压变化图。从图5(a)可以看出,当VG=-2.5V,VDS较低时(VDS<100V),随着漏偏压VDS增加,沟道电势先减小后增大,其转折点就是鞍电势位置点。随着漏偏压VDS增大,鞍电势反而减小,同时鞍电势位置点移向源极区。另外,沟道电势的降低以源极为不变值,其他的点随漏偏压的变化符合鞍型趋势。从图5(b)给出的沟道势垒的变化曲线可以看出,当漏偏压VDS较大时(VDS>100V),沟道电势曲线图和漏偏压较低时(VDS<100V)基本一致,但不同于前者的是当鞍点靠近到源极区时,鞍电势位置点随VDS的变化趋势会很小,同时当VDS=125V、VDS=150V、VDS=175V时对应的三条曲线纵方向沟道电势变化也很小,说明此时反偏栅电压对沟道势垒的影响已经微乎其微。

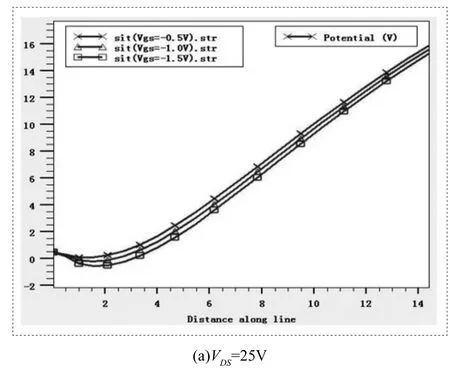

总之,漏偏压大小影响着鞍电势位置点在沟道中的高低,而栅偏压直接影响着栅耗尽层是否扩展至沟道中心,甚至相交,也就是沟道是否关闭。从图6(a)可以看出,当漏偏压VDS=25V时,反偏栅压越大,沟道势垒位置点越靠近源极区,这表明在漏偏压较小的情况下,反偏栅压对沟道状态有很好的调制作用;从图6(b)可以看出,当漏偏压VDS=150V时,不同栅压下的几条鞍电势曲线图几乎重合,这就充分说明在漏偏电压较大的情况下,鞍电势位置点已经紧靠源极区,此时栅偏压的大小与沟道鞍电势位置点的高度无关,反偏栅压对沟道状态失去了调制控制作用,可以忽略不计。另外,当沟道电势小于鞍电势值时,器件因高低结整流而导致栅偏压对鞍电势影响很小;相反,当沟道电势大于鞍电势值时,栅极反偏电压对器件的工作状态有很大的影响,从而控制和调节器件电流的大小。所以,沟道鞍电势由漏偏压VDS和栅偏压VGS通过这种类似于静电感应式的诱导控制着沟道势垒高低,二者相互制约,共同影响着静电感应晶体管的电流-电压特性。

图6 漏偏压一定,不同栅偏压下沟道势垒分布图

4 结论

(a)沿沟道中心较小漏偏压下沟道电势变化

图5 栅偏压一定,不同漏偏压下沟道势垒分布图

本文通过软件Silvaco Tcad模拟仿真,得出了静电感应晶体管沟道鞍电势的存在是在沟道完全夹断条件下,且反偏栅压影响着沟道导通状态,并与鞍电势保持线性关系,而漏偏压影响着沟道势垒的高低。另外当反偏栅压为-2.5V时,漏偏压在100V范围内对沟道电势影响较大,而大于100V后漏偏压对沟道电势影响微乎其微。当漏偏压较小时,栅偏压对沟道电势影响较大,当漏偏压较大时,栅偏压对沟道电势几乎没有影响。本文的研究对静电感应晶体管对工艺实践起到理论指导作用。

[1]李思渊.静电感应器件作用原理[M].兰州:兰州大学出版社,2002.

[2]李思渊.静电感应器件—物理、工艺与实践[M].兰州:兰州大学出版社,2001.

[3]朱筠.利用SILVACO TCAD软件改进集成电路实践教学的研究[J].数字技术与应用,2012,14(7):113-118.

[4]J.Nishizawa,T.Terasaki,and J.Shibata.Field-effect transistor versus analog transistor(static induction transistor).Electron Devices,IEEE Transactions on,1975,22(4):185-197.

[5]张琳娇.小功率射频静电感应晶体管的设计[D].兰州大学硕士学位论文,2014.

[6]刘亚虎.音频小功率静电感应晶体管的制作工艺[D].兰州大学硕士学位论文,2014.

[7]Wang Y S,Liu S,Li S Y et al.Electrical Performance of Static Induction Transistor with Mixed I-V Characteristics.Chinese Journal of Semiconductors,2004,25(3):266-271.

[8]Hu D Q,Li S Y,and Wang Y S.Analysis on Characteristic of Static Induction Transistor Using Mirror Method,Chinese Journal of Semiconductors,2005,26(2):258-264.

王富强(1988—),男,硕士,助理工程师,主要研究方向为静电感应器件器件和集成电路的设计与研究。