基于FPGA的8位CPU设计

2014-04-01,

,

(安阳师范学院,河南 安阳 455000)

CPU作为计算机系统的核心,其功能与结构设计一直是国内外研究的热点。近年来随着计算机和微电子技术的发展,采用EDA技术,基于FPGA器件的CPU设计成为计算机组成原理和计算机系统结构实验中的重要内容[1]。如何使CPU更有效率地工作,使其内部结构更精简,一直是研究的方向。本文研究了CPU的功能和结构特点,完成了一个8位CPU的设计,并给出综合仿真结果。

1 CPU功能简介、模块组成和指令集

本文设计的CPU是基于FPGA器件的具有完整的取指、译码、执行功能的8位CPU。在此设计中,指令系统采用单字长结构,指令地址码部分采用直接寻址方式,指令所能访问的数据存储器的地址空间为32字节。为简化处理,所设计的指令存储器的地址空间也为32字节,用5位指令地址进行访问取指。

1.1 CPU功能简介

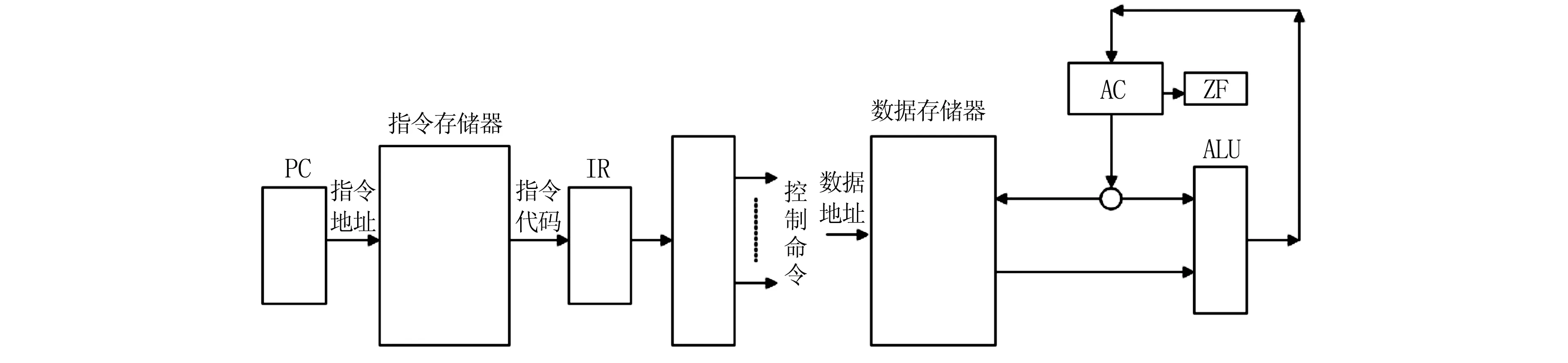

CPU的功能主要是取指令、分析指令、执行指令。其工作过程是对所存储的程序指令进行读取,并进行指令译码,从而按照指令所代表的含义执行相应操作。基于此设计的CPU及存储器的大致结构如图1所示。在图中可以清晰地看到整个CPU的运作过程。首先从寄存器PC中取出指令地址,根据指令地址从指令存储器中取出指令,将指令放入寄存器IR中,再根据寄存器IR中的指令进行指令分析;其次从数据存储器中进行数据存取,通过ALU运算器,最终按照指令要求进行数据加工操作;最后根据AC结果值,对标志位ZF进行赋值。根据整个CPU的运作过程,把CPU的功能模块设计成取指部件、译码部件、执行部件三大功能部件,然后设计一个时序信号处理部件来控制这三个部件的执行[2]。

图1 CPU结构图

1.2 CPU的模块组成

基于FPGA的8位CPU的设计主要包括三大功能部件:取指部件、译码部件、执行部件。这三大功能部件的执行通过时序信号处理部件timer来控制,从而模拟CPU的功能。其中,取指部件的主要功能是根据指令地址从指令存储器中取出指令,然后把取出的指令送给译码部件;译码部件进行指令功能解析,取出需要操作执行的数据;执行部件根据译码部件提供的译码命令和数据,进行最终的操作执行[3]。

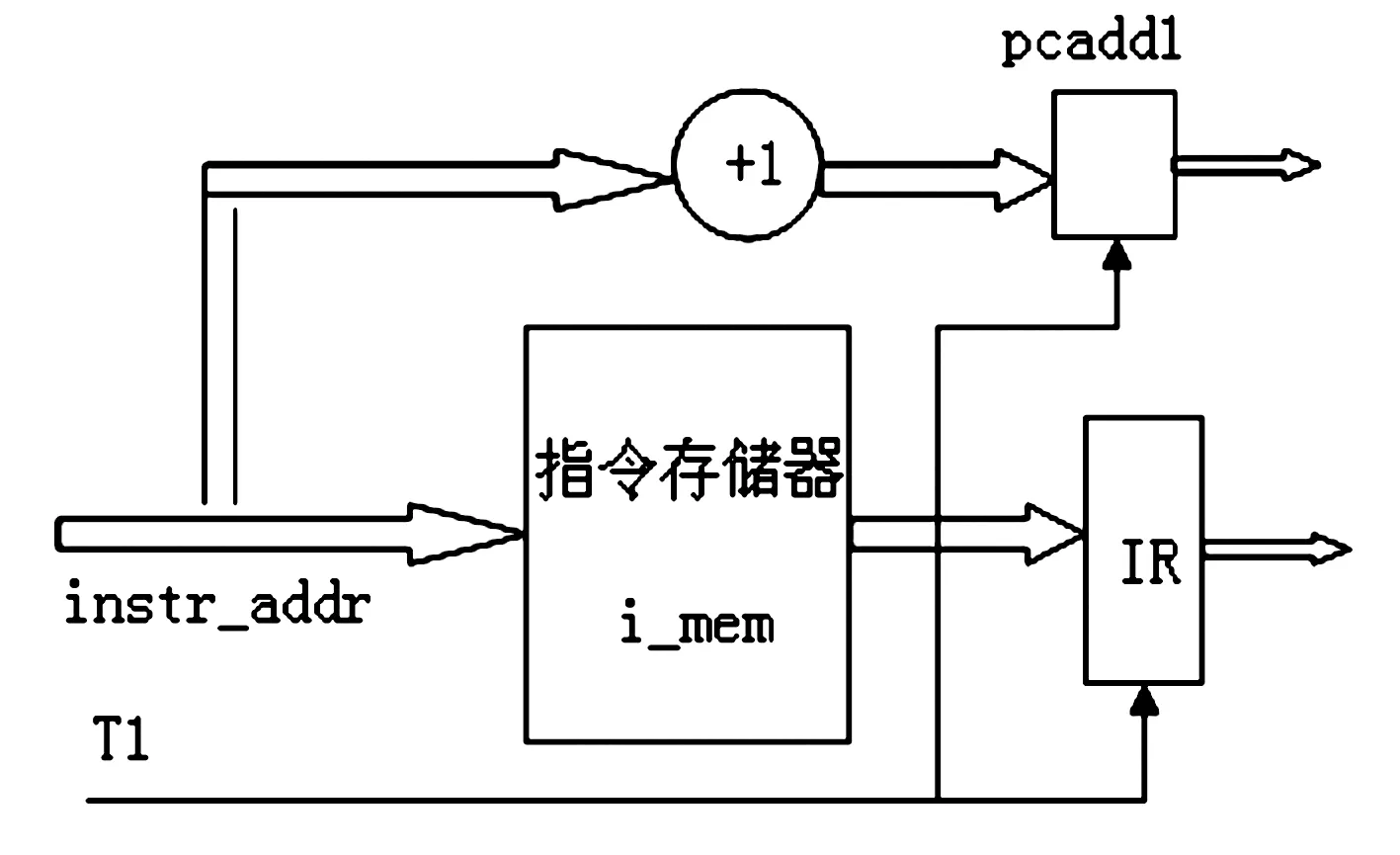

(1)取指部件:i_fetch,如图2所示。该部件以PC中的指令地址instr_addr为输入,在指令存储器中读取指令,在时钟信号的边沿将指令存入指令寄存器IR中,并将取指令地址+1送入pcaddl。该部分的核心为指令存储器。

图2 取指部件:i_fetch

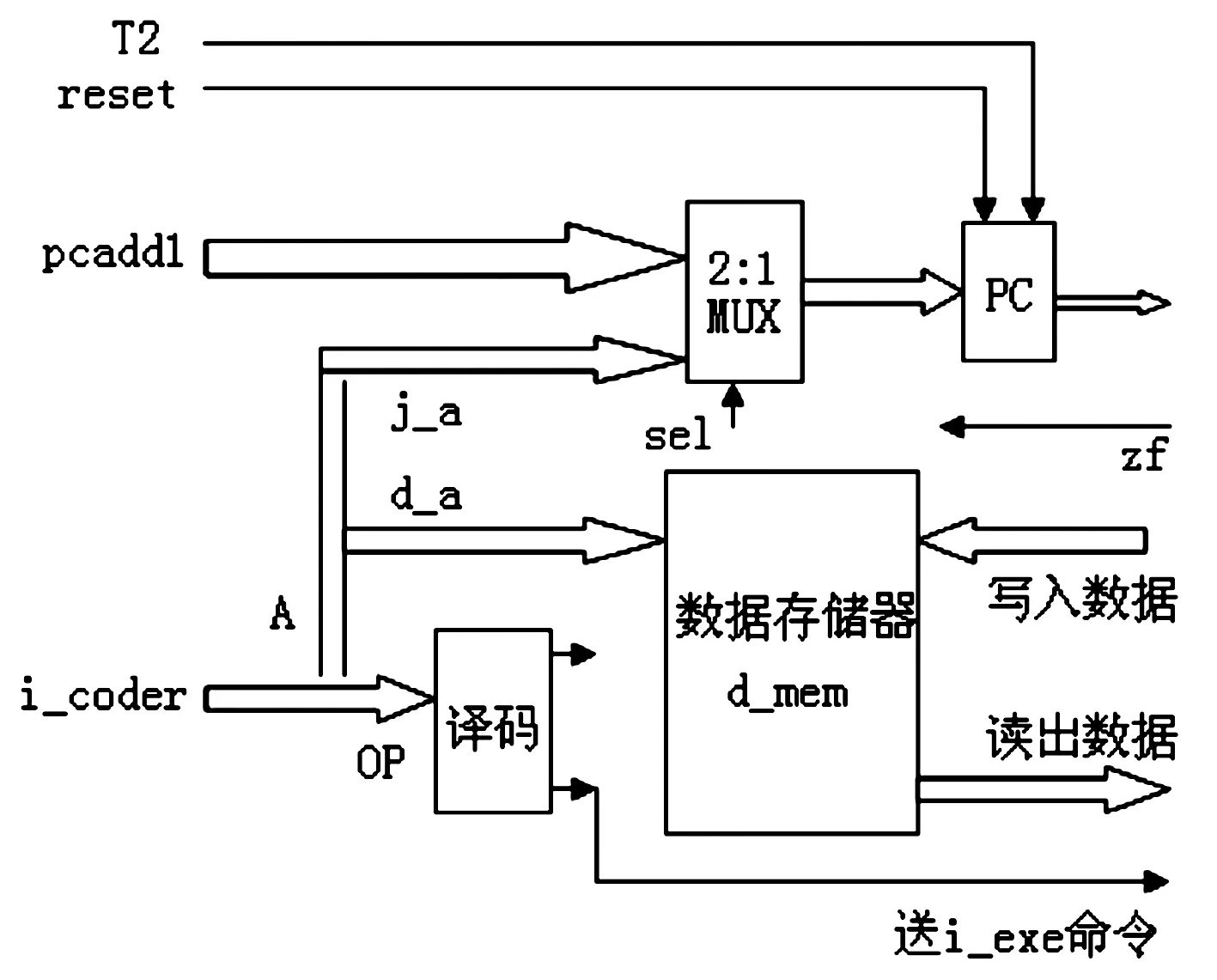

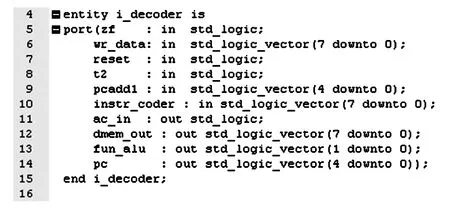

(2)指令译码部件:i_decoder,如图3所示。该部件以IR中的指令代码为输入,完成指令译码分析,产生各种控制命令。因为指令系统中的各指令地址都采用直接寻址,所以译码阶段可直接使用该地址处理,以完成数据在数据存储器上的存取操作。在执行指令译码部件功能时,需要考虑PC值的变化情况。在指令地址没有发生跳转时,需对PC置入取指部件送来的指令地址pcaddl,产生后继指令地址;在转移执行时,需对PC置入转移地址,同时在系统执行指令时,无论指令地址是否发生跳转,如果系统的复位信号RESET产生复位,都需要对PC清0;在执行动态停机指令halt时,可使PC值保持不变。

图3 指令译码部件:i_decoder

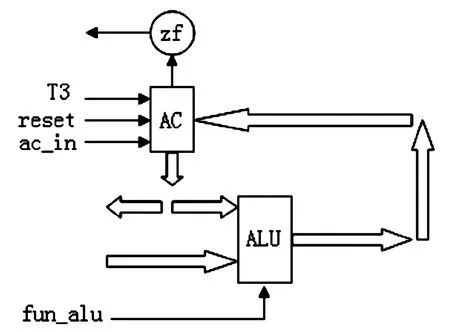

(3)指令执行部件:i_exe,如图4所示。该部件包括ALU与累加器AC,ALU为核心部件。对AC值的打入使用时序信号控制,同时执行部件会根据AC结果值,对标志位ZF进行赋值,该标志会被送回指令译码部件,当执行jz指令时,决定是否转移。

图4 指令执行部件:i_exe

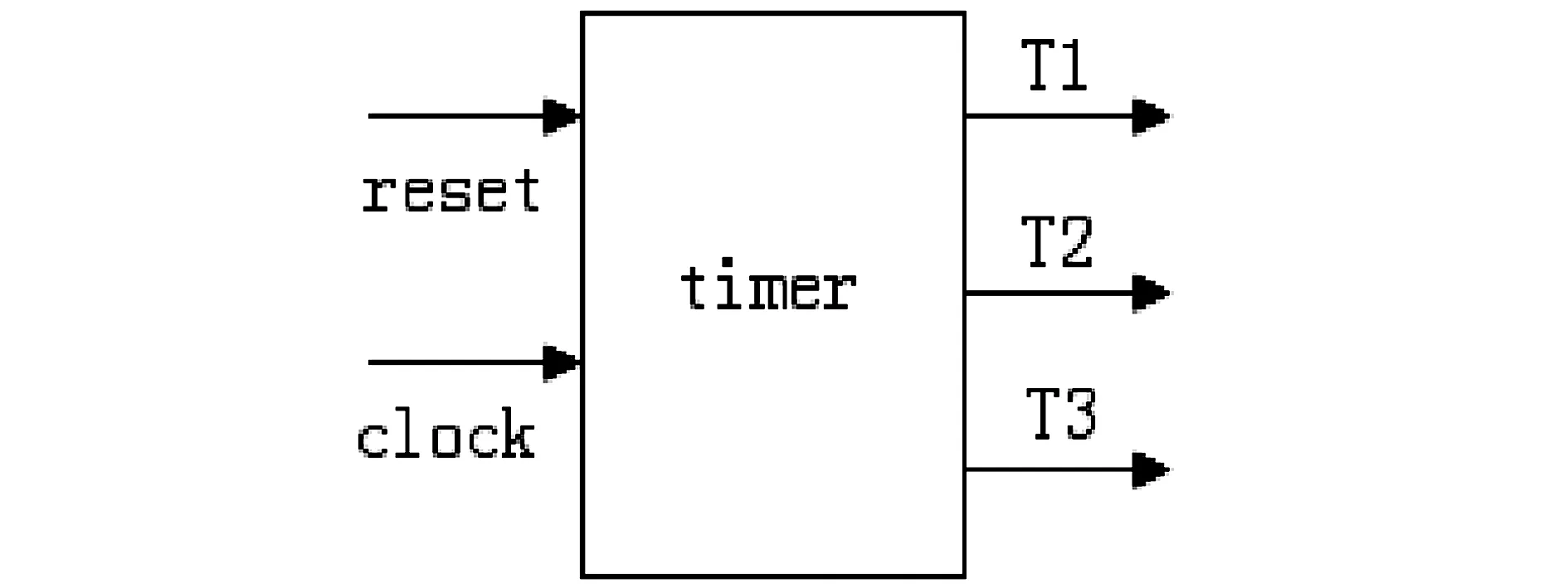

(4)时钟信号处理部件:timer,如图5所示。该部件本来是控制器的一个组成部分,现在单独作为一个模块来设计。考虑到前面的3个模块的划分,每个部件都需要一个时钟信号来控制其中寄存器、存储器部分数据的写入和读出。每个部件所需要的时钟信号分别称为T1、T2、T3,它们是由时钟信号处理部件timer根据时钟信号clock周期性地依次产生的,但在系统复位时不产生时钟信号。

图5 时钟信号处理部件:timer

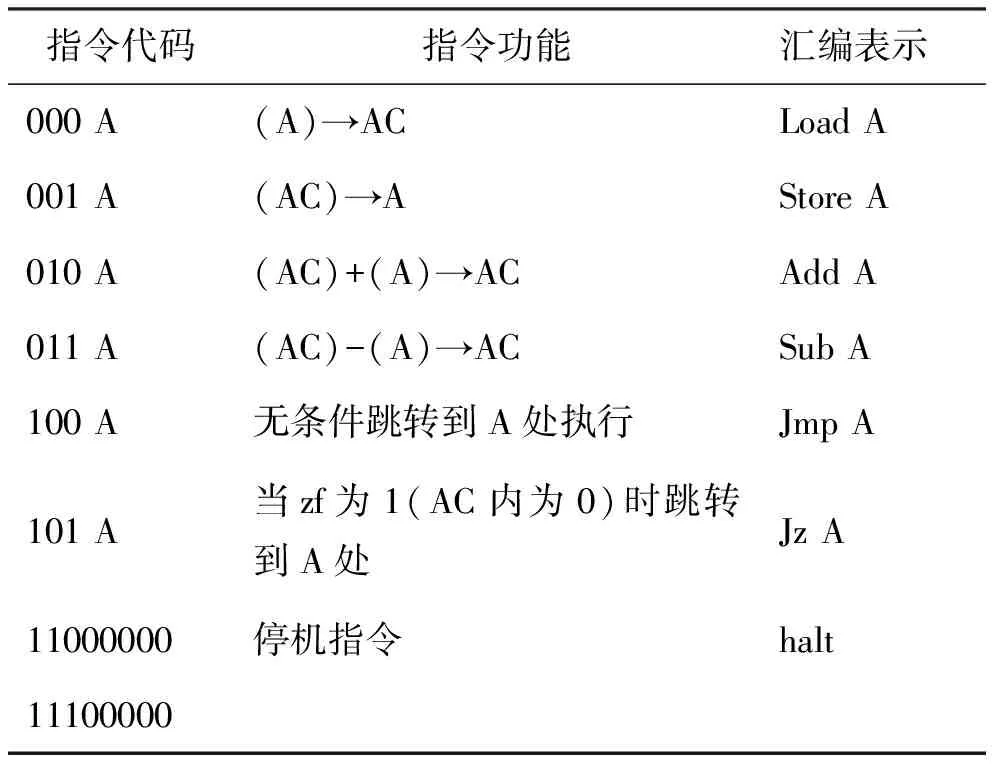

1.3 指令集

设指令字长为8位,每字节存放一条完整的指令,指令操作码为高3位,地址码为低5位,CPU的寻址方式为直接寻址,CPU设计中的机器指令主要支持如下指令,如表1所示。

2 关键模块的设计

2.1 指令译码部件的设计

在该CPU设计中,指令译码部件通过取指部件取得指令,根据指令集将指令进行译码,产生控制指令执行的一系列命令,同时完成存取数据的处理。其VHDL程序实体部分定义如图6所示。

表1 指令系统表

图6 指令译码部件VHDL程序实体部分定义截图

在指令译码部件程序截图中,zf为0标志位,reset为复位信号,wr_data为要写入数据存储器中的数据,t2为时钟,pcadd1为加1后的指令地址,instr_coder为IR中存储的指令代码,pc为输出的指令地址,dmem_out为输出的数据,fun_alu为控制执行部件的操作命令,ac_in用来控制执行部件是否打入AC值。

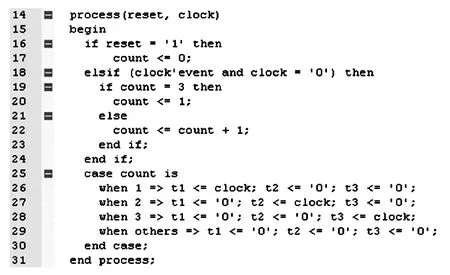

2.2 时序控制部件的设计

时序控制部件应依次产生控制各功能部件操作的时序信号。应用VHDL语言完成其设计后,其VHDL程序结构体部分定义如图7所示。

图7 时序信号处理部件timer的VHDL程序结构体部分定义截图

在时序控制部件程序截图中,t1、t2、t3通过信号count来依次获取时钟,获取时钟后,t1用来控制取指部件,t2用来控制指令译码部件,t3用来控制执行部件。在代码中,获取时钟的顺序为t1、t2、t3,所以在CPU执行中,先执行取指部件,再执行译码部件,最后执行执行部件。

3 软件仿真综合与硬件实现

3.1 软件综合与仿真

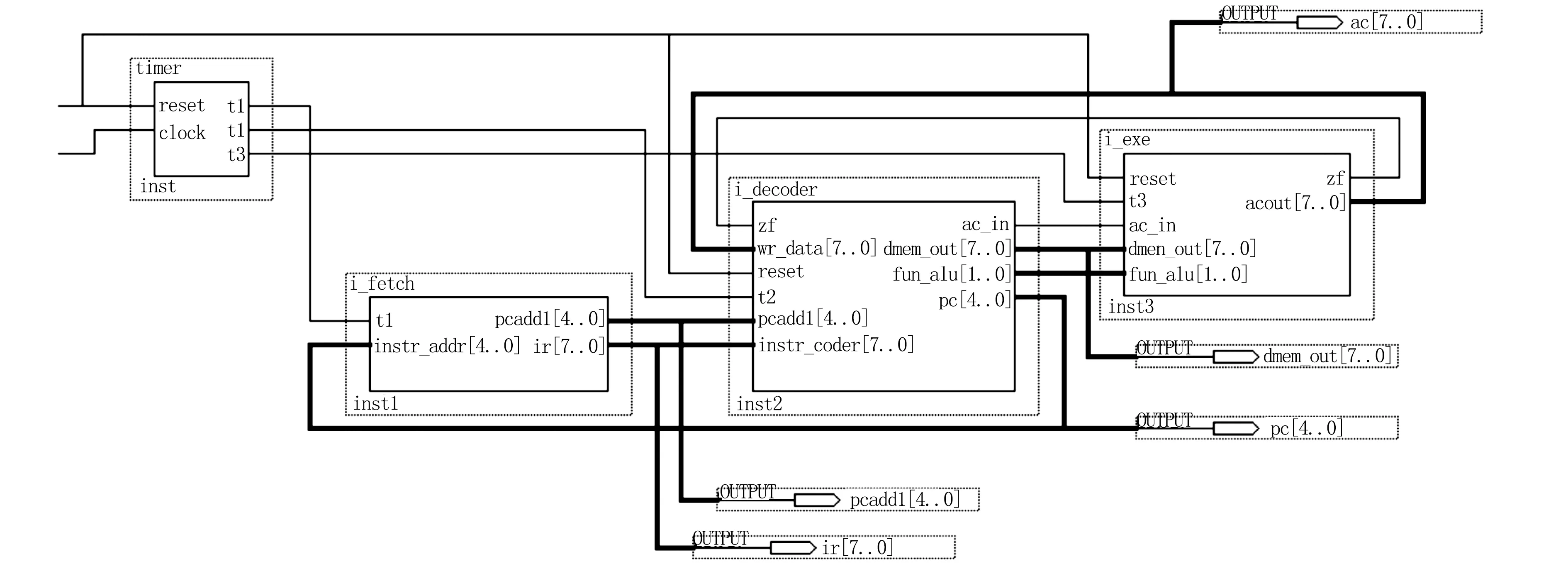

此次设计的CPU总共有四大模块,首先对每个模块进行单独的设计和仿真,实现其功能,然后将各个模块进行连接,创建顶层的设计文件simcom.bdf。顶层模块连接图如图8所示。

图8 顶层模块连接图

在完成总体设计的情况下,用 QuartusII9.0对其进行综合和仿真,根据之前对存储器中指令和数据的设置,得到仿真结果,如图9所示。

图9 仿真结果图

其仿真所用程序指令可理解如下:

pc 指令 指令含义 数据地址 数据

0 00000100 load 4 00000100 00000111

1 01000100 add4

2 00100100 store 4

3 11000000 halt 4

3.2 CPU设计的硬件实现

基于FPGA的8位CPU设计,其硬件最终实现是在Altera公司的Cyclone系列FPGA芯片EP1C3T100A8上完成的,而最后的硬件仿真结果,也如预期的那样,得到了实现和验证。

4 结 语

基于FPGA的8位CPU设计,完成了对CPU功能模块的设计和仿真,充分展示了使用FPGA和VHDL进行EDA数字系统设计的优越性。该设计中使用独立的指令存储器和数据存储器,这相当于在CPU内使用独立的指令CACHE和数据CACHE,为后继进行基于哈佛结构的复杂CPU设计或带CACHE结构的CPU设计打下了基础。

参考文献:

[1] 汤志忠,杨春武.开放式实验CPU设计[M].北京:清华大学出版社,2007.

[2] 李强,潘明,许勇.基于FPGA的RISC微处理器的设计和实现[J].广西科学院学报, 2005(11): 294-297 .

[3] 马辉,王丁磊.计算机组成原理[M].北京:中国水利水电出版社,2010.