厚多晶硅膜饱和掺杂工艺研究

2012-09-05聂圆燕吴晓鸫

林 丽,聂圆燕,吴晓鸫

(无锡中微晶园电子有限公司,江苏 无锡 214035)

1 引言

在微电子领域中,多晶硅的应用十分广泛。其中,最多的是用作栅电极,而使用多晶硅来制作电阻也非常常见。一般来说,多晶电阻的方块电阻值,都在几十Ω.□-1以上。高值电阻应用非常广泛,制作工艺也很成熟。但是部分特殊电路,会要求将多晶电阻率做到非常低。以下讨论的即为低阻的多晶电阻制作。

根据电路功能的特殊需求,需要制作方块电阻低至2Ω.□-1~4Ω.□-1的多晶硅薄膜。由于多晶阻值很低,因此采用淀积多晶硅膜、再进行炉管饱和掺杂的方法来完成。

2 多晶硅薄膜淀积

2.1 SiO2衬底

由于低阻多晶电阻需要进行饱和掺杂来完成,多晶硅中的杂质浓度非常高。为了防止在饱和掺杂和后续退火过程中,掺杂杂质扩散进入衬底中,在多晶硅和衬底之间,需要有一层较厚的SiO2作为阻挡层。

2.2 LPCVD多晶薄膜淀积

多晶硅通常在580℃~650℃下由硅烷分解淀积。用于淀积多晶硅的主流技术是LPCVD,因为它的均一性,纯度和经济性较好,反应副产物少,洁净度高。多晶硅淀积化学式如下:

基于多晶硅方块电阻值要求,集成电路中常用的几百纳米厚度的多晶硅是无法达到的,需要生长厚多晶硅膜。根据350nm以及1 000nm多晶硅进行饱和掺杂的实验结果,预估要达到2Ω·□-1~4Ω·□-1,需要淀积2 000nm厚的多晶硅薄膜进行饱和掺杂。

3 多晶硅饱和掺杂

3.1 扩散模式

杂质在多晶硅膜中,由于晶粒间界的存在,扩散方式比较复杂。杂质在晶粒间界的扩散比晶粒内点阵间的扩散快很多。根据晶粒间界增强扩散和晶粒内扩散的相对比较,杂质在多晶硅膜中的扩散模式可以分为三类。

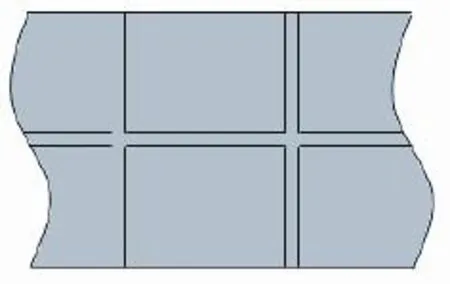

A类:晶粒L较小或晶粒内的扩散较快,以至从两边晶粒间界向晶粒内的扩散相互重叠。简化示意图见图1。

图1 A类扩散模式(阴影区为掺入杂质的区域)

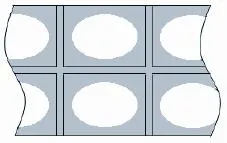

B类:晶粒较大,或晶粒内的扩散较慢,所以在离晶粒间界较远处趋于零。简化示意图见图2。

图2 B类扩散模式(阴影区为掺入杂质的区域,空白区为未掺入杂质区域)

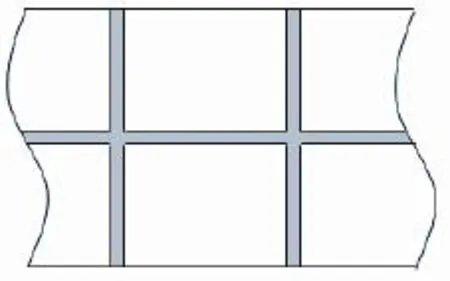

C类:与晶粒间界扩散相比,晶粒的点阵扩散可以忽略不计,因此,有意义的原子输运过程只发生在晶粒间界内。简化示意图见图3。

图3 C类扩散模式(阴影区为掺入杂质的区域,空白区为未掺入杂质区域)

为了达到深饱和掺杂,要使多晶掺杂工作在A类方式,即杂质在晶粒内和晶粒间界同时扩散,并且分布均匀。当多晶厚度有限且扩散时间比较长时,扩散模式往往发展为A类。对于厚多晶硅膜,由于厚度较厚,A类方式就要求很长的掺杂和退火时间。

3.2 扩散方式

多晶硅可以通过扩散、注入或是在淀积时加入掺杂气体进行掺杂。比较这三种掺杂工艺,主要的不同是扩散的电阻率较低,离子注入的掺杂浓度较低,淀积时加入掺杂气体的迁移率较低[2]。炉管扩散掺杂是一种高温过程,掺杂浓度经常超过固溶度极限,过剩的掺杂元素分凝在晶粒间界[3],它使多晶硅的电阻率降得很低。因此,在制作低阻多晶电阻时,采用炉管扩散掺杂方式对多晶硅进行深饱和掺杂。

3.3 炉管掺杂工艺

炉管扩散掺杂多数采用液态源。液态源能提供较好的一致性和纯度。多数液态源是卤族化合物,还能起辅助作用:吸收反应物,排除重金属杂质。液态源的工作方式为:在一定温度下,携带气体通过液态杂质源,带着源的蒸气进入扩散炉,即将液态源转化为气态。这种工艺很容易控制气体流过起泡器的开始或结束时间,便于工艺控制。

目前,炉管掺杂普遍使用液态POCl3源,通入N2作为携带气体,进入炉管后与一起通入的O2反应,在硅片表面的多晶硅薄膜上生成掺杂杂质的氧化物P2O5进行掺杂预淀积。化学反应式为:

反应生成的Cl2被带走,而P2O5与多晶硅反应,P原子被还原出来,通过扩散进入多晶硅薄膜中,并在多晶硅表面生成SiO2。

通入POCl3的预淀积步骤结束后,在N2氛围中进行再扩散,激活杂质,并使得杂质进行再分布,使杂质原子达到稳定状态,并达到预期的方块电阻值。

4 实验

实验步骤如图4。

图4 实验步骤

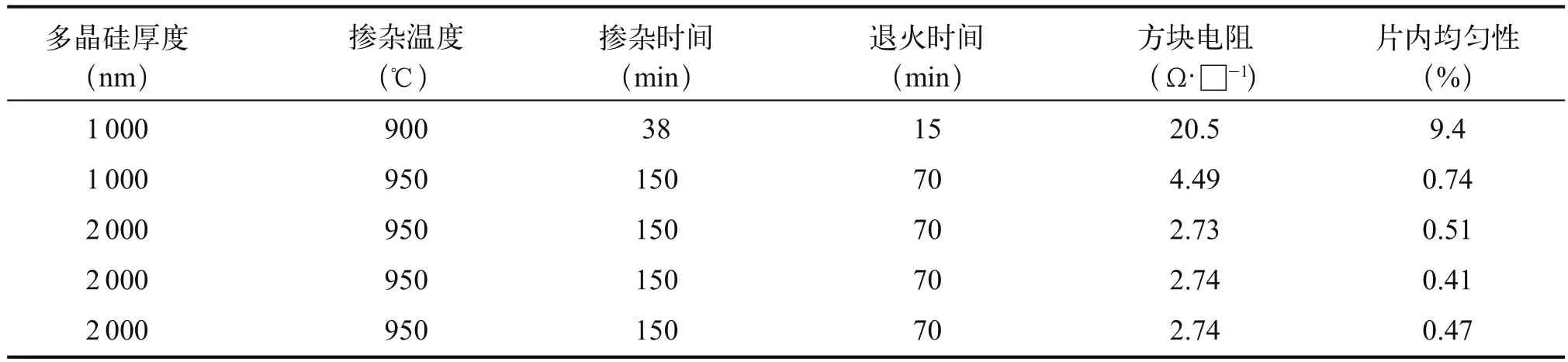

热氧化生长650nm SiO2作为多晶硅与衬底的阻挡层。本实验是在单晶硅圆片上直接制作低阻多晶硅膜,因此可以采用热氧生长SiO2。若在其他衬底上制作,无法采用热氧化的方式,也可以采用CVD淀积阻挡层的方法。LPCVD分别淀积1 000nm及2 000nm厚度多晶硅薄膜,进行掺杂实验。影响炉管掺杂电阻值的因素很多,如扩散温度、气氛、扩散时间、杂质种类、排风等。其中扩散温度、时间比较容易控制和调节,实验时通过对以上因素进行优化,在保证达到饱和掺杂的前提下,取最佳条件进行掺杂,并进行重复性验证。掺杂结束出炉后,使用稀HF酸漂掉多晶硅表面的SiO2后,使用四探针仪测试方块电阻。实验结果如表1。

表1 实验结果

四探针测试MAP图如图5。

图5 四探针测试MAP图

5 结论

从实验结果来看,炉管非饱和掺杂的电阻片内均匀性较差,且若采用非饱和掺杂方式,势必要增加多晶厚度。因此,多晶硅的掺杂虽可采用多种方式,对于低阻的多晶硅掺杂,考虑经济性、大生产以及工艺质量等方面的因素,应选择采用LPCVD淀积多晶薄膜后使用炉管饱和掺杂的方式。采用该方法能够较方便地得到稳定、均匀的方块电阻。

[1]Stanley Wolf, Richard N. Tauber. Silicon Processing for the VLSI Era I [M].Lattice Press, 1986.

[2]王阳元.多晶硅薄膜及其在集成电路中的应用[M]. 北京:科学出版社,2001.

[3]李兴.超大规模集成电路技术基础[M].北京:电子工业出版社,1999.

[4]M M Mandurah, K C Saraswat, C R Helms, et al. Dopant Segregation in Polycrystalline Silicon [J]. Appl.Phys.,1980,51:5 755.