利用FPGA实现三相正弦直接数字频率合成器

2011-03-08吴进

吴 进

(西安邮电学院电子工程学院,西安 710121)

1 引 言

直接数字频率合成器(Direct Digital Synthesizer,DDS)与数字信号处理器(DSP)一样,是一项关键的数字化技术。与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛应用在电信与电子仪器领域,是实现设备数字化的一个关键技术。目前,各大芯片厂商都相继推出了高性能和多功能的DDS芯片,内部数字信号抖动很小,输出信号的质量较高。但是在某些场合,由于专用的DDS芯片的控制方式是固定的,故在工作方式、频率控制等方面与系统的要求差距很大,数字控制器接口不便,难以满足复杂要求,对处理速度要求较高,从而也限制了频率进一步的提高,同时微处理器的处理任务也更加繁重[1,2]。FPGA以其可靠性高、功耗低、保密性强等特点,在电子产品设计中得到了广泛的应用[3]。

本文根据实际需要,设计出符合特定需要的三相正弦DDS电路,通过实验证明,利用FPGA合成DDS是一个较好的解决方法,具有良好的实用性和灵活性。

2 正弦直接数字频率合成器设计原理

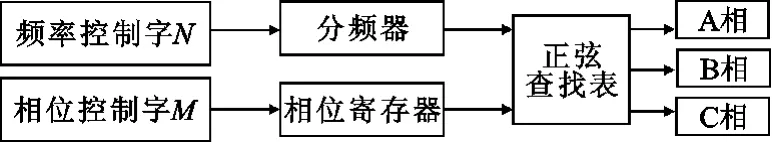

合成器由频率控制字N、相位控制字M分别控制输出正弦波的频率与相位,其中相位累加器为合成器的关键控制部分,通过控制改变频率控制字N与相位控制字M的快慢,从而得到相应频率和任意超前与滞后的相位的正弦波形,甚至是余弦波形。实际这种改变相位控制字M与频率控制字N的配合,通过查找正弦表地址来得到,实际将每个地址对应正弦表中的0~360范围内的每一个相位点。查表将输入的地址信息映射成相应的幅值,从而得到完整的正弦信号,同时通过数模转换器DAC,经过低通滤波器(LPF),就可以得到一个频谱纯净的正弦波。其原理图如图1所示。

图1 三相数字频率合成器结构Fig.1 Three-phase DDS structure

3 正弦波发生原理及逻辑设计

3.1 正弦函数表的设计

在传统正弦函数ROM表的设计中,通常将0~2π整个周期所有的离散信号全部存入芯片中[5]。这种方法虽然实现比较简单,但同时会浪费芯片的大量资源。

考虑到正弦波信号在0~π与π~2π关于直线X=π成偶对称,故可以将ROM表中的数据减少为原来的一半。再利用左半周期内,波形关于直线X=π/2成奇对称,进一步可将正弦函数ROM表减少一半。这样,就可以将ROM表的数据减少为原来的1/4,可极大减少正弦函数ROM表在芯片内部占用的逻辑资源。即通过一个正弦波形表的前1/4周期,就可以变换得到正弦的整个周期波形,同时减少了将近3/4的周期资源而使系统得到优化,效果非常显著。

根据以上思路,利用公式(1)提前把算好的正弦函数离散值按照相应的地址顺序依次存入芯片内部的ROM区中。本文的设计中采用以上思路,将0~2π一个正弦周期内共有8192个离散点,缩减为0~π/2共2048个离散点,其中相位分辨率为 0.044°。将N作为正弦离散值的地址线,离散点的计算按公式(1)计算:

其中正弦表的内部结构如表1所示。

表1 正弦函数表内部结构表Table 1 Internal structure of sine function

3.2 三相正弦信号的产生原理

由于在设计中采用了一个正弦表,而需要产生三相正弦信号则成为逻辑设计的一个难点与关键点。传统的设计中需要在FPGA内部存储3个正弦函数表,非常浪费芯片的逻辑资源[6]。因此,本文产生三相正弦信号利用了三相分时原理设计。在设计中采用3个可逆计数器,分别在时钟信号的作用下同时进行计数,其计数值作为三相正弦信号在ROM表中的地址。由于产生的三相正弦信号彼此的初相位不同,所以在可逆计数器的作用下,3个可逆计数器的查表方向对于A、B、C三相就各有所不同。其查正弦函数表原理如图2所示。

图2 查正弦函数表原理图Fig.2 The principle figure of finding sine function table

例如,在设计中产生3个初相位为零、相位互差120°的三相正弦信号[7],如图2所示,A相首先从正弦函数表的地址0°开始累加读起,当读到地址90°处,再从地址90°处累减读到地址0°处,这样在A相可逆计数器的控制下,就可以得到周期为π的单向半波正弦信号;C相首先从正弦函数表的地址60°开始递减读起,当读到地址0°处,再从地址0°处递增读到地址90°处,然后从地址90°处递减读到地址0°处,这样在C相可逆计数器的控制下,就可以得到周期为π,初相位滞后A相60°的单向半波正弦信号;同理,B相从正弦函数表的地址60°开始累加读起,在B相可逆计数器的控制下,就可以得到周期为π,初相位滞后C相60°的单向半波正弦信号。这样,通过一个π/2周期的正弦函数表就可以发出3个相位互差60°周期为π的单向半波正弦信号。

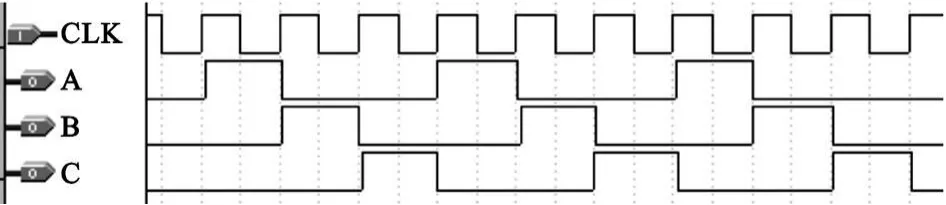

正弦函数表中读取对应的正弦幅值采用分时的方法。其中分时时钟非常小,在不影响正常三相正弦信号的相位关系下,分相逻辑产生器产生的时序如图3所示,其中CLK为输入系统时钟,分相逻辑产生器输出 A、B、C 3个依次滞后的时序[8]。当 A为高电平时读取从正弦函数表内读取出A相的正弦幅值;B当为高电平时,读取B相的正弦幅值;C为高电平时,读取C相的正弦幅值。这样,在三相分时逻辑控制器的作用下,将查出的3个单相半波正弦信号送给正弦信号幅值调节器。

图3 三相分时逻辑时序图Fig.3 The logic time sequence figure of three-phase time-sharing

将3个单相半波正弦信号调整为周期为2π的正弦信号,利用公式(2)和公式(3)就可以调节为正常的正弦信号:

这样,3个单相半波正弦信号就调整为成为相位彼此互差120°的三相正弦信号。

3.3 相位的调节方法

M作为相位控制字输入信号,将输入信号M作为正弦函数ROM表的偏移地址。当系统要求发出超前参考信号的角度时,首先超前与滞后标志位变为“1”。可逆计数器查表地址从初始位置对应偏移到ROM表地址[9]。如果M=“01010101011”(即 δ=683为相对偏移地址,实际 M=683×0.044°=30°),A相可逆计数器首先从地址“01010101011”处先递增计算,递增到“11111111111”处就开始递减计算,计算到地址“00000000000”处再递增计算,在时钟的作用下往复计算。B相可逆计数器从地址1365+683处(1365为 60°地址)递减计数;同理,C相可逆计数器从1365+683处递增计数。这样,输出的正弦信号比参考信号超前30°。同理,发出滞后电网电压信号的正弦信号只需采用与超前相反的方法。由于在正弦函数ROM 表中存储了(0°~90°)的正弦函数值共2048个离散点,M的调节范围在(-90°~+90°)之间,相位分辨率为 0.044°。

4 实验结果

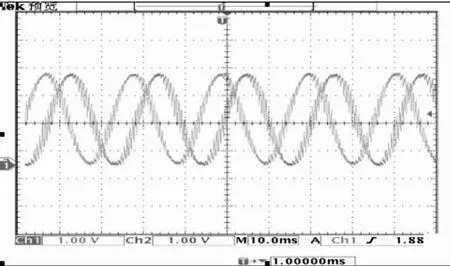

将编译好的配置文件下载到FPGA芯片中,用示波器来观测输出波形。图4为A相与B相LPF滤波后的波形图,可以看出A相与B相彼此相位保持120°的相位关系,证明输出三相波形的相位是正确的。

图4 两相输出120°波形图Fig.4 The 120°waveform figure of two-phase output

在实际应用中,通过改变频率控制字的大小就可以改变输出频率[10]。本文利用FLEX10K器件设计了相应的三相正弦DDS电路,对实验电路进行了全面检验。实验结果表明,整体逻辑设计是正确的,输出的三相波形相位符合设计要求的控制。

5 结束语

本文根据实际需要,设计出了符合特定需要的三相正弦DDS电路,通过实验证明,输出波形达到了技术要求,控制灵活,性能良好。该方法较传统方法具有良好的实用性和灵活性,有很好的推广价值。本文下一步的工作是利用FPGA设计并实现出符合特定需要的方波或三角波DDS电路,并且频率可调节。

[1]Zbigniew Bielewicz,Leszek Debowski.A DSP and FPGA Based Integrated Controller Development Solutions for High Performance Electric Drives[J].Proceedings of the IEEE,2009,16(2):679-684.

[2]Shih-Liang Jung,Meng-Yueh Chang.Design and Implementation of a FPGA-Based Control IC for AC-Voltage Regulation[J].IEEE Transactions on Power Electronics,2009,14(3):522-532.

[3]侯波亨,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,2010.HOU Bo-heng,GU Xin.VHDL and digital logic circuit design[M].Xi′an:Xidian University Press,2010.(in Chinese)

[4]Vankka J.Methods of mapping from phase to sine amplitude in direct digital synthesis[C]//Proceedings of the 1996 IEEE International Frequency Control Symposium.Honolulu,HI,USA:IEEE,1996:942-950.

[5]刘薇,王建立.基于FPGA与单片机的波形发生器设计[J].微计算机信息,2008,64(15):198-199.LIU Wei,WANG Jian-li.Design of waveform generator based on FPGA and single chip[J].Microcomputer information,2008,64(15):198-199.(in Chinese)

[6]刘诗华,王德石,谢邦勇.基于DDS的混沌调相信号生成方案[J].系统工程与电子技术,2009,55(4):26-28.LIU Shi-hua,WANG De-shi,XIE Bang-yong.Scheme of chaos phase modulation signal Generation base on DDS[J].Systems Engineering and Electronics,2009,55(4):26-28.(in Chinese)

[7]曹群,颜德田.基于DDS的中功率低频信号源的设计[J].电子测量技术,2009,38(5):14-16.CAO Qun,YAN De-tian.Design of middle power lowfrequency signal source based on DDS[J].Electronic Measurement Technology,2009,38(5):14-16.(in Chinese)

[8]冯源,樊祥,胡涛涛,等.基于DDS技术的通信激励器设计[J].通信技术,2010,34(11):126-128.FENG Yuan,FAN Xiang,HU Tao-tao,et al.Designof communication prompting source based on DDS technology[J].Communication Technology,2010,34(11):126-128.(in Chinese)

[9]袁纵横,魏常伟.基于DDS的高功率超声波电源的设计[J].电力电子技术,2010,26(11):46-49.YUAN Zong-heng,WEI Chang-wei.Designof high power ultrasonic wave supply based on DDS[J].Power Electronics Technology,2010,26(11):46-49.(in Chinese)

[10]杨蕾.基于DDS的高码速率遥感卫星模拟信号频综源设计与实现[J].电子器件,2009,56(12):66-69.YANG Lei.Design and implement of high bit rate remote sensing satellites analog signal source based on DDS[J].Electronic Devices,2009,56(12):66-69.(in Chinese)