门控时钟单元IP核设计

2009-01-20陈志强潘兰芳韩安太吴秀山

陈志强 潘兰芳 韩安太 吴秀山

摘要:门控时钟是VLSI设计中降低功耗的一种主要技术,将门控时钟设计为一个独立的IP,可以降低设计的复杂性。在对门控时钟的基本工作原理和结构分析的基础上,本文给出了将门控时钟单元电路设计为一个独立IP核的设计流程,并生成了系统物理设计和验证阶段所需要的库文件。设计结果已成功地应用于高性能、低功耗嵌入式CPU的设计。

关键词:门控时钟单元;IP核;低功耗;静态时序分析

中图分类号:TN47 文献标识码:A

1引 言

在同步电路中,每个时序单元都有一个时钟信号,时钟信号通过时钟网络连接到各个时序单元,时钟网络能够提供足够的驱动并且能将时钟偏移控制在一定的范围内。但是由于时钟信号在系统工作期间不断地翻转,以及时钟网络的产生使线网电容增加,导致系统功耗增加,当时序单元中寄存器的状态不需要改变或者一些功能模块(如ALU,内存,FPU等)在某一个时间段空闲时,关闭其时钟信号是降低时序电路时钟信号功耗的一种有效途径。有研究表明,数字计算机中时钟信号的功耗占总功耗的15%-45%之多[1]。

门控时钟技术[1-4]能够有效减少电路中的冗余翻转,将空闲电路模块的时钟信号临时关闭以减小电路的功耗,是一种重要的降低时钟信号功耗的方法。通常门控时钟引入是在设计的逻辑综合阶段,加入门控时钟综合脚本,在设计中插入门控时钟结构。但是门控时钟结构中有一个锁存器,这样在综合阶段和后续的静态时序分析(STA)、自动测试模式生成(ATPG)、时钟树综合(CTS)等步骤中都要特别考虑门控时钟结构,增加了后续工作量,延长了设计的tape-out时间。但是如果将门控时钟结构做成一个独立的IP(Intellectual Property,知识产权),就能像标准单元一样使用,降低了设计测试的复杂性[4]。

本文详细分析了门控时钟的基本工作原理和组成结构,并给出了将门控时钟单元电路设计为一个独立IP的流程。设计的门控时钟单元IP核已成功地应用于嵌入式CPU-CKxxx(xxx为隐去的型号)的设计中。

2门控时钟基本工作原理和结构

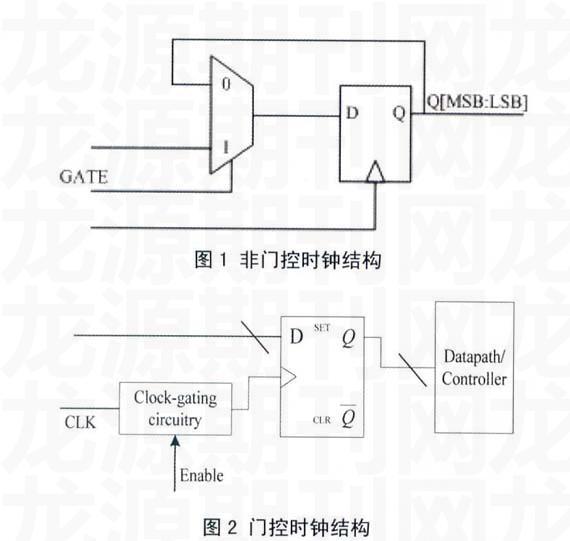

ASIC设计中一般采用上升沿触发的D触发器来组成寄存器和/或存储单元,如果D触发器要保持前一个状态的值,一般采用如图1所示的MUX电路。

在图1中,当寄存器状态需要改变时,GATE端使能,输入端信号通过MUX进入D触发器,触发器的时钟一直有效,即使在GATE关闭时,D触发器也在工作。在存在大量的总线和寄存器组的设计中,这些冗余的翻转会消耗大量的功耗。如果可以使用一个门控时钟单元替代MUX,芯片的面积也将减小,功耗也就相应降低。

门控时钟的基本原理如图2所示。当Q值相对于前一个时钟周期保持稳定或者不需要数据通路的输出时,使Enable=0,屏蔽时钟信号CLK,否则Enable=1,使电路处于正常工作状态。

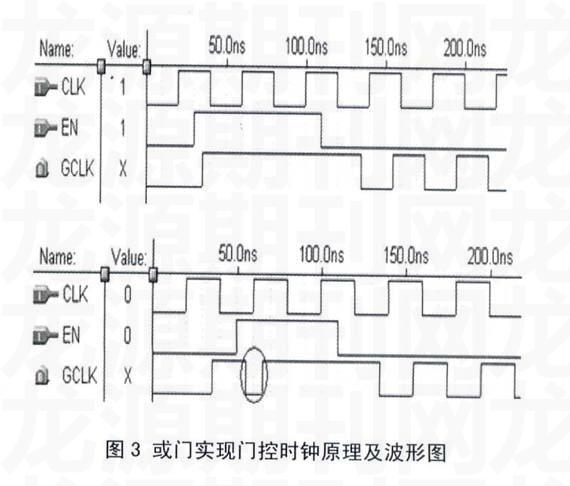

对于上升沿触发的触发器,门控时钟的原理如图3所示,它在逻辑功能上与图1所示的电路相同,当EN=1时,时钟信号被屏蔽,GCLK端没有时钟信号;当EN=0时,时钟信号正常。但是,必须保证EN在时钟的前半周期达到稳定。

如果改用与门实现上升沿触发器的门控时钟,即使EN在时钟的前半周期达到稳定,GCLK也会出现毛刺,所以上升沿触发器的门控时钟一般利用或门实现。但是如果,EN信号在时钟的后半周期达到稳定,也会有毛刺出现。为了解决这个问题,在或门的前面加一个锁存器,这样不管EN信号何时达到,毛刺都不会传递到GCLK可以阻止。

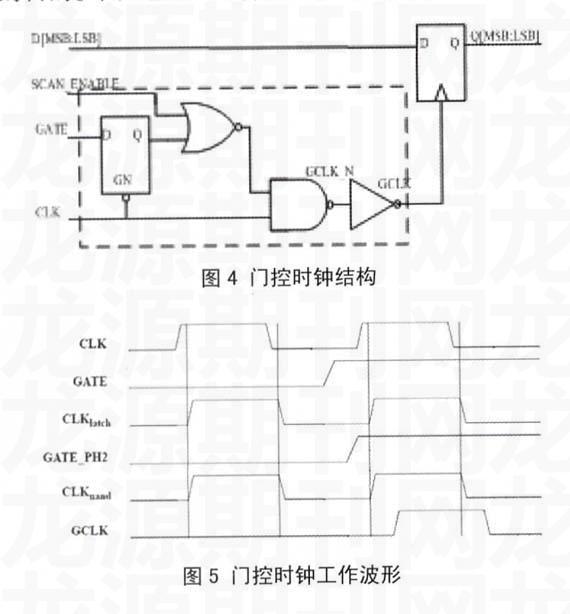

图2中虚线框内是改进后的门控时钟结构,引入锁存器以后,要将或门改为与门,否则GATE信号为高电平时会将时钟信号屏蔽,导致时钟信号不能达到GCLK端。锁存器保证了GATE信号只有在CLK发生当D触发器的状态不需要改变时,GATE信号为0,这时GCLK端没有时钟信号,触发器的状态保持不变,这样就可以使D触发器在状态不需要改变时关闭触发端的时钟信号,从而达到降低功耗的目的。图5显示了门控时钟工作波形。

3建立门控时钟单元

由于Foundry提供的免费单元库没有门控时钟单元,为了节约设计成本,门控时钟单元需要自行设计。一个完整的门控时钟单元库需要建立以下库文件:用于版图编辑的GDS2文件、用于综合和布局布线的timing model(*.db格式和*.lib格式)和LEF文件、用于LVS的spice网表。下面给出基于TSMC18标准单元库将图2所示的结构设计为一个物理门控时钟结构单元的步骤。

3.1 门控时钟单元结构的Verilog HDL描述

下面为一个逻辑时钟单元的Verilog硬件描述:

#file name: gated_cell.v

module gated_cell (clk_in, SE, external_en, clk_out);

input clk_in, SE, external_en;

output clk_out;

wire clk_en_af_latch, n1;

TLATNX4 clk_en_af_latch_reg ( .D(external_en), .GN(clk_in), .Q(clk_en_af_latch) );

OAI21X4 U1 (.A0(SE), .A1(clk_en_af_latch), .B0(clk_in), .Y(n1) );

CLKINVX20 U2 ( .A(n1), .Y(clk_out) );

endmodule

其中clk_in, SE, external_en和clk_out分别对应于图2中的CLK, SCAN_ENABLE, GATE和GCLK,实例TLATNX4, OAI21X4和CLKINVX20的尺寸是根据全局设计中的驱动能力在标准单元库中选择的。

3.2 产生门控时钟单元的版图描述GDS2文件和LEF文件

利用商业化的布图布线工具产生门控时钟的GDS2文件。这里以CADENCE版图设计工具SE来说明门控时钟的版图描述GDS2文件的设计过程。

(1) 读入标准单元库的LEF(Library Exchange Format,库交换格式)文件;读入标准单元库timing model GCF(General Constraints Format)文件;读入门控时钟单元的Verilog HDL网表文件和标准单元的Verilog HDL网表文件tsmc18.v。

(2) 初始化预布局(initialize floorplan),放置设计单元,布线。

(3) 在SE中导出门控时钟单元的GDS2文件和LEF文件。

(4) 这里产生的GDS2文件是通过读入标准单元的LEF文件产生的,不包含其中三个标准单元的版图信息。所以要将SE导出的GDS2文件和Foundry提供的标准单元的GDS2文件读入CADENCE的工具Virtuso,然后从Virtuso中再导出包含三个标准单元版图信息的完整的GDS文件。生成的版图如图6所示。

3.3 Timing model的产生

Timing model提供单元的时序信息,在物理设计阶段用于时序分析和时序优化。Primetime是SYNOPSYS公司的静态时序分析工具,这里借助Primetime来提取门控时钟单元的Timing model。下面给出了min/max时序分析分析用Timing model的产生步骤,独立的min,typical,max分析用的Timing model的产生步骤也是如此,只不过产生过程用的命令有些许变化(可以参考SYNOPSYS的帮助文档)。

(1) 定义搜索和连接路径;读入标准单元库的timing model文件

用到的命令:set link_path; set search_path; read_min_max_lib。

(2) 读入门控时钟单元的Verilog HDL描述设计,设定连线模型和运行环境,设定时钟信号。

用到的命令:read_db; link_design; set_wire_load_model; set_operating_conditions; create_clock.

(3)提取门控时钟的timing model。

命令和设定如下:

set extract_model_conservative true

set extract_model_tolerance 0.02

set extract_model_transition_limit 5.0

set extract_model_capacitance_limit 64

set extract_model_min_resolution 0.01

set extract_model_min_delay_threshold 35.0

extract_model -output ./model_min_max

-operating_conditions {MAX MIN}

-format {db lib}

-library_cell

- test_design

(4)打开产生的*.lib文件,将对应的引脚名改为图中所示引脚名。由于*.lib文件可以进行编辑而*.db文件不能,所以将修改后的*.lib文件再读入Primetime,重新提取修正过的db文件。

3.4 LVS用的spice网表文件的产生

运用MENTOR公司的Calibre生成门控时钟单元的SPICE网表文件,产生的网表文件用于对这个设计进行LVS时引用。命令格式如下:

v2lvs –v ./verilog/clock_gating_cell.v –o ./lvs_netlist

/clock_gating_cell.sp

经过以上步骤,生成了物理设计阶段门控时钟单元的库文件,利用这些库文件,就能够在设计中将建立的门控时钟单元像标准单元一样使用。在布局布线优化、时序优化和功耗优化时不需要额外考虑门控时钟单元具体版图信息、时序信息。

4门控时钟单元在嵌入式

低功耗高性能CPU-CKxxx中的应用

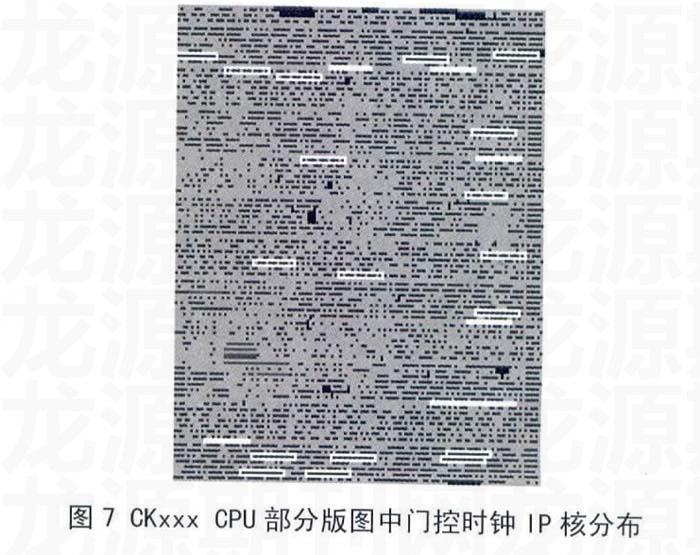

CKxxx(xxx为隐去的型号)是一个“32位高性能低功耗嵌入式CPU,其中包含大量的总线和寄存器组,这种结构适合于使用门控时钟,由于使用一个门控时钟单元IP可以替代多个MUX,减小芯片面积,降低芯片物理设计的复杂性。利用上述流程设计的IP已成功地应用于CKxxx的设计中,图7中白色的框为门控时钟IP核单元的分布。

流片后的测试表明,采用门控时钟单元IP设计的CKxxx工作正常。门控时钟单元IP在CKxxx设计中的应用,降低了STA的复杂性和其它后续的工作量,缩短了该芯片的tape-out时间,降低了芯片了功耗和面积,提升了设计的时序性能,提高了产品的整体性能。

5结论

将门控时钟单元电路设计成一个独立的IP,可以降低芯片物理设计阶段的复杂性,减小芯片的面积,提升系统的时序性能,保证设计的成功率。首先根据门控时钟结构的Verilog HDL描述,在TSMC18工艺库的基础上生成了逻辑综合阶段所需要的库文件,时序分析所需要的Timing model,版图描述GDS2文件和LVS用的SPICE网表文件。该门控时钟单元在嵌入式低功耗高性能CPU中的成功应用说明了本文的设计的单元是正确的、有效的。

参考文献

[1] Qing Wu, Pedram M, and Xunwei Wu, Clock-gating and its application to low power design of sequential circuits[J]. Circuits and Systems I: Fundamental Theory and Applications, IEEE Transactions on, 2000. 47(3): p. 415-420.

[2] Mukheijee A and Marek-Sadowska M. Clock and power gating with timing closure[J]. Design & Test of Computers, IEEE, 2003. 20(3): 32-39.

[3] Darren Jones, How to successfully use gated clocking in an ASIC design[C]. Boston: SNUG report, 2002.

[4] Synopsys, Power Compiler User Guide. 2003.

[5]Gray, Yeap K. Practical low power digital VLSI design[M]. Massachusetts: Kluwer Academic Publishers Group, 2001(2).

[6] 张永新, 陆生礼, 茹邦琴.门控时钟的低功耗设计技术[J].微电子学与计算机.2004, 21(1):23-26

作者简介

陈志强,博士,主要研究方向为超大规模集成电路低功耗设计研究及物理设计。