基于片上PLL时钟的at-speed测试设计

2009-01-20孙大成

孙大成

摘要:深亚微米制造工艺的广泛采用及越来越高的芯片工作频率,使得具有时序相关的芯片缺陷数量不断增加,at-speed测试成为对高性能电路进行测试的必要技术。文章首先介绍了at-speed测试的故障模型,以及具体测试方法,然后详细介绍了采用PLL时钟作为at-speed测试时钟时,一款芯片的at-speed测试实现方案,最后采用Fastscan及TestKompress对整个设计进行了测试向量自动生成及向量压缩。实验结果表明此方案可行,采用TestKompress进行设计更符合目前的设计需求。

关键字:At-speed测试;可测性设计;自动测试向量生成

中图分类号:TN95

文献标识码:B

1引言

现今的集成电路制造广泛采用深亚微米工艺技术,这使得与时序相关的缺陷的数量越来越多。通常的测试方法即采用stuck-at故障测试和IDDQ测试相结合的测试方法,在90 nm以下工艺时,已经不能够充分地剔除具有时序相关缺陷的芯片。At-speed测试技术应运而生,利用全速工作时钟,采用对跳变故障(transition faults)和路径延时故障(path-delay faults)的测试,成为高性能电路测试的必需技术。

At-speed测试时钟频率与功能模式下的时钟频率相当,比传统stuck-at测试的时钟要快很多。At-speed测试时钟可以通过两种方法提供:第一种直接从管脚输入,由外部的自动测试仪(Automatic Test Equipment,ATE)提供;第二种由片内产生,比如PLL提供。如果采用从外部ATE产生高速测试时钟的方法,则对ATE的要求比较高,需要高速的ATE,相应的测试成本和电路封装的成本会显著增加,特别是在电路运行频率达GHz的情况下,这种影响尤为突出。为了降低测试成本,可以采用第二种方法,这种方法的基本思想就是利用片上的时钟源,如PLL,产生at-speed高速测试脉冲,而ATE只提供慢速的移位时钟和测试控制信号。这种片上测试时钟产生的方法即经济又有效,所以得到工业界的青睐,逐渐成为很多公司标准的产品测试方法。

然而,基于扫描的at-speed测试在自动测试向量生成(ATPG)中会显著增加测试向量的大小。这是由于激活并传递at-speed故障的过程要比stuck-at故障复杂很多。所以,为了降低测试成本,需要对at-speed测试的测试向量进行必要的压缩。同时要指出的是:也正是因为这种复杂性,对at-speed测试向量进行压缩的效果会比对stuck-at测试向量进行压缩的效果要差不少。

本文针对一款包含11万个寄存器的芯片,详细介绍了完整的at-speed测试方法。

2At-speed测试技术

At-speed测试针对的故障模型包括transition故障和path-delay故障。Transition测试针对的是transition类型的故障,即电路某一节点是否能在规定的时间内完成从低到高或从高到低的跳变。Path-delay故障则是对于某一条信号路径而言,在路径起点发生信号改变后,路径终点是否能在规定的时间内完成相应的跳变。对电路的中所有的路径都进行测试是不现实的,因为随着电路规模的增加,路径数量会显著增加。因此通常的做法是采用静态时序分析工具分析出电路中一定数量的关键路径,然后只对这些关键路径产生path-delay测试向量。大多数关键路径的起点和终点位于时序元件,只有小部分路径起点位于源输入,终点位于源输出。

对于两种故障模型来说,at-speed测试都包括测试向量移位输入(shift-in)、条件触发(launch)、响应捕获(capture)、结果输出(shift-out)几个阶段。根据条件触发与测试向量移位输入之间的时序关系,at-speed 测试又可以分为launch-off-shift 测试和broadside测试。

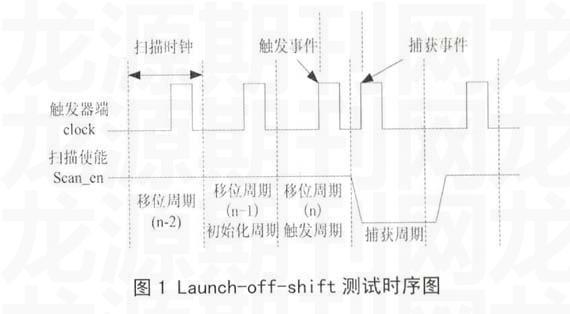

launch-off-shift测试方法如图1所示。在shift-in 的最后一个时钟沿,测试向量完成移位输入,同时也在at-speed 测试的源产生所需的逻辑跳变(launch)。然后在紧接着的下一个时钟沿完成capture。shift-in 的最后一个时钟沿和capture 的时钟沿之间为一个at-speed 测试时钟的时钟周期,而不是用于shift-in 的时钟周期。launch-off-shift 测试的优点是测试向量的生成比较简单,易于达到较高的测试覆盖率。缺点是在布局布线时要把扫描使能信号(Scan_en)与时钟信号一样进行时序优化。由于Scan_en的fan-out 很大,实际上很难对Scan_en信号进行时序优化或需要占用过多的资源。

Broadside测试方法如图2所示。在功能模式即Scan_en为0时,采用一对at-speed的时钟脉冲。这种方法的优点是对Scan_en信号的时序要求大大降低,缺点是:因为源跳变是由芯片本身的逻辑产生的,这必然导致测试向量生成的算法较复杂,难以达到很高的测试覆盖率。

3PLL控制电路设计

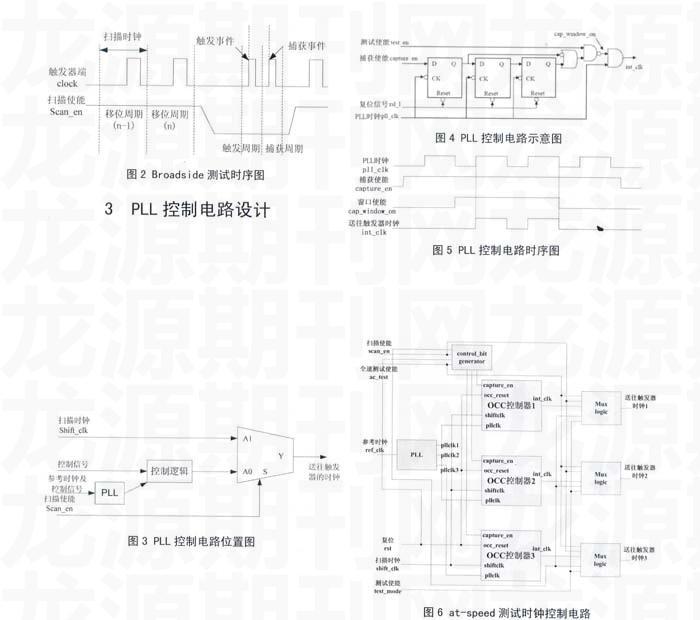

对PLL电路进行控制的方法有多种,本文采用文献[1]描述的,采用捕获窗口生成2个捕获时钟的方法。PLL控制电路在RTL阶段就插入到代码中。如图3中粗线部分所示,该图表明PLL控制逻辑在电路中的插入位置。从ATE输出的测试时钟shift_clk用于扫描操作,PLL时钟经过控制逻辑电路,产生用于捕获数据用的两个背靠背脉冲。

为了保证Scan_en为0的阶段能够产生两个快速时钟脉冲,可以采用如图4所示的PLL控制逻辑电路。其时序关系如图5所示。

该PLL控制逻辑,通过将capture_en置为高电平,触发电路在4个PLL时钟周期内可以在int_clk端产生两个背靠背的脉冲串输出,随后再将capture_en置为低电平。

在本文的设计中,PLL有三路时钟输出,所以需要例化3个控制逻辑电路,以达到对不同时钟的控制。这样就需要3个capture_en信号,针对这种情况,我们设计了一个加法计数器,通过计数器达到在不同计数值的情况下,激活相应的capture_en位。具体电路结构如图6所示。参考时钟ref_clk经过PLL输出3路时钟,每路时钟都单独对应一个时钟控制电路,窗口使能信号由专门的控制位生成器通过计数产生,ac_test信号用于决定是否进行at-speed测试选择。

4采用TestKompress进行ATPG

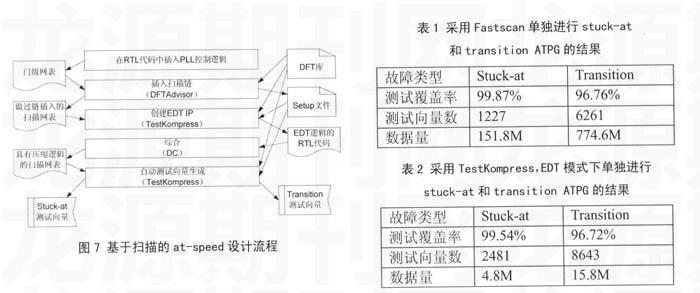

通过ATPG过程生成的at-speed测试数据量很大,很容易超过测试机的存储容量,测试成本也会很高,所以必须对测试向量进行压缩。我们采用Mentor Graphics公司的Fastscan和TestKompress进行了测试向量生成和向量压缩,结果表明该TestKompress拥有优异的数据压缩能力。

本文针对的设计采用基于扫描的at-speed设计流程如图7所示。

由于PLL控制逻辑电路是手动加入,和链插入过程完全独立,造成无法通过procedure文件将PLL控制逻辑的信息自动传递给ATPG工具。对于TestKompress和Fastscan来说,可以通过Named Capture Procedure技术对procedure文件进行修改,来达到信息传递的目的。具体到Named Capture Procedure及procedure文件的修改,见参考文献[2]。