一种基于GaAs和FO-WLP工艺的异质异构集成PDK

2024-04-22董泽瑞陈展飞

董泽瑞,陈展飞,刘 军

(杭州电子科技大学浙江省大规模集成电路设计重点实验室,浙江 杭州 310018)

0 引 言

近年来,随着对电子系统微型化高密度、多样化功能、高性能和低成本日益增长的需求,为实现不同工艺、不同材料和不同工厂的协同设计,异质异构集成技术已然成为电子技术重要研究方向之一[1]。

随着信息技术的高速发展,半导体行业诞生了很多高性能的半导体材料,以GaAs和GaN为代表Ⅲ-Ⅴ族化合物半导体材料具有禁带宽度较宽、电子迁移率高、高热导率、低噪声等显著特点,表现出更优异的高频器件性能,满足集成电路日益增长的性能要求[2]。然而,由于单一半导体材料具有一定的局限性,难以满足高信息化装备的需求。异质异构集成技术可将基于GaAs、GaN等化合物材料的高性能有源器件、高性能无源器件、硅基电路模块与树脂基电路模块等,集成为一个完整的异质异构集成电路,充分发挥各种材料、结构以及器件的优势。本文采用一种异质异构集成技术,扇出型晶圆级封装(Fan-out Wafer Level Packaging,FO-WLP),其在封装体积、产品性能、封装成本和封装效率上都具有明显优势,并且可以将不同功能的芯片集成在一起,显著提高产品性能[3]。

为了支持不同工艺的电路协同设计,提高异质异构集成电路设计效率,避免不必要的重复流片,设计人员非常需要通用并且准确的异质异构集成工艺设计套件(Process Design Kit,PDK)[4]。PDK是联系集成电路(Integrated Circuit,IC)设计与晶圆代工厂(Foundry)的重要桥梁[5],其中包含了一系列完整的工艺信息文件、基础器件库和器件模型文件,并且可以确保其满足Foundry的设计规则检查(Design Rule Check,DRC)、版图与原理图的匹配检查(Layout Versus Schematic,LVS)[6]。

异质异构集成PDK相较于之前传统工艺PDK更困难复杂,主要表现在异质异构集成的工艺多样,可开放度不一致,标准工艺定义困难,精确电/磁/热仿真困难。2016年,为了实现将多种化合物半导体的优势与CMOS集成电路的优势结合,实现全新架构的高性能集成芯片,在美国国防部高级研究计划局(Defense Advanced Research Projects Agency,DARPA)主导的多样化可用异构集成(Diverse Accessible Heterogeneous Integration,DAHI)项目中,诺斯罗普·格鲁曼航天系统公司(Northrop Grumman Aerospace Systems,NGAS)基于统一的设计平台和分散的工艺平台,将化合物半导体器件、以及其它新材料和器件与高密度硅基CMOS基板集成,显著减小了尺寸、重量和功耗,实现颠覆性的高速电子器件[7]。

然而,由于异质异构集成技术的多样性,目前还没有提出标准的异质异构集成PDK设计方案,为进一步推进异质异构集成电路设计研究,本文提出一种基于GaAs和FO-WLP工艺的异质异构集成PDK。在本文中,研究了该PDK的开发难点和开发方法,同时该PDK对异质异构集成技术文件、器件模型、Pcell和物理验证文件进行创新并提供了支持。最后,使用该异质异构集成PDK设计单刀双掷开关及其封装电路并进行仿真验证。

1 异质异构集成PDK开发难点和开发方法

在Advanced Design System(ADS)平台下开发基于GaAs和FO-WLP工艺的异质异构集成PDK,提供处理多种工艺集成的电路封装设计流程的完整解决方案,实现工艺数据与设计环境的无缝集成,提高电路封装设计效率,缩短生产周期[6]。该异质异构集成PDK基本结构框架包含:

Symbols:用于电路原理图设计的图形符号,是电路原理图仿真时器件的载体,用户通过调用Symbols,对器件进行各项参数的配置。

CDF(Component Description Format)参数:器件的属性描述文件,用于定义器件名称、器件参数等各种与器件属性相关的内容[8]。

Callback函数:器件参数调用关系函数。器件所有参数的设置,包括相关工艺参数限制范围和器件参数相关联的计算等都由Callback函数来完成计算并回调。

器件模型(Device Model):器件的仿真模型文件。

Artwork:参数化单元Pcell对应的版图文件,用于版图设计。

参数化单元(Pcell,Parameterized Cell):由ADS的AEL语言编写实现,是EDA仿真工具中的设计单元器件,由上述Symbol、CDF参数、Callbak函数和Artwork组成。

技术文件(Technology File):用于版图设计和物理验证的工艺文件,包括图层的属性定义、图层显示颜色定义、衬底信息等。

物理验证文件(PV Rule):包含设计规则检查文件(Design Rule Check,DRC)、版图与原理图比较文件(Layout Versus Schematic,LVS)等。

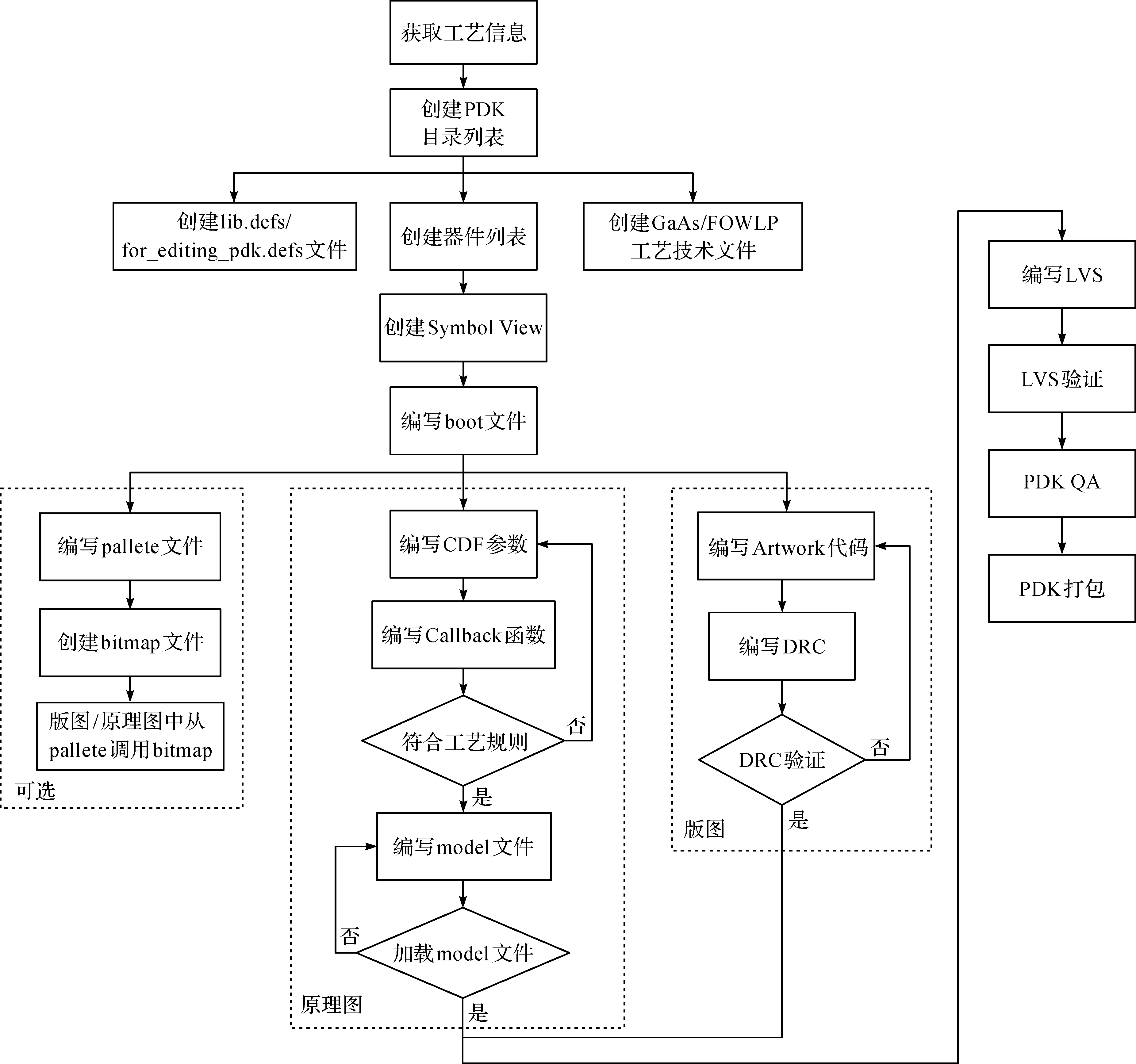

PDK结构框架如图1所示:

由于预算管理的根本目的是使企业能够适应市场发展的需要和市场的变化,加强企业对长期发展战略的确定和实施。通过科学有效的企业预算管理,企业可以在激烈的市场竞争环境下调整自己的行为,并随着市场的变化不断做出有效改变,充分适应市场环境。这要求企业在发展市场环境和企业长远目标的基础上进行预算管理。在具体工作中,首先要以企业自身的发展战略为根本目标,预测不同形势下的市场变化因素,制定相应的经营机制,使企业适应各种变化的市场条件。最后,根据市场变化下企业的实际情况,不断调整,与市场经济同步发展。

图1 PDK结构框架图

异质异构集成PDK的开发难点在于多工艺之间的行交互,例如不同工艺的堆叠、图层、电气和电磁模型交互[9]。不同工艺之间的交互,主要体现在技术文件、Pcell和物理验证文件,需要在一个PDK中同时调用不同工艺的技术文件,并且确保PDK集成多个技术文件不报错。在此基础上设计同时集成两种工艺的器件,主要包含CDF参数、Artwork和器件模型,并执行满足多工艺的物理验证文件无误。

为实现异质异构集成PDK的多工艺集成交互,本文提出了一种结构化的开发方法开发异构集成PDK,这种方法思路清晰、PDK运行速度快、方便迭代维护。通过此方法,技术文件可以降低出错率,Pcell和物理验证文件代码行数显著减少,准确性明显提升,并提供了更高的性能。异质异构集成PDK的整体开发流程如图2所示。

图2 异质异构集成PDK整体开发流程图

2 异质异构集成PDK技术创新

异质异构集成PDK构建在GaAs工艺和FO-WLP工艺信息基础之上[10],支持从电路设计到物理设计验证的整个设计流程。此外,该PDK对异质异构集成技术文件、器件模型、Pcell和物理验证文件进行了创新并提供支持。

2.1 异质异构集成PDK技术文件

异质异构集成PDK技术文件开发的主要难点,在于导入不同工艺时图层编号产生重复冲突和复合工艺衬底文件的开发。

异质异构集成PDK技术文件开发分为两个部分,分别为GaAs工艺技术文件和FO-WLP工艺技术文件,开发方法和传统PDK技术文件类似。异质异构集成PDK技术文件开发特别要注意图层信息不能重复,如有问题需要及时和Foundry进行沟通。然后,将开发完成的GaAs和FO-WLP技术文件有效地组合为异质异构集成PDK技术文件。

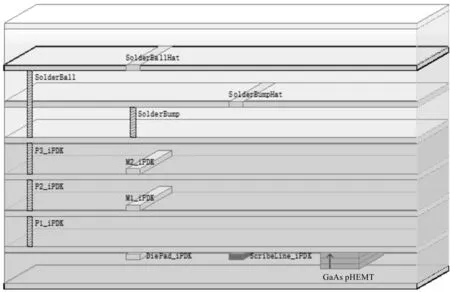

为支持多工艺复合衬底协同EM仿真,在异质异构集成PDK中搭建GaAs和FO-WLP工艺的衬底模型,衬底材料参数由工艺对应的Foundry提供。在FO-WLP工艺衬底上嵌入“Nested Substrate”,添加需要进行联合仿真的GaAs工艺衬底信息,搭建多工艺复合衬底模型,如图3所示。

图3 基于FO-WLP和GaAs复合工艺衬底模型

2.2 异质异构集成pHEMT Pcell

异质异构集成PDK库由许多器件的Pcell构成,每个Pcell由Symbol、CDF参数、Callback函数和Artwork等组成[11],Pcell实际上是一串使用AEL语言编写的代码。如果在ADS版图编辑器中实例化了Pcell的Arwork,设计者就可以修改器件的参数进行电路性能的调整。然而,必须在器件特性允许的参数范围内进行修改,任何小于或大于限制条件的值都将返回到最小或最大限值,并且CDF参数及其Callback函数应在器件的原理图和版图中保持一致。

为了便于后续系统级设计,在GaAs pHEMT Pcell基础上开发一个CDF参数,HIExtType(Yes/No),控制pHEMT器件的Artwork是否启用FO-WLP,其Artwork在GaAs pHEMT基础上,由源漏栅端口引出PAD搭建GaAs芯片,对GaAs芯片进行模塑,通过3层RDL连接GaAs芯片PAD与树脂基PAD,实现GaAs pHEMT器件的树脂基FO-WLP。构建完成的异质异构集成pHEMT器件,允许设计人员从pallete直接拖放器件到原理图和版图上进行仿真设计。图4(a)显示了异质异构集成pHEMT器件的Symbol,源极、漏极和栅极端口及其FOWLP封装在器件Symbol中有标记。图4(b)显示了相同异质异构集成pHEMT器件HIExtType参数为Yes的Artwork。

图4 异质异构集成pHEMT Symbol和Artwork

2.3 异质异构集成pHEMT器件模型

在异质异构集成实际电路应用中,pHEMT器件同样承担着放大信号、信号混频、开关电路等作用,因此要求pHEMT器件应当具备高输出功率,低噪声,高线性度,工作频带宽等电学特性。为提高异质异构集成PDK中pHEMT器件特性在多工艺衬底影响下的准确性,研究了一种基于GaAs和树脂基FO-WLP异质异构集成的pHEMT器件模型。

该异质异构集成pHEMT器件结构上类似于树脂基GaAs pHEMT器件。pHEMT器件的建模,是等效电路模型对器件电热等物理行为的模拟,其在树脂基上表现出不同的RF特性,与衬底的寄生效应有关。在对大信号模型准确建模之前,考虑树脂基衬底寄生效应的影响,对小信号进行建模。异质异构集成pHEMT器件小信号模型的寄生元件分布与器件的物理结构模型紧密相关联,物理结构模型如下图5所示。

图5 异质异构集成pHEMT器件的物理结构模型

异质异构集成pHEMT的大信号模型基于改良的ASM模型开发,ASM是由印度理工学院Khandelwal等人提出的一种物理基模型,用于GaAs,GaN pHEMT器件的精确建模。ASM的核心是量子阱表面势计算,通过表面势推导可以得到全部工作区域内连续、可导的I-V和C-V特性等。模型中所有的参数提取出来之后,将参数值输入ASM模型对应值内得到异质异构集成Model文件。将其集成到异质异构集成PDK,即可进行直流特性与大信号的仿真模拟。

2.4 异质异构集成PDK DRC

设计规则为给定工艺技术的物理设计及其版图连接设置了限制,在电路设计流程中,对于检查错误、降低设计成本和减少设计失败风险具有重要作用。异质异构集成PDK不仅需要同时引入GaA和FO-WLP两种工艺设计规则,并且需要制定关联两种工艺的新规则,以确保两种工艺异构集成的版图设计符合工艺要求。该PDK制定了GaAs工艺顶部金属层GaAs M2和FO-WLP工艺底部金属连接层FOWLP P1的连接关系等设计规则,GaAs M2和FOWLP P1的三维结构连接图如图6所示。GaAs M2和FOWLP P1的连接规则是一种跨越不同工艺的enclosure设计规则,图形示意图如图7所示。

图6 GaAs M2和FOWLP P1的三维结构连接图

图7 GaAs M2和FOWLP P1的enclosure设计规则图形示意图

GaAs M2和FOWLP P1的enclosure DRC开发难点在于,需要同时调用两种不同工艺的图层进行DRC检查。在开发Pcell的过程中GaAs pHEMT和FOWLP的工艺图层信息已经重新在boot文件中完成定义,同时涉及两种工艺DRC的工艺图层运算需要在boot中进行,以确保3D HI PDK的DRC跨越不同工艺可以正常进行检查。

2.5 异质异构集成PDK LVS

LVS确保了集成电路版图设计和电路原理图设计相匹配,尽管有效的DRC验证检查确保了版图设计符合特定的工艺规则,但是不能保证版图信息、器件连接与实际设计电路完全一致,这就需要LVS对版图和原理图的器件类型、器件参数、连接情况进行验证,以确保制造出来预期的电路。异质异构集成PDK LVS开发与传统PDK类似。

器件识别是LVS和寄生提取中的一个关键步骤,用于识别版图中的器件及其连接端口。由于pHEMT的栅极使用肖特基接触,源极和漏极使用欧姆接触,并且端口不能互换,因此我们通过图层定义和运算来识别器件并区分端口。pHEMT耗尽型器件ADS LVS的代码片段如图8所示,通过代码识别版图中的器件识别层及其三个端口,并可以在网表中导出。异质异构集成PDK LVS还有一个关键步骤为连接关系定义,需要对不同工艺芯片/结构界面进行定义,构建其连接关系,以检查版图中跨越不同工艺的连接是否存在问题。

图8 pHEMT耗尽型器件ADS LVS代码片段

3 异质异构集成PDK应用验证

本章节介绍基于GaAs和FO-WLP工艺的异质异构集成PDK的应用验证,以确保PDK的准确性和有效性。使用该异质异构集成PDK中GaAs工艺库,电路设计人员可以使用传统的MMIC设计工作流程来构建和仿真电路,并且可以构建与版图相关联的原理图执行电气仿真。在原理图仿真之后,设计人员可以使用原理图和EM联合仿真来得到更准确的仿真结果。采用异质异构集成PDK设计微波段单刀双掷开关及其FO-WLP电路[12],仿真结果与封装前的设计结果对比,以验证PDK的有效性和准确性。图9显示了微波频段单刀双掷开关的封装电路。图10显示了微波频段单刀双掷开关的封装电路3D结构图。

图9 开关扇出型封装电路图

在通过DRC和LVS验证之后,得到电路封装前后仿真的S参数结果如图11所示。通过对比分析,开关电路封装后的回波损耗S11、S22虽然都小于-13 dB,但由于封装电路中存在电阻、电感引起谐振点偏移,回波损耗趋势和封装前有所差别。开关电路封装后的插入损耗S21和隔离度S31、S32基本和封装前设计结果相吻合。结果证明,本文所设计的异质异构集成PDK具有较高的准确性和可靠性,能满足异质异构集成电路的设计要求。最后将封装完成的单刀双掷开关电路作为IP电路引入异质异构集成PDK,方便后续系统级设计调用。

图11 封装前后单刀双掷开关S参数仿真结果

4 结束语

为进一步推进异质异构集成电路设计研究,本文提出一种基于GaAs和FO-WLP工艺的异质异构集成PDK,经过前期评估测试到后期开发验证,较完整的解决了一些目前异质异构集成PDK开发的技术问题,并验证了该PDK的准确性和可靠性。随着异质异构集成PDK的成功设计和实现,电路研究人员能够从复杂和困难的工作中解脱出来,设计将更加高效。我们相信这个异质异构集成PDK的设计将为电路研究人员提供条件开发创新电路,并为推进异质异构集成电路设计研究发挥重要作用。