导线间距变化对阻抗的影响探讨

2023-09-25宋海波邓伦华

宋海波 罗 松 符 博 邓伦华

[(胜宏科技(惠州)股份有限公司,广东 惠州 516211)]

0 引言

近年来,随着高频高速信号的快速发展,对印制电路板(printed circuit board,PCB)的信号完整性要求越来越严格。其中,阻抗匹配性是至关重要的问题。为保证有效的阻抗匹配性,PCB阻抗控制成为重中之重。然而,随着电子产品不断朝小型化、多功能化等智慧型方向发展,PCB上安装元器件越来越密集,走线设计不可避免地出现阻抗线到铜间距不足的问题,在PCB 制作时经常会忽略线到铜间距对阻抗的影响,导致实际阻抗达不到要求。因此,本文研究了一种能解决导线间距对阻抗影响的方法。

1 术语说明

信号线:用作信号传输载体的走线。一般有两种,分别是微带线和带状线。

接地层:PCB 阻抗中的接地回路层,又称为参考层。

跨层阻抗:信号线与参考层为非相邻层的阻抗。

共面阻抗:接地线在信号线旁边布线,且接地线通过孔连接到相对层上的接地部分的阻抗。PCB 布线设计中,接地线与相对层上的接地部分一般均设计为铜面。

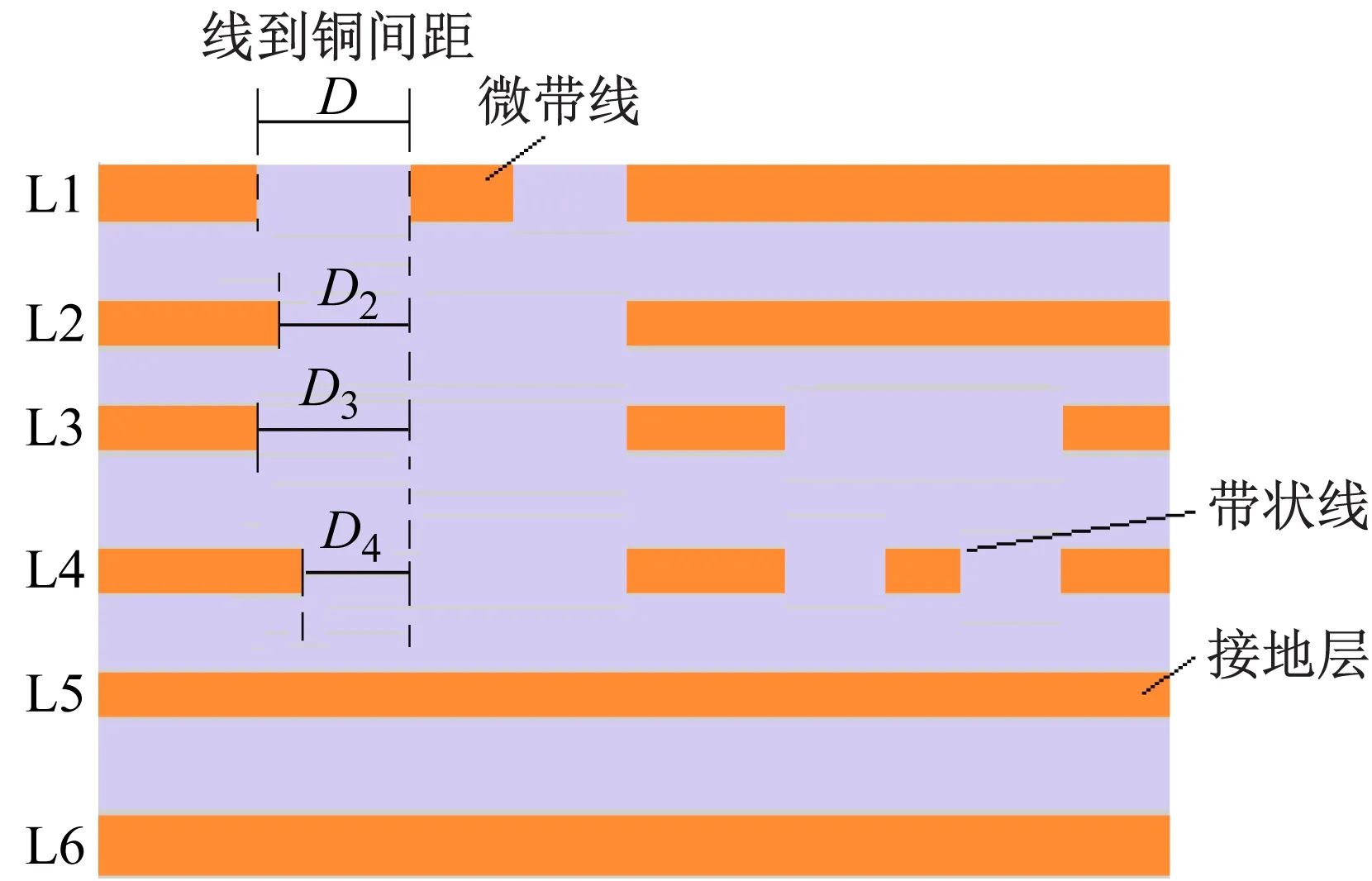

跨越层:跨层阻抗中,信号线与参考层中间所跨过的层次。例如信号线L1 层与参考层L5 层的阻抗模型设计中的L2、L3、L4 层均为跨越层,如图1所示。

图1 阻抗叠构示意图

线到铜间距:阻抗信号线与旁边接地线间的距离。

切面间距:信号线投影部分到跨越层中旁边线路或铜面的距离。

2 基本信息

阻抗基本的要求信息见表1。

表1 阻抗基本信息

3 验证分析

3.1 线到铜间距变化对阻抗的影响

在同一片板上分别设计不同线宽大小、不同的线到铜间距的阻抗,测试验证各种线宽下,线到铜间距的变化对阻抗的影响。通常情况下,阻抗线到铜间距设计为0.50 mm。不同线到铜间距的阻抗量测数据见表2。

表2 不同线到铜间距的阻抗量测数据

3.1.1 验证分析

①随着线到铜的距离变大,对应的阻抗也不断变大,当线到铜距离变大到一定程度时,阻抗基本不变。② 线宽≤0.175 mm 的阻抗,线到铜的距离是线宽的3 倍(约0.50 mm)以上时,阻抗基本不变;线到铜的距离是线宽的2 倍以上时,阻抗的变化较小,在0.5 Ω 以内。③线宽在0.175 mm 以上的阻抗,线到铜的距离是线宽的2倍以上时,阻抗基本不变。

3.1.2 小结

常规阻抗线到铜间距设计最小需满足≤20 mm且是线宽的2 倍以上,否则,需按照共面阻抗方式设计,将线到铜间距代入阻抗计算。

3.2 跨层阻抗中切面间距变化对阻抗的影响

在同一片板上分别设计相同线宽、相同线到铜间距、不同切面间距的阻抗,测试验证不同切面间距的变化对阻抗的影响,其中,线宽0.50 mm,线到铜间距0.50 mm,特性阻抗设计值74.5 Ω。不同切面间距的阻抗量测数据见表3。

表3 不同切面间距的阻抗量测数据

3.2.1 小结

当跨越层L2、L3、L4层中有任意一层的切面间距小于线到铜间距时,实测阻抗值均会小于设计阻抗值74.5 Ω,且跨越层中切面间距越小,对应阻抗实测值越小;当跨越层L2、L3、L4层所有层次的切面间距大于或等于线到铜间距时,实测阻抗值与设计阻抗值74.5 Ω相符合。

因此,跨层阻抗设计中,跨越层任意一层切面间距必须大于或等于阻抗信号线到铜的距离。

4 结语

为了保证阻抗满足客户需求,准确判断阻抗的真实情况,通过间距对阻抗影响的验证分析,PCB非共面阻抗设计中线到铜间距必须≤0.50 mm,且大于线宽的2 倍,跨层阻抗的跨越层切面间距必须大于或等于阻抗信号线到铜的距离。