基于STM32的EtherCAT转UDP通信转换系统设计与实现

2023-08-18殷伟

摘要:工业以太网总线技术EtherCAT是一种基于以太网的高性能、低成本的实时通信技术,它可以实现分布式控制系统的高速、低延迟、同步和确定性的通信。EtherCAT在工业自动化领域有着广泛的应用,如机器人、数控机床、汽车制造等。然而,EtherCAT与工控机端的通信网络一般采用TCP/IP协议,由于其非实时性通信方式,不能直接与EtherCAT从站交换数据,需先进行通信协议转换。通信转换需要借用硬件介质来实现。为了实现EtherCAT与工控机端的TCP/IP协议的互通,本文设计了一种基于STM32单片机的通信转换系统,该系统利用FPGA开发的高速、低延迟、同步和确定性的TCP/IP通信模块,实现了EtherCAT与TCP/IP协议的转换。本文介绍了系统的硬件结构和软件设计,验证了系统的通信性能和效率。

关键词:STM32F103;EtherCAT;FPGA;UDP;通信转换

以太网控制自动化技术EtherCAT在工业自动化领域应用广泛。在工业以太网总线技术EtherCAT中,从站之间的通信采用分布式时钟同步机制,保证了通信的高速、低延迟、同步和确定性。然而,EtherCAT与工控机端的通信网络一般采用TCP/IP协议,由于其需要建立连接和确认数据的传输,无法与EtherCAT直接进行数据交互,导致了通信的非实时性,因此,需借用硬件介质进行通信协议转换。伺服电机、步进电机和输入/输出口的控制过程非常复杂,任何一个控制环节出错都会造成控制系统运行不稳。

在实际产品开发中,考虑成本因素无法直接在控制系统中运行实时分析软件,而是要将相应数据实时地传输到PC机上,通过PC机上的数据采集、分析軟件中查找、定位问题根源。为了实现EtherCAT与工控机端的TCP/IP协议的互通,本文提出了一种基于UDP协议的通信转换方案,利用UDP协议的无连接和高带宽特点,提高通信的效率和速度,同时利用FPGA开发的高性能TCP/IP通信模块,保证通信的实时性和可靠性。

一、系统硬件设计

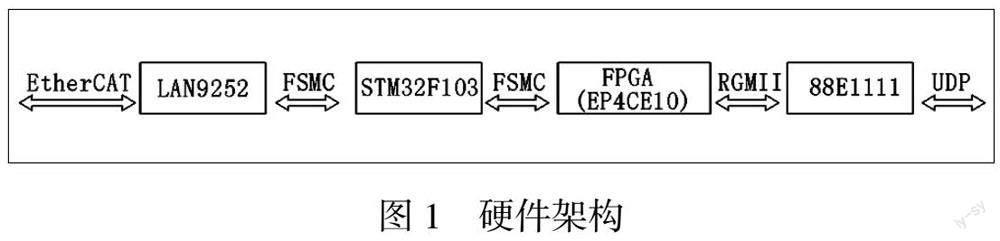

系统的控制部分包括STM32F103、FPGA。STM32F103程序负责控制LAN9252和FPGA的通信,以及配置88E1111 PHY芯片的寄存器。FPGA程序负责实现可变静态存储控制器通信模块、UDP通信模块和88E1111 PHY芯片配置模块。可变静态存储控制器通信模块用于与STM32F103进行数据交换,UDP通信模块用于封装和解析UDP数据包,88E1111 PHY芯片配置模块用于设置PHY芯片的工作模式和速率。整体硬件架构如图1所示。

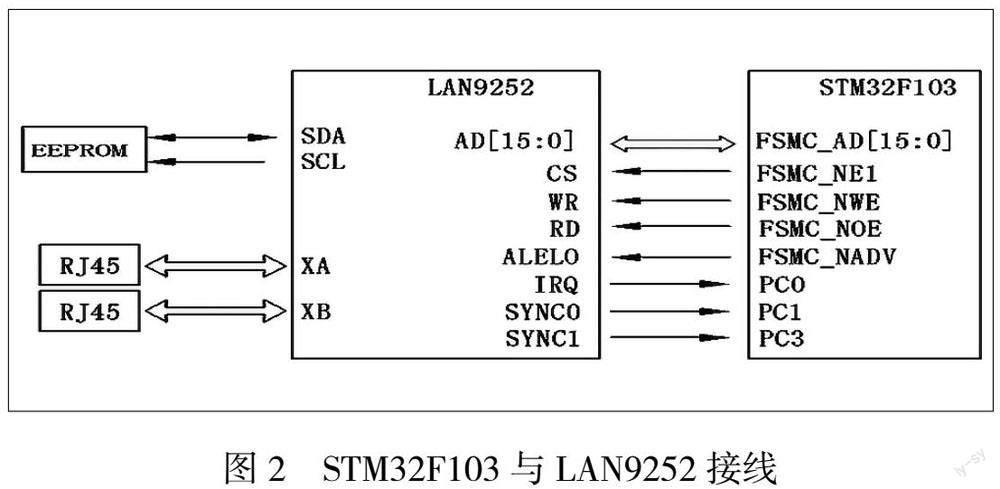

LAN9252和STM32F103的接口电路如图2所示。

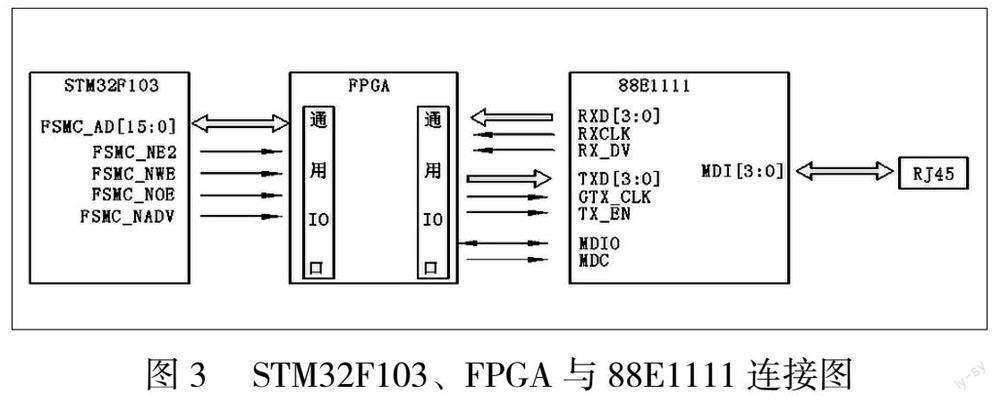

FPGA选用EP4CE10,是一种低成本、高性能的可编程逻辑器件,可以实现复杂的通信协议和算法。FPGA与STM32F103通过可变静态存储控制器总线进行数据交换。

88E1111支持10/100/1000Mbps的自适应速率,具有低功耗、高集成度、高稳定性的特点。88E1111与FPGA通过GMII总线进行数据传输,88E1111与工控机端的网卡通过RJ45接口进行数据通信。STM32F103、FPGA与88E1111连接图如图3所示。

电源采用5 V供电,需要转换成3.3V、2.5V及1.2V。

二、系统软件设计

(一) STM32F103单片机程序

STM32F103是系统的控制核心,用于系统初始化,FPGA、LAN9252模块之间的通信。

为了实现从站微控制单元的EtherCAT通信功能,本文使用SSC工具生成协议栈代码,配置协议栈、物理层之间的接口,如可变静态存储控制器并行总线配置和输入/输出中断入口配置。协议栈包含EtherCAT从站通讯模块输出信号,需将模块的中断处理函数与STM32F103引脚绑定,引脚中断功能关键代码如下。

# define INIT _ESC_INT EXTIO _ Configtiration ( )

# define Ecatlsr EXTIO _ IRQHandler ;

SYNCO 对应中断功能配置及映射

#define INIT_SYNC0_TEXTI3 _ Configoation ( ) ;

#define Syllc0Isr EXTI3_IRQHandler;

SYNC1 对应中断功能配置及映射

#define INIT_SYNC1 _INT EXTI1_ Configuration ( );

#define Sync1lsr EXTl1_ IRQHandler;

为确保引脚快速准确地响应通信模块信号,需要在配置函数中激活引脚的中断功能,并将其映射到外部中断0,设置中断优先级为最高。再配置可变静态存储控制器并行总线,选择异步多路PS随机存取存储器/NOR作为输出通信方式。生成新XML文件之后,需在协议栈代码里,修改数据定义、读取模块,使其与XML生成的数据量一致。在协议栈的数据定义头文件里,修改结构体数据量大小及初始值。生成的协议栈的代码

如下。

typedef struct OBJ_STRUCT_PACKED_ START {

UINT16 ul6SulbIndexo;/ * * < \ brief Sublndex 0* /

UINT32 aEntries [ 32 ]; / * * < \ brief Entry buffer * /

} OBJ_STRUCT_PACKED _END

TOBJ1601;

typedef struct OBJ_STRUCT _PACKED _ START {

UINT16 ul6SubIndex0; / * * < \ brief SubIndex 0* /

UINT32 aEntries [4]; / * * < \ brief Entry buffer * /

} OBJ_STRUCT_PACKED_END

TOBJ 1A00;

在中斷入口函数中修改数据操作,确保数据格式与XML文件保持一致,以免EtherCAT网络通信不能实现初始化。

(二) FPGA程序开发

FPGA主要功能模块包含:可变静态存储控制器通信、UDP收接、UDP发送、PHY配置、以太网MAC,FPGA功能模块如图4所示。

可变静态存储控制器通信模块可以读写单片机的数据,也可以发送和接收UDP数据。读写单片机的数据时,需要进行数据类型转换和缓存;发送和接收UDP数据时,需要解析UDP协议和添加协议头尾。可变静态存储控制器通信模块使用随机存取存储器作为缓存器,单片机接收到一定量的数据后,UDP发送模块开始发送数据。88E1111是PHY芯片,通过FPGA实现标识具体的网络节点。基于ALTERA芯片,可以使用QuartusII提供的TSE IP核。TSE IP核包含数据接收、数据发送、配置和RGMII四个接口,配置接口用于设置88E1111的寄存器和连接方式。UDP协议是一种简单的面向消息的传输层协议,不保证消息的可靠传递,也不维护消息的状态,其优点是简单、快速、灵活,适用于实时性要求高的应用场景,如流媒体、语音、视频等。UDP协议使用16位端口号来区分不同的应用程序,并提供校验和来验证数据的完整性,并且还包含一个伪首部,用于计算校验和实时检查IP地址是否正确。

三、系统调试

系统调试装置如图6所示。

调试的基本步骤如下:

1.应用程序离线调试

在开发环境中使用模拟器或仿真器对STM32F103程序和FPGA程序进行编译、下载和运行,检查是否有语法错误或逻辑错误。使用断点、单步执行、变量监视等功能观察程序运行状态和数据流向,验证程序功能是否符合设计要求。

2.控制系统硬件检查

在目标平台上连接STM32F103单片机、LAN9252芯片、FPGA芯片和88E1111 PHY芯片等硬件设备,检查电源电压、信号线连接、接口匹配等是否正常。使用示波器或逻辑分析仪等工具观察各个总线或接口上的信号波形是否正确。

3.应用程序在线调试

在目标平台上使用JTAG或SWD等接口对STM32F103单片机进行在线调试,使用USB Blaster或JTAG等接口对FPGA芯片进行在线调试,使用网线或无线网卡与工控机端进行通信。使用调试工具或打印日志等方式检查程序运行情况和通信效果,排除可能存在的错误或异常。

4.现场调试

在实际应用场景中对系统进行测试,模拟各种正常或异常的输入输出条件,观察系统的响应和输出结果,评估系统的性能和稳定性,优化系统的参数和配置,解决可能出现的问题或故障。

在完成系统调试后,对调试过程中发现和解决的问题进行总结和归纳,记录调试过程中使用的工具和方法,撰写调试报告和文档,为后续的维护和改进提供参考。

四、结束语

综上所述,设置EtherCAT从站的通信周期为1ms,输入/输出分别为64字节、16字节,在数据中添加递增序列号,通过一段时间的测试观察序列号的变化,EtherCAT从站与UDP通信没有丢包或通信中断现象,具有较高的通信可靠性。

作者单位:殷伟 浙江宁广有视网络工程有限公司

参 考 文 献

[1]左振领,何方,李霄.基于STM32的EtherCAT从站的设计与实现.组合机床与自动化加工技术,2016(7):1-3.

[2]李益,王成杰,史世友,等.基于ZYNQ处理器的EtherCAT从站通信系统设计[J].控制与信息技术,2022(1):59-63.

[3]马保全,姚旺君,刘云龙,等.基于FPGA的EtherCAT从站通信链路分析与验证[J].电子技术应用,2017,43(8):95-99.

[4]Ricardo Moraes,Francisco Borges Carreiro,Paulo Bartolomeu.Enforcingthe timing behavior of real-time stations in legacy bus-based industrialEthernet networks.Computer Standards and Interfaces[J],2011,33(3):5-11.

[5]党选举,李帅帅,伍锡如,等.EtherCAT主站与主站通信协议的研究与实现[J].组合机床与自动化加工技术,2017(1):98-101.

[6]宋孙浩,郑天江,张驰,等.轻量一体化机器人关节的SPI通信及EtherCAT通讯研究[J]. 制造业自动化,2019,41(8):41-46.

[7]康存锋,杜斐斐,马春敏,等.EtherCAT协议芯片与单片机通信系统的研究[J].现代制造工程,2011(7):113-117.

[8]赵世超,左金印,魏骁,等.基于FPGA的万兆以太网UDP协议通信接口设计[J].电子技术应用,2022,48(10):113-117,122.

[9]李浩,赵晨希,关冰.基于超时重传和多重校验的UDP可靠通信设计[J].测控技术,2022,41(2):105-110.

[10]汪钦臣,方益民.基于Modbus UDP协议的STM32与PC实时通信的实现[J].仪表技术与传感器,2020(7):67-70.

[11]柳青.基于Windows套接字的Ethercat主站协议栈设计与实现[J].机电产品开发与创新,2021,34(5):14-15,18.