基于FPGA的通用自动测试平台设计

2023-08-16马绪铎

摘 要:为了实现电子产品在调试、测试中测试指令下发和测试数据获取的自动化,结合FPGA技术、SCPI命令、仪表程控、QT软件开发平台等提出一种通用自动测试平台设计方案,在传统调试测试方式的基础上有效提升测试效率,降低测试成本,实现测试指令下发以及数据处理的一体化和自动化。

关键词:自动测试;FPGA ;SCPI;仪表程控;QT

引言

随着电子信息技术高速发展,数字化、模块化的高集成度电子产品被广泛应用于各个领域,对于产品功能调试,测试验证,售后维修的要求逐步提升。手动使用仪器仪表和测试工装的测试手段落后,效率低下,为了提高生产调试效能,节约多方成本,通用自动化测试平台的研制需求日益递增。合成仪器技术(Synthetic Instruments,SI)是美国国防部为开发新一代自动测试系统提出的关键技术[ 1 ],该技术旨将多种标准仪器仪表通过程控的方式与计算机进行数据交互,实现计算机对仪器仪表的参数设置以及测量结果的自动获取[2-3]。FPGA能够产生满足绝大多数被测电子设备所需的专用信号,如:控制指令、时钟信号等,目前在数据采集处理、逻辑功能实现等多种领域得到了广泛的应用[ 4 ]。本文提出一种基于FPGA的通用自动测试平台设计,通过将合成仪器技术与FPGA技术二者结合,结合目前常用的模块化硬件作为通用自动测试平台的硬件组成[5-6],外观结构为一台便携式加固计算机,通过SCPI命令及VISA I/O库实现对仪表程控设置,上位机软件采用QT平台开发以支持WINDOWS、银河麒麟等多个操作系统,实现跨平台运行。通用自动测试平台能够实现系统的参数设置、测试流程编辑以及数据的自动捕获、处理和可视化显示。

1 通用自动测试平台总体设计

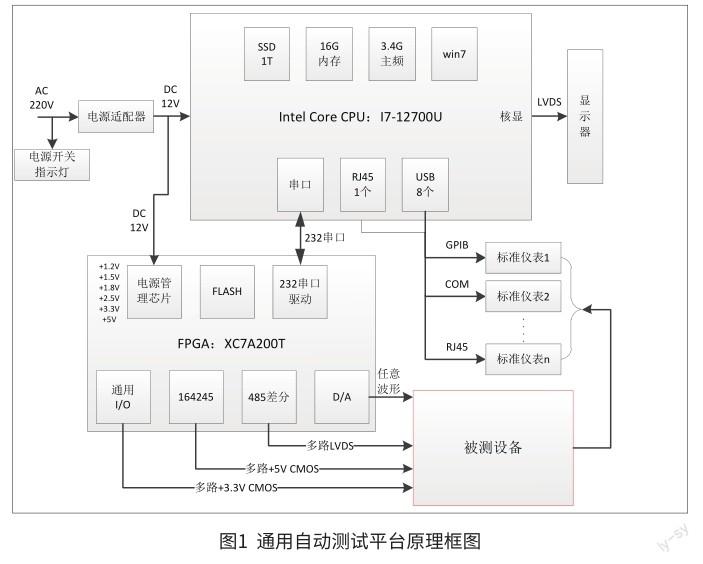

图1是通用自动测试平台的原理框图,AC220V市电经电源适配器后变为12V直流送至计算机主板及FPGA核心板,FPGA核心板中使用DC/DC直流降压芯片构成电源管理组,将DC+12V变为板内其余器件所需的DC+1.0V、+1.5V、+1.8V、+2.5V、+3.3V、+5V等多种电压;核心板上配有256M的FLASH与FPGA通过标准SPI总线连接,便于上电后加载程序。将FPGA的BANK13~16内所有通用I/O引出,部分引脚作为+3.3V CMOS单端信号直接输出,部分引脚通过164245对其进行驱动和电平转换后变为+5V CMOS单端信号输出,其余部分引脚经过485差分转换芯片后变为标准485 LVDS格式信号输出,此外为了满足某些特殊的测试需求,对FPGA的+1.8V及+2.5V内核BANK34/35的输出引脚后端增加D/A模块,能够产生灵活且满足时序要求的任意波形测试信号。FPGA核心板通过232串口与计算机主板之间进行信息交互,接收主板控制指令,回传当前工作状态。计算机主板上配有8个标准USB2.0/3.0兼容接口以及一路RJ45网络接口,能够同时对多路符合IEEE-488.2通用命令的仪器仪表进行远程控制,配置仪表参数,接收测试结果。

2 通用自动测试平台的设计实现

2.1 核心器件的选型及硬件设计

计算机主板选用研华MIO-5272,实物见图2,其內部核心为第七代英特尔 酷睿 U系列CPU,TDP功耗低至15W,双通道DDR3L内存高达16 GB,具有可扩展至8路的USB接口,支持多个GPIB仪表的程控。

FPGA核心板为自主设计且具有丰富种类、可灵活配置的多路输出接口,组成框图见图3。FPGA芯片选用Xilinx公司的XC7A200T-1FFG1156I,该芯片具有200万逻辑单元数量,500路通用I/ O接口,数据速率最高可达6.6Gb/s[7],可提供多类被测产品所需的专用信号,电源管理组选用TI公司的TLV62130直流降压芯片,其支持高达3A的输出电流,通过配置不同的外部分压电阻可获得+0.9V~+5.5V的输出电压,满足核心板内所有器件所需。232串口驱动电路选用MAXIM公司的MAX3232芯片,负责将232电平转换为FPGA_UART要求的+3.3V TTL标准电平。FLASH选用MICRON公司的N25Q256系列芯片,与FPGA之间为标准QSPI总线接口,用于存储可执行bin程序文件,上电加载,FLASH内部可分16个缓存区,对于不同测试的应用,可由上位机的232串口通过指令控制FPGA随时调用FLASH内部的不同bin文件适配不同的测试需求。50MHz晶振选用国产13所的有缘晶振,通过FPGA内部集成的PLL,对50MHz晶振进行20倍频后得到高达1GHz的系统时钟,以高速的系统时钟保证提供给被测设备最小脉宽可达1ns的测试信号。此外,核心板内配有4片16路245电平转换电路SN74ALVC164245、10片4路485差分驱动电路SN75LBC172及2片14位、500Mbis/s高速D/A芯片DAC5675,负责完成FPGA通用I/O引脚+3.3V CMOS至+5V CMOS和485 LVDS的信号转换,DAC5675负责产生部分测试需求的任意波形信号。

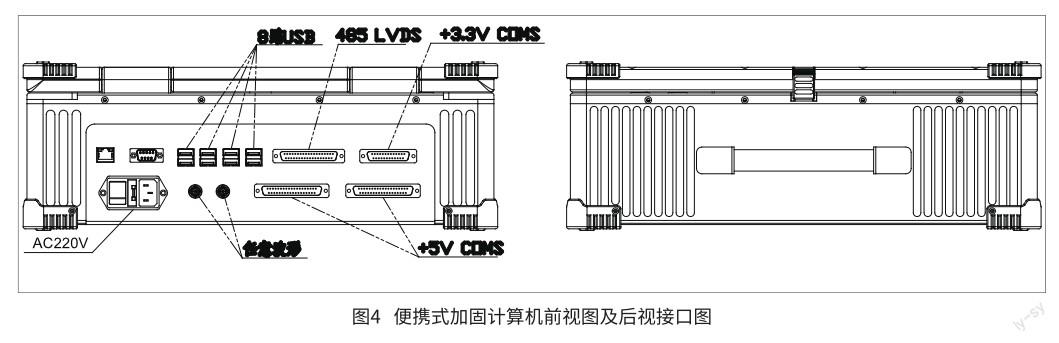

通用自动测试平台采用便携式加固计算机的结构形式设计,外壳采用5106标准金属机箱,内置计算机主板,FPGA核心板及电源适配器,所有接口均在便携式加固计算机后方,USB、网络、串口通过标准接口引出,核心板的输出信号根据信号类型的不同通过不同的矩形连接器引出,D/A后的信号通过BNC/ SMA接口引出。外观示意见图4。

2.2 软件设计

通用自动测试平台软件分为嵌入式FPGA软件及上位机软件两类,嵌入式FPGA软件主要用于提供被测设备所需的专用信号,结合被测设备的测试需求,通过专用接口送出不同电平、不同信号类型的控制信号、时序信号等。上位机仪器仪表程控软件通过标准GPIB接口完成对所需仪表的一键设置,并对测试结果进行采集和分析,实现被测设备性能的自动测试。

2.2.1 嵌入式FPGA软件

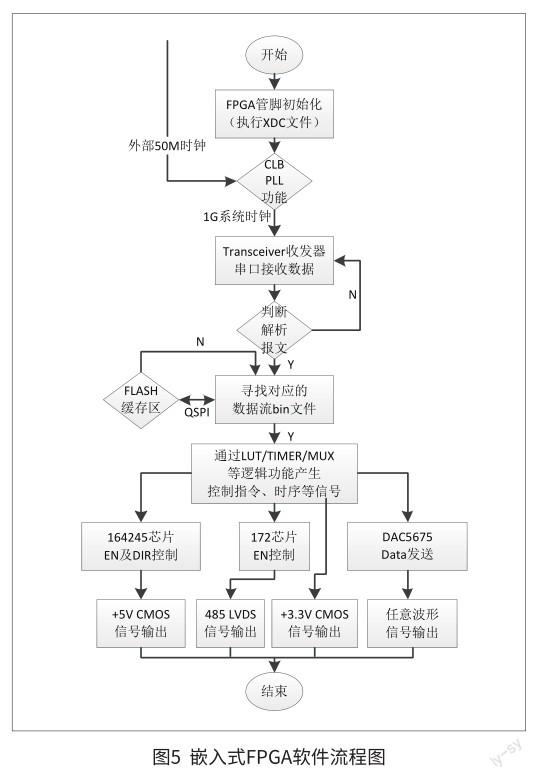

针对FPGA芯片的逻辑功能开发,通过Xilinx的官方软件Vivado作为本次设计的EDA开发平台,使用Verlog HDL语言编程,软件会自动完成逻辑编译、综合、打包、布局布线、仿真逻辑映射(XDC)等工作[8],通过核心板上的FLASH芯片,上电后将程序加载至FPGA芯片中,实现预设的硬件功能。其软件设计流程详见图5。

程序开始运行后,FPGA首先加载FLASH中初始化数据流origin.bin中的XDC配置项完成初始化管脚配置,通过CLB中多个LUT集成PLL功能将外部输入的50MHz时钟倍频至1GHz,提供给FPGA芯片作为运行所需的系统时钟。之后等待Transceiver收发器接收上位机发来的UART数据,成功接收报文并解析后,明确当前的测试场景及应用。随后通过QPSI接口从FLASH的16个缓存区内找到对应当前测试需求的最终数据流bin文件后重新加载,依据最终程序的配置和响应,调用BANK13~16的多个CLB单元,通过LUT查找表配合具有嵌套关系的MUX复用器及最高可达1GHz的高级定时器,产生满足逻辑要求的+3.3V CMOS类型通用I/O接口输出,最后对FPGA后端外围电路的EN使能端、DIR方向端、DAC芯片的14位数据进行发送和控制,最终得到在当前测试应用下所需的专用信号。

2.2.2 通用测试平台上位机软件

通用测试平台上位机软件采用Qt开发平台,通过SCPI命令及VISA I/O库实现对仪表程控设置。自动测试软件支持WINDOWS、银河麒麟等多个操作系统,能够实现跨平台运行。

2.2.2.1上位机软件组成

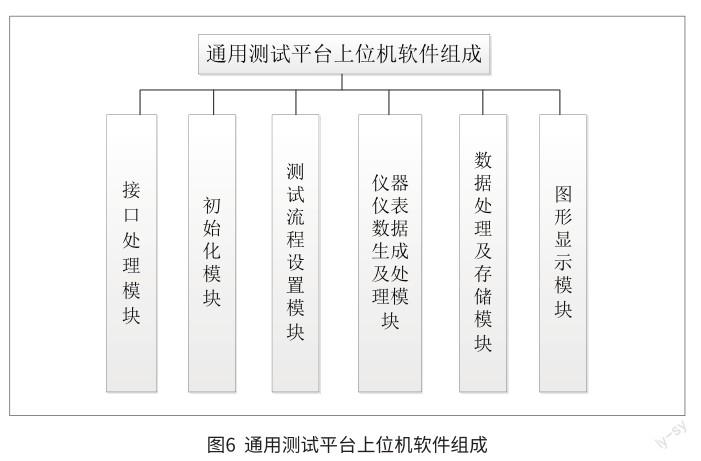

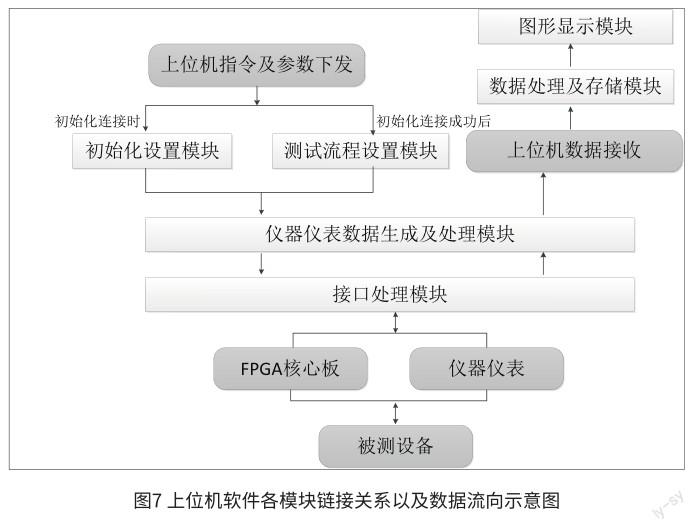

根据实现功能不同,将上位机软件进行模块化划分,如图6所示,通用测试平台上位机软件由接口模块、初始化模块、测试流程设置模块、仪器仪表数据生成及处理模块、数据处理及存储模块、图形显示模块组成。

接口处理模块:实现上位机与FPGA核心板、上位机与仪器仪表程控接口的通信控制,对FPGA核心板以及仪器仪表链接状态进行实时监测;

初始化模块:实现上位机系统内存初始化、各变量初值初始化、接口初始化以及仪器仪表默认参数初始化设置;

测试流程设置模块:实现用户对被测设备测试项目、测试模式、测试流程以及测试数据存储和显示的设计;

仪器仪表数据生成及处理模块:根据相应的测试设置对所选的仪器仪表生成相应的SCPI命令,对仪器仪表所回传的标准数据进行处理形成用户所需的测试数据;

数据处理及存储模块:根据用户的设置对测试数据结果进行筛选、划区等处理并存储;

图形显示模块:对存储的最终测试数据以图形、图像或图表形式进行可视化显示。

2.2.2.2上位机软件工作流程

通用自动测试平台上位机软件各模块连接关系以及数据流向示意图如图7所示。

上位机软件工作基本流程如下:

a)发送FPGA核心板、被测设备、仪器仪表建立连接命令,与FPGA核心板、被测设备、仪器仪表建立连接;

b)发送FPGA核心板、被测设备、仪器仪表初始化命令,初始化FPGA核心板、被测设备、仪器仪表;

c)发送FPGA核心板、被测设备、仪器仪表参数设置命令,观察反馈信息。若反馈信息正确,则表示连接成功,反之,连接失败。检查FPGA核心板、被测设备、仪器仪表状态,若状态正常,则返回上一步,否则,人工修正连接;完成FPGA核心板、被测设备、仪器仪表相关参数设置;

d)FPGA核心板、被测设备、仪器仪表连接成功后,选择相应测试项目;

e)根据测试需求,设置测试模式(包括单步测试、轮循测试、交检测试等);

f)下发相应测试模式下仪器仪表、FPGA核心板参数设置,设置成功后,需将设置参数反馈至上位机,等待测试人员确认;

g)各项准备工作完成后,点击开始测试。等待被测设备相关性能基本稳定并达到可测状态、仪器仪表测试结果稳定后,上位机读取仪表测量结果并在软件系统界面可视化刷新显示,判断后续是否有未测试项目,直至所有测试项目测量完毕,将测试数据根据用户选择以.Txt、.doc、.xsl等格式进行存储。

通用测试平台上位机软件基本工作流程图如图8所示。

3 结语

本文提出并设计了一种基于FPGA的通用自动测试平台设计,对电子产品在调试、测试中测试指令的下发和测试数据获取及处理实现了全自动化控制。基于FPGA的通用自动测试平台设计,总体外观结构为一台便携式加固计算机,内部设计一块FPGA核心板,对外接口采用统一的模块化设计,通过SCPI命令及VISA I/O库实现对仪表程控设置,通过上位机平台实现系统的参数设置、测试流程编辑以及数据的自动捕获、处理和可视化显示。

参考文献

[1]田晚成,基于FPGA和LabVIEW的某产品自动测试系统设计与实现[D].成都:电子科技大学,2019.

[2]尚建波,展利,一种射频滤波组件自动测试系统的设计与实现[J],电子质量,2019(3),61-64.

[3]张翔,基于GPIB的数字电路自动测试系统设计分析[J],电子设计工程,2019,27(16),88-91.

[4]王华,基于ATE的FPGA测试技术研究和应用[J],电子与封装,2018,18(7),12-15.

[5]雷爱强,某系列雷达自动测试系统研制[D].哈尔滨:哈尔滨工业大学,2014

[6]董志玉,發射接收模块自动测试系统软件模块机流程设计[D].成都:电子科技大学,2017

[7]许丽君,一种PCB板测试系统的设计与实现[D].成都:电子科技大学,2018

[8]李雪莹,FPGA软件自动化测试平台的设计与实现[D].上海:东华大学,2018

(作者简介:马绪铎,硕士,工程师,主要研究为雷达系统信号处理及数字电路设计。工作单位:西安导航技术研究所)