100BASE-FX物理层收发器设计与仿真

2023-05-26高金辉汪再兴郑丽君刘晓忠

高金辉, 汪再兴, 郑丽君, 刘晓忠

(兰州交通大学 电子与信息工程学院, 兰州 730070)

光通信技术因具有稳定性强与速度快等特点被广泛应用于各领域之中,且以太网也将光传输作为重要发展方向之一[1-2].100 Mbit/s光以太网作为我国覆盖最广的线路之一,研究其PHY层(physical layer,物理层)的设计规则及实现方式,能为进一步升级以太网传输速度提供技术保障[3].而对物理层的深入研究,了解其传输数据的速度、位宽与频率等条件,可为接口处协议设计提供便利,进一步提高传输效率,以此获得更优的用户体验[4-6].以太网标准IEEE802.3规范由IEEE组织制定,其不仅为设计生产PHY芯片提供了规范,还便于研究者利用统一的标准进行产品开发[7].

100BASE-FX(100 Mbit/s光纤基带以太网)从20世纪90年代开始被广泛应用,近年来我国也大量展开100 Mbit/s光以太网的研究.任靖晔[8]提出了一种基于FPGA芯片的100 Mbit/s、1 000 Mbit/s以太网自适应技术.2021年,冯梓轩等[9]研究了乘用车千兆以太网物理层技术.PHY层作为以太网面向用户的第一层,对其进行研究是探究以太网传输规则及开发终端设备的首要任务.

100BASE-FX以太网的PHY层可支持全双工以太网MAC(media access control,控制器)层,且提供并行4B/5B编码、NRZI(no return zero-inverse,不归零反相)编码、数据的纠错及等待功能.上一代10BASE-TX(10 Mbit/s光纤基带以太网)的PHY层使用了曼彻斯特编码模块,无并行编码模块,数据串行输出.100BASE-FX相较于上一代10BASE-TX串行的编码方式提供了更高的传输效率,在同一时钟频率下,并行编码可提供数倍于串行编码的数据传输速度.

本文主要聚焦于PHY层的PCS、PMA子层,完成收发器的设计仿真.本设计自上而下设计PHY的顶层功能,设计PCS、PMA两个子层的功能模块.实现方式则是由下至上,实现4B/5B和NRZI编码与解码、串并转换与并串转换等底层模块后,通过时钟匹配与握手协议将各模块相连接,实现PCS、PMA两个子层的功能,完成整体设计.

1 PHY整体结构

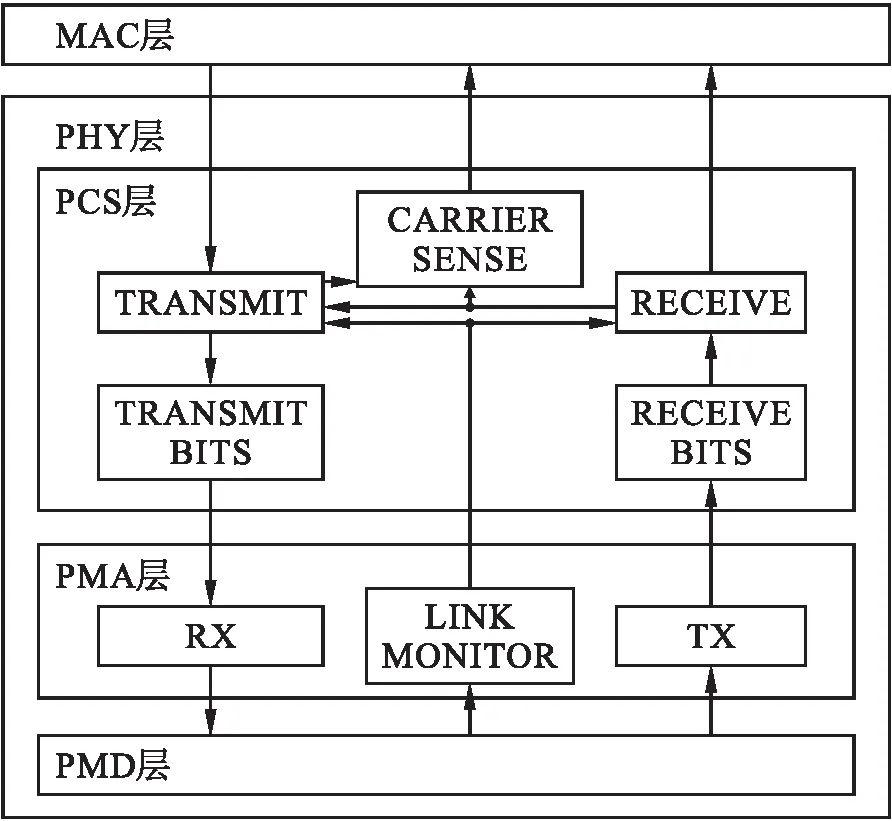

PHY层位于OSI(open system interconnection,开放系统互连模型)七层协议中数据链路层的第一层,其负责联通MAC层与终端,保证二者间的数据转换可正常进行,且规范物理介质参数并支持100 Mbit/s的数据率[10].PHY层结构示意图如图1所示.PCS子层与PMA子层共同实现数据的收发,其中PCS子层在接收链路中将4B/5B解码后的数据送向MAC层,且在发送链路中将MAC层接收的数据进行4B/5B编码;而在链路监听功能中,其负责产生载波状态信号并将该信号送向MAC层[11].PMA层则在接收链路中将从终端接收的数据进行NRZI解码;在发送链路中,将数据完成NRZI编码后再送向MAC层[12].

图1 PHY层结构示意图

1.1 PCS子层

PCS子层负责PHY层与MAC层的数据交换及链路的监控,主要提供4B/5B编码功能[13].服务接口为100 Mbit/s MII(medium independent interface,独立介质接口),所以要求PCS子层的传输上限至少为100 Mbit/s.

4B/5B编码方式由IEEE 802.3协议定义,具有效率高、易实现等优点.在连续传送时,传输过程中任何一对5 bit代码连续的0最多仅有3个,较好地解决了数据中出现连续0的问题,并有助于降低传输错误率,方便从数据中恢复时钟.

1.2 PMA子层

PMA子层负责与PCS层、PMA层进行数据交流和生成使能信号,提供NRZI编码功能.由于PCS层输出速度与接收不同,所以需在PMA层重新匹配时钟.例如,PCS层使用25 MHz时钟,则PMA层的时钟频率需达到125 MHz.NRZI的编码规则为当前信号跳变为0,输出为1[14].此种方法将信号与时钟相结合,解决了数据中因连续出现1而导致的容易出错及时钟无法恢复的问题.此外NRZI编码方式还节约了带宽,提高了传输效率.

2 分层设计

2.1 顶层设计

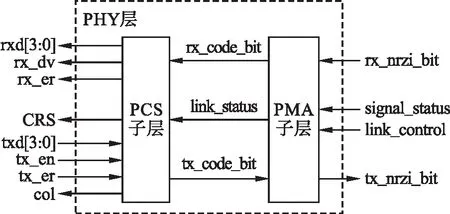

PHY顶层设计如图2所示.其中,PCS子层受link_status(链路状态信号)控制,负责对txd(PCS发送数据)进行4B/5B编码和并串转换,或对rx_code_bit(串行接收数据)进行串并转换后4B/5B解码.PMA子层负责提供使能信号以及NRZI编解码功能.

图2 PHY顶层模块设计

PHY顶层通过联通所有的子层模块从而完成整体设计,但需考虑两点:

1) 各模块的信号联通.将各模块相对应的输入输出信号连接,以保证逻辑正确,实现发送、接收链路及链路反馈等功能.例如,PMA子层LINK MONITOR(链路监控模块)所产生的链路状态控制信号需分别提供给PCS子层的TRANSMIT(发送模块)与RECEIVE(接收模块),进而控制接收与发送链路的工作进程.

2) 提供时钟.考虑到不同模块的时钟匹配,根据不同模块的需求,提供对应的时钟频率.例如,TRANSMIT与RECEIVE模块所需的时钟频率为25 MHz,方能达到要求的传输速率.而TRANSMIT BITS(串行发送模块)与RECEIVE BITS(串行接收模块)模块为了与其匹配,则需要提供频率为125 MHz的时钟.

2.2 PCS子层设计

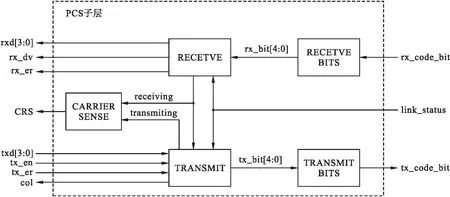

PCS子层模块结构如图3所示,共设计了5个模块,分别是:TRANSMIT、TRANSMIT BITS、RECEIVE、RECEIVE BITS和CARRIER SENSE(载波监听模块).

图3 PCS层模块图

其中,CARRIER SENSE负责产生CRS(载波状态信号)并送向MAC层.此外,当该模块在检测到发送链路与接收链路均处于工作状态或任意一个在工作状态时,会判断CRS有效并向MAC层发送;而当两链路均未工作时,则将CRS信号视为无效.

RECEIVE负责将来自于RECEIVE BITS模块的rx_bit(并行接收数据)解码成rxd(PCS接收数据),并生成用于链路监控的标志信号,收发速度可达100 Mbit/s.该模块在检测到link_status信号有效后开始工作,当识别出数据流中的SSD(start stream data,启动流数据),则开始4B/5B解码工作.之后可能存在4种工作状态:若在SSD后为DATA(有效码型),则正常解码,并将解码后的4位宽数据送向MAC层;若检测到ESD(end stream data,终止流数据),则解码结束,输出IDLE(空闲码型)占位并回到空闲状态;若连续检测到5个高电平,即空闲码型,则解码过早结束,此时将rx_er(接收错误信号)设置为有效,结束解码并回到空闲状态;而若解码行为开始后所读取的数据并非上述任意一种信号,则数据错误,将rx_er设置为有效,之后回到数据检测,并识别下一组数据.

RECEIVE BITS负责将来自于PMA层的串行rx_code_bit转换为并行的rx_bit.为了与RECEIVE模块接收速度匹配,RECEIVE BITS模块数据接收频率5倍于发送频率.RECEIVE BITS模块在检测到rx_code_bit信号中的SSD指令后,开始工作,将SSD指令后的有效数据进行串并转换.当识别出rx_code_bit信号中的ESD指令时,发送指令,转为检查SSD状态.

TRANSMIT负责将来自于MAC层的txd进行4B/5B编码,生成标志信号,并控制col(链路冲突信号)的产生,收发速度可达100 Mbit/s.空闲时会持续发送IDLE数据,当tx_en(发送使能信号)有效后,开始4B/5B编码工作.之后可能有3种工作状态:若接收SSD的同时,tx_er(发送错误信号)有效,则进入错误翻译路径,正常发送两个SSD信号后发送HALT(数据错误码型),等待tx_er无效,此时col信号取决于接收链路;若tx_er无效且接收到有效数据,则正常编码,此时col信号同样取决于接收链路;若检测到ESD指令,则解码结束,输出两个ESD指令后,回到空闲模块等待,此时col信号无效.

TRANSMIT BITS负责将已经4B/5B转码后的并行tx_bit(并行发送数据)转换为串行tx_code_bit(串行发送数据).为了与接收速度相匹配,数据发送频率5倍于接收频率.该模块对每一个完整的tx_bit进行并串转换,包括SSD、DATA、ESD、IDLE和HALT.

PCS子层设计满足了100BASE-FX以太网的物理层要求.为了实现时钟恢复功能,采用了4B/5B编码方式,此种方式具有16个有效数据组,可保证数据中拥有足够多的跳变,从而便于从串行数据中恢复时钟.同时,4B/5B编码方式可在同样的25 MHz时钟频率下及100 Mbit/s的100BASE-FX上获得125 Mbit/s的带宽,满足了MAC层100 Mbit/s的传输速度.

2.3 PMA子层设计

PMA子层负责将PCS子层数据进行编码发送、将终端数据解码传回以及对链路状态进行控制.PMA子层模块结构共设计了3个模块,分别是:LINK MONITOR、TX(NRZI编码模块)和RX(NRZI解码模块),如图1所示.

TX负责将并串转换后的tx_code_bit进行NRZI编码,以便被PMD层识别.该模块对每一个接收到的数据均会进行NRZI编码.

RX负责将从物理终端接收的tx_nrzi_bit进行NRZI解码,再送向PCS子层.RX模块对每一个接收到的数据进行NRZI解码,但并不负责检测数据是否为有效数据.

LINK MONITOR负责对链路控制信号进行监视,以生成正确的控制信号,并用来控制PCS子层的TRANSMIT与RECEIVE模块正常工作.当signal_status(数据状态信号)有效时,启动计时器.若在计时器周期内该信号均是有效的,则等待link_control(链路控制信号)状态,若为有效,则再将link_status信号送出.

3 仿真结果

本文的物理层设计仿真环境:Intel Core i5-7200U处理器,Microsoft Windows10 Profession操作系统,并使用ModelSim SE 10.5(64 bit)进行测试.

3.1 顶层模块测试

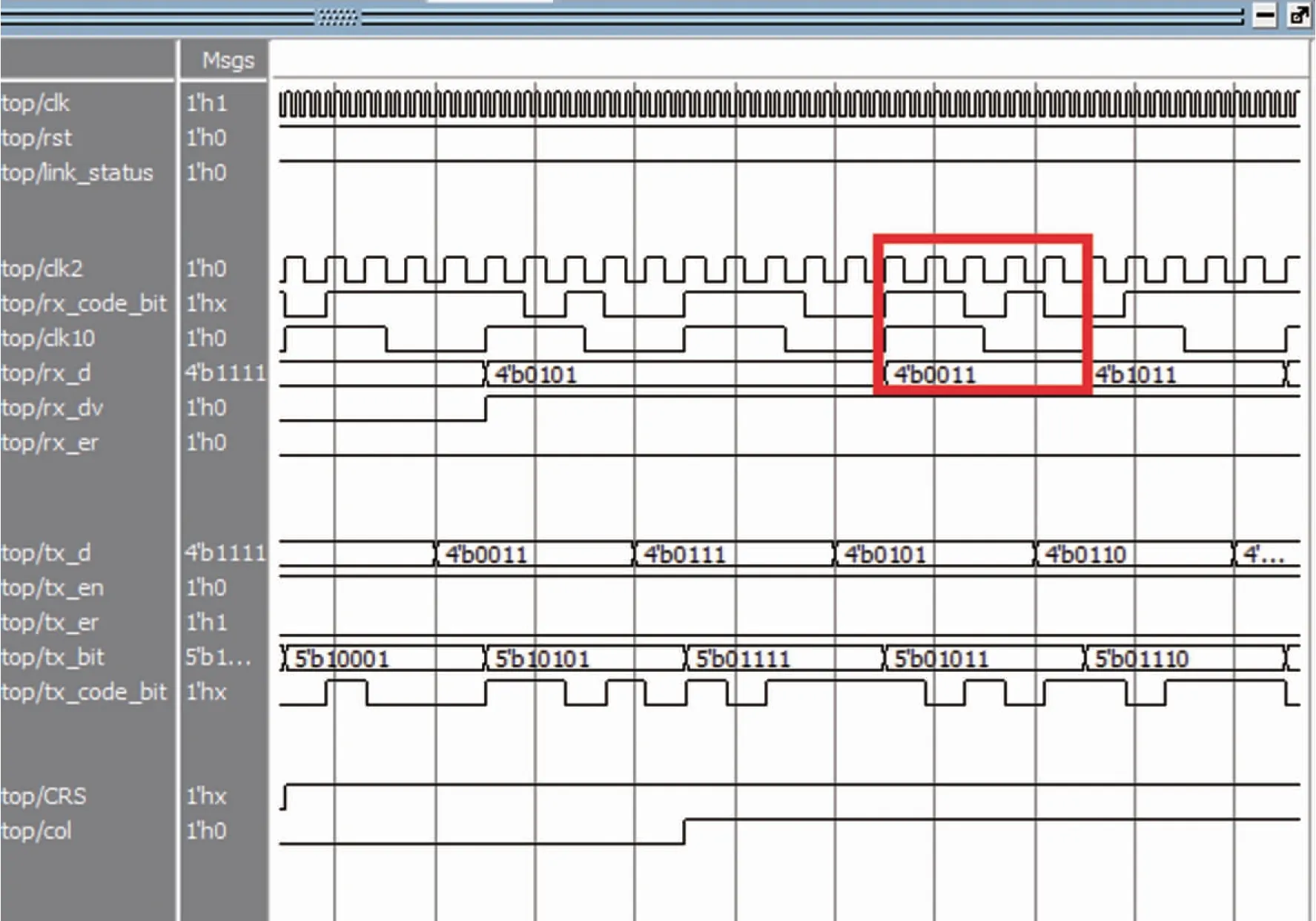

顶层模块仿真结果如图4所示.10BASE-TX的物理层将终端信号NRZI解码后送出,数据输出效率十分依赖时钟,而100BASE-FX在PCS子层采用了4B/5B编码,使输出信号并行输出,较大程度上提高传输效率.

图4 顶层模块部分信号仿真图

10BASE-TX仅对输出信号做了NRZI解码,输出速率相当于PCS子层的rx_code_bit,在图4中对应的时钟为clk2,频率为125 MHz;100BASE-FX的输出为rx_d,对应的时钟为clk10,频率为25 MHz.如图4红框内所示,rx_code_bit在5个时钟周期内共发送5位数据,实现了125 Mbit/s的传输速度,而rx_d在1个周期内输出4位宽数据,且信息量相当于4位rx_code_bit,收发器在25 MHz时钟下实现了100 Mbit/s的收发.

3.2 PCS子层测试

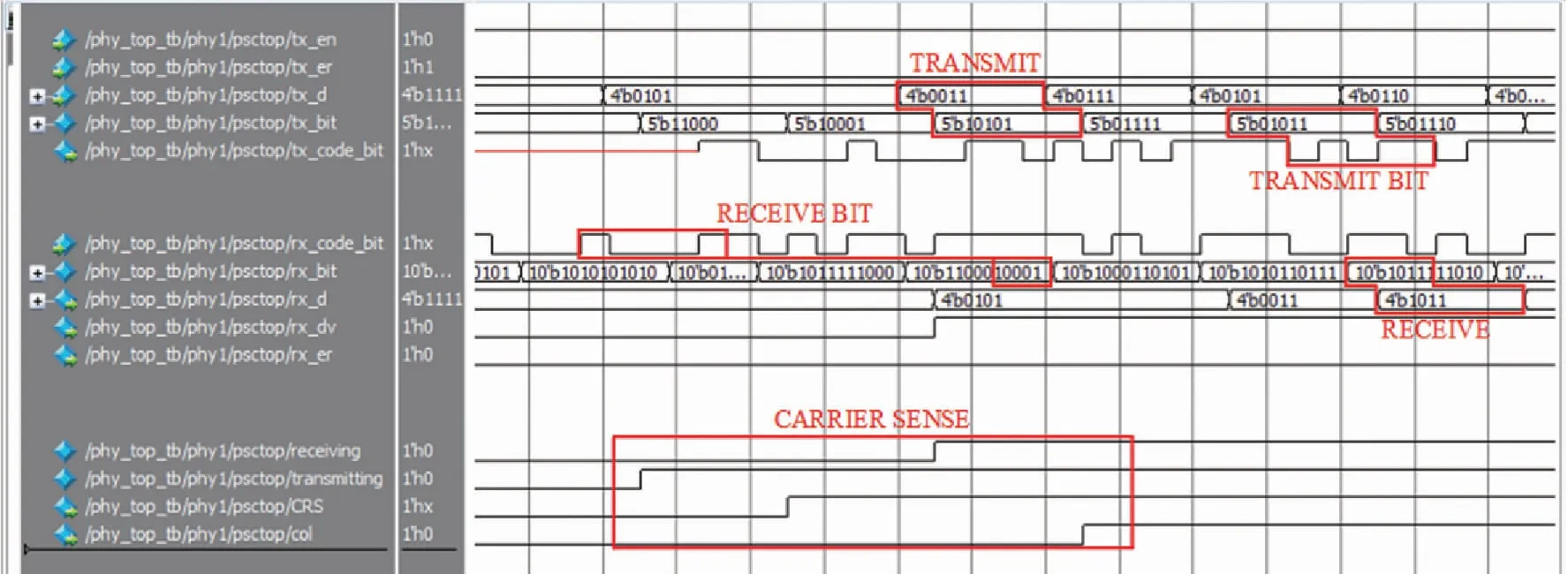

PCS主要完成发送链路的4B/5B解码与并串转换工作,接收链路的串并转换、4B/5B编码及载波监控整体仿真如图5所示.

图5 PCS层仿真图

发送链路中,TRANSMIT与TRANSMIT BIT两模块工作正常,获得有效数据后,均在下一时钟上升沿开始翻译,且码型正确.对于无法识别的数据不会中断该发送过程,而是输出翻译错误数据来占位,以确保用户可识别出错误数据组,便于在对应位置检查,同时也保证其他数据的传输不受影响.所设计的发送链路在保证传输的同时对错误帧位置发出提示,鲁棒性较强.

接收链路中RECEIVE BIT与RECEIVE两模块工作正常,RECEIVE BIT模块中输出信号与输入信号对应数据延时较大,因rx_bit[9∶0]为10位宽信号,所以读取后输出信号延迟11个时钟周期;RECEIVE模块则在接收到数据后的下一个时钟沿输出对应数据.当接收链路检测出接收数据中存在无效信号时,将rx_er设置为有效,并跳过解码该数据.这样可有效标记出数据错误位置,同时不影响其他数据传输.在接下来的层级处理数据时,可根据rx_er的位置来判断数据是否有效,提高了系统的检错能力.

CARRIER SENSE模块在receiving、transmitting信号同时无效时,CRS信号无效,否则有效.当transmitting信号为高电平而receiving信号为低电平时,CRS信号仍有效.而二者均为低电平时,CRS信号有效,载波监控功能正确.本模块向上层提供链路工作情况,并指示上层控制信号的产生,例如在链路空闲时提示可进行数据传送等.

3.3 PMA子层测试

PMA子层进行链路控制、NRZI编码及解码工作的仿真结果如图6所示.LINK MONITOR模块负责生成链路工作信号,通过监控终端工作状态,决定PCS子层的发送、接收进程是否能够进行.

图6 PMA子层仿真图

TX模块负责将tx_code_bit翻译为NRZI码型的tx_nrzi_bit信号.NRZI编码方式为电平翻转代表逻辑0,电平不变则代表逻辑1.图6中,tx_code_bit信号100011被翻译成01101数据流,逻辑正确,NRZI编码功能实现.

RX负责将接收到的NRZI码型的rx_nrzi_bit数据翻译为rx_code_bit信号.图6中,100001数据流被翻译成rx_code_bit信号101011,逻辑正确,NRZI解码功能成功实现.

4 结 论

本文介绍了100BASE-FX的PHY层结构,着重陈述了PCS子层与PMA子层的信号传递方式,且利用4B/5B编码、NRZI编码和串并转换等技术代替了10BASE-TX物理层中的曼彻斯特编码,完成了对100BASE-FX的PHY层结构及功能的设计,大幅提升了传输效率.在ModelSim软件上进行了验证,获得了正确的仿真结果.在25 MHz时钟下,实现了最高100 Mbit/s的数据交换速度,满足IEEE802.3规范.本文所设计的PHY层结构在实现了更快传输速度的同时,还可适配市场上所有满足IEEE802.3规范的PHY芯片.