低压差线性稳压器在射频中的应用

2023-05-05王燕

王燕

(西南电子设备研究所 四川省成都市 610036)

电源管理是电子系统中的核心模块,在目前电子系统低功耗、高集成度、智能化、可重构的要求下,对电源管理提出了高效率、低噪声、低纹波等要求。主流的电源管理有开关稳压器(DC-DC)、低压差线性稳压器(LDO)。

开关稳压器需要电感和电容等外部元件配合才能在很宽的电压范围内工作,因此布局受限,瞬态响应慢,存在潜在的噪声干扰。LDO 具有外围电路简单、瞬态响应快、不引入额外噪声等优点,广泛应用于各类电子设备中。得益于半导体技术进步,在LDO 的导通回路中采用低导通阻抗RDS(ON)的功率MOSFET 可以进一步提高LDO 的效率[1]。在电源噪声方面,LDO 能够衰减开关稳压器生成的电压纹波。当涉及给频率合成器、调制器、高分辨率数模转换器等对噪声敏感的器件供电时,LDO 是首选。

然而,某些应用中电源纹波抑制已经达到传统低噪声LDO 的极限。例如,在某些高端压控振荡器(VCO)的供电中,电源噪声直接影响VCO 的输出相位噪声。此外,为满足整体系统效率的要求,LDO 通常用于对噪声相对较高的开关转换器的输出进行后级调节。因此合理的使用LDO 降低电源噪声变得至关重要。

1 LDO降低电源噪声的方法

1.1 选取合适的PSRR降低电源噪声

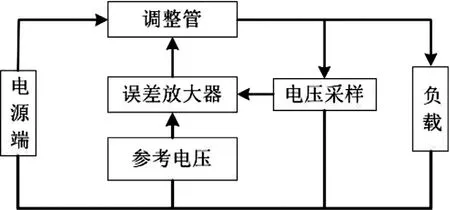

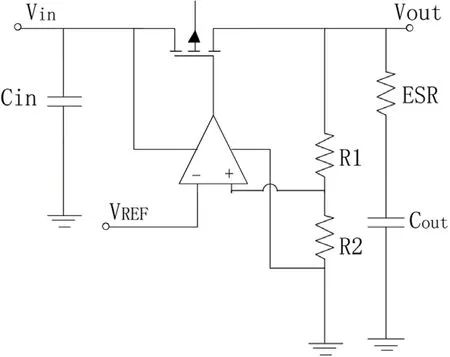

LDO 原理框图如图1所示。当负载发生变化时会引起电压波动,误差放大器将采样的电压波动放大之后作用到调整管以保持负载电压的恒定输出。

图1:LDO 原理图

LDO 的优势之一是能够衰减开关稳压器生成的电压纹波进而降低电源噪声。电源抑制比(PSRR)表示特定频率的交流元件从 LDO 输入衰减到输出的程度,其表达式为式(1):

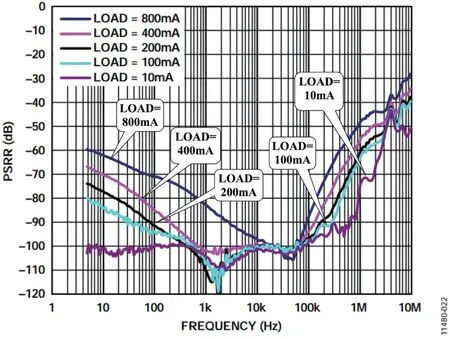

LDO 的PSRR 与频率并非线性关系,以常用高PSRR 的LDO 器件ADM7151[2]为例,图2 为该器件PSRR 与频率的关系。

图2:ADM7151 的PSRR 与频率的关系

由图可得在1 kHz~100 kHz 频段内的PSRR 优于90 dBc,而在其它频段PSRR 恶化严重。因此,当选用LDO 时,应当着重考虑噪声所在频段的PSRR。

1.2 选取低噪声LDO与使用降噪电容器降低电源噪声

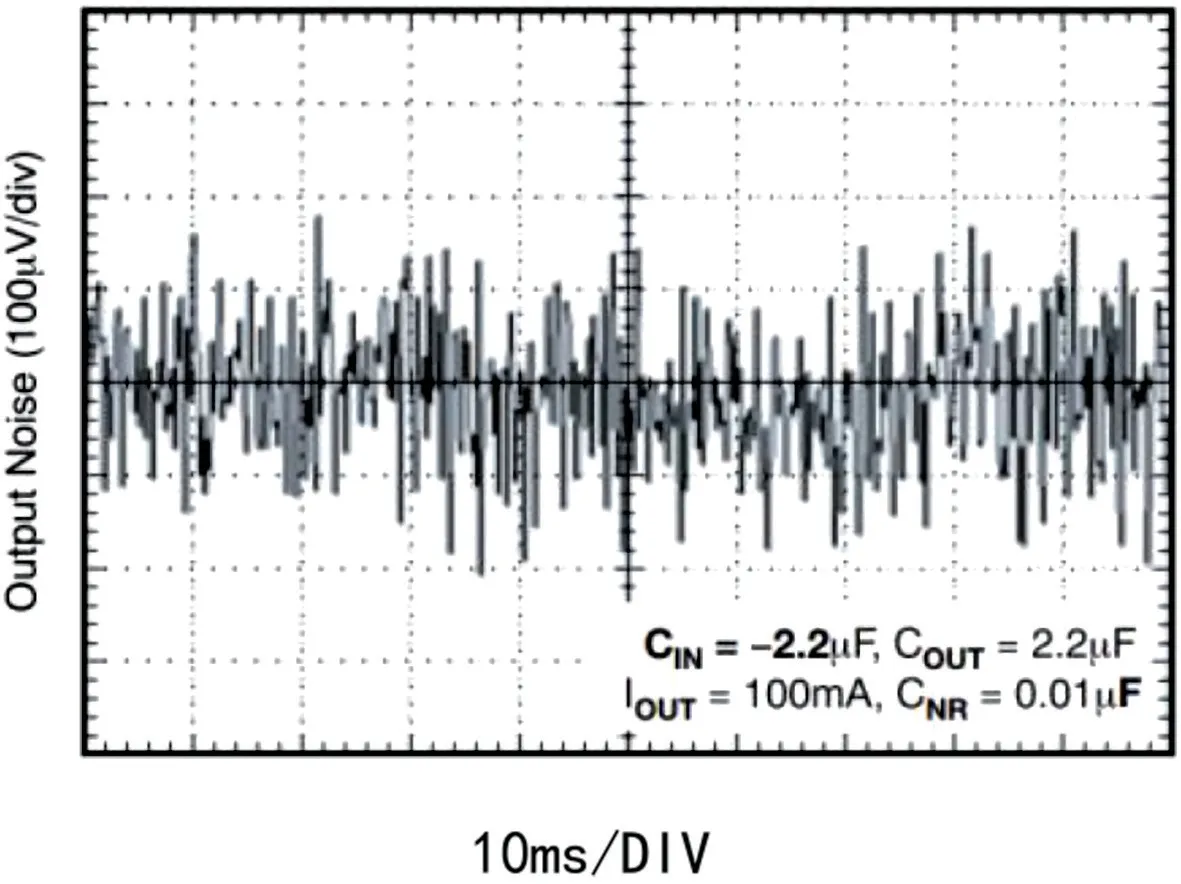

要获得干净的直流电源,仅关注PSRR,而忽略LDO 输出的噪声是不可取的。LDO 作为电子器件,在抑制外部噪声的同时内部同样会产生噪声。选择低噪声LDO 并采取措施降低内部噪声是不可或缺的环节。LDO 自身噪声来源:内部的晶体管、电阻,外部的元器件等。LDO 自身的噪声种类包括:热噪声、散粒噪声和闪烁噪声等。如图3所示为LDO 自身噪声在时域中的表现,热噪声和散粒噪声都是随机的,不随频率而变化;而闪烁噪声源自半导体的表面缺陷,跟频率呈反比特性。

图3:LDO 自身噪声在时域中的表现

在时域中分析噪声十分困难,通常情况可通过两种主要方法来分析噪声:频域分析噪声和以积分值形式分析噪声。LDO 产品的数据资料中通常会提供积分噪声值和噪声功率谱密度,积分噪声值通常为10 Hz~100 kHz范围,以微伏均方根值(μVRMS)表示。噪声功率谱密度通常提供曲线,通过对比积分噪声值和噪声功率谱密度曲线才能更加准确地进行LDO 器材选型。

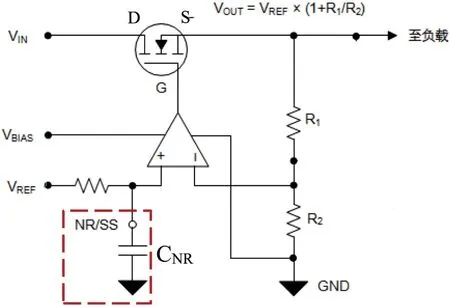

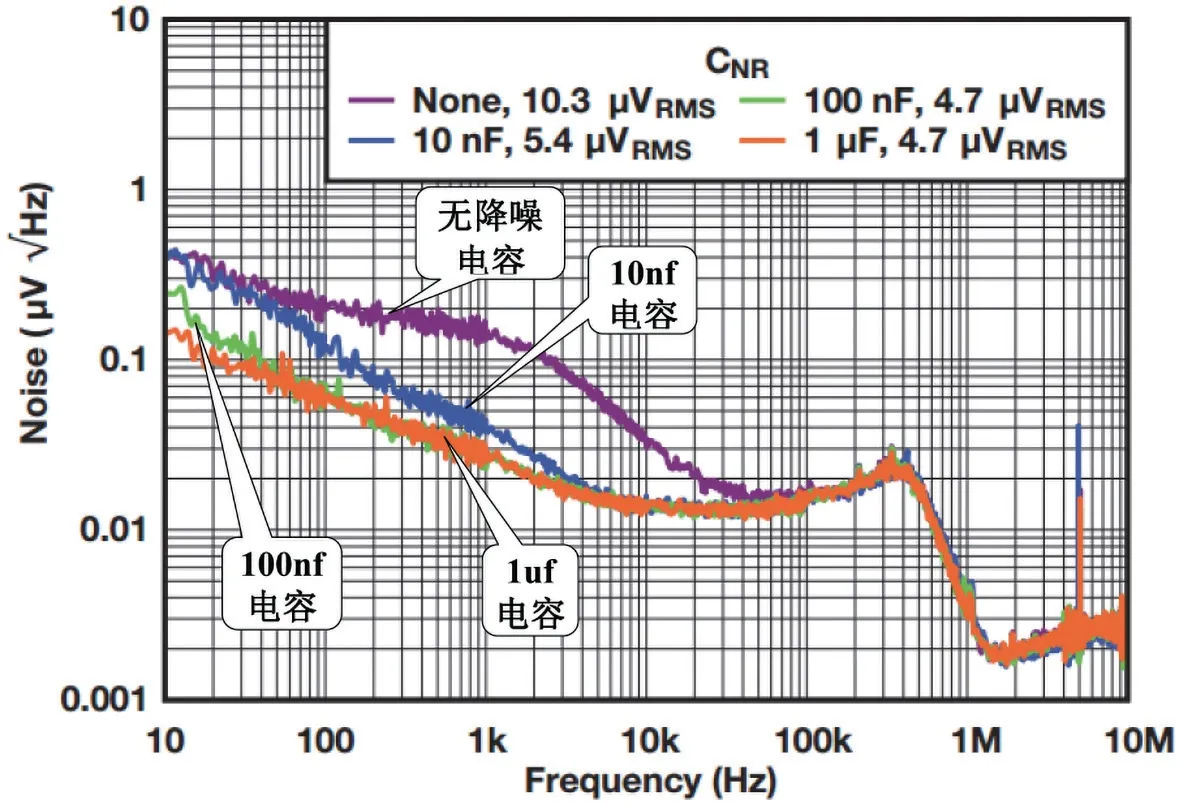

当选择具有低噪声特性的LDO 之后,使用降噪电容器能进一步降低电源噪声。降噪电容器CNR处于图4中的虚线处。

图4:具有降噪引脚NMOS 型LDO

添加降噪电容器CNR将与内部电阻形成RC 滤波器,降低由电压基准VREF生成的噪声。图5 显示了不同容值降噪电容器CNR对输出噪声产生的影响。

由图5 可知采用降噪电容器可以显著地降低电源噪声。此外,降噪电容器还会在启动期间引入 RC 延迟,导致输出电压以较慢的速率斜升。当输出端或负载上存在大容量电容,需要减小浪涌电流时,添加降噪电容器就能有效地提高输出电压转化率,防止浪涌电流出现尖峰,进一步降低电源噪声。

图5:不同CNR 噪声频谱密度与频率的关系

1.3 使用前置电容器(CFF)降低电源噪声

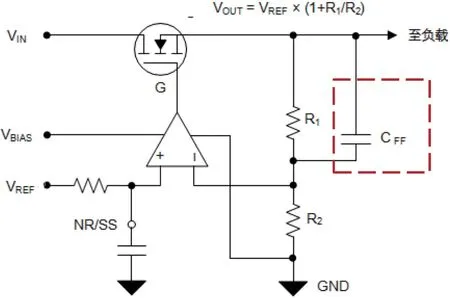

如图6所示,前置电容器是与电阻分压器的电阻R1 并联放置的可选电容器CFF。

图6:使用前置电容器的NMOS 型LDO

在稳压过程中,LDO 的误差放大器驱动FET 的栅极。基准电压将按1+(R1/R2)的比例放大,同时基准电压的噪声部分也会被放大。

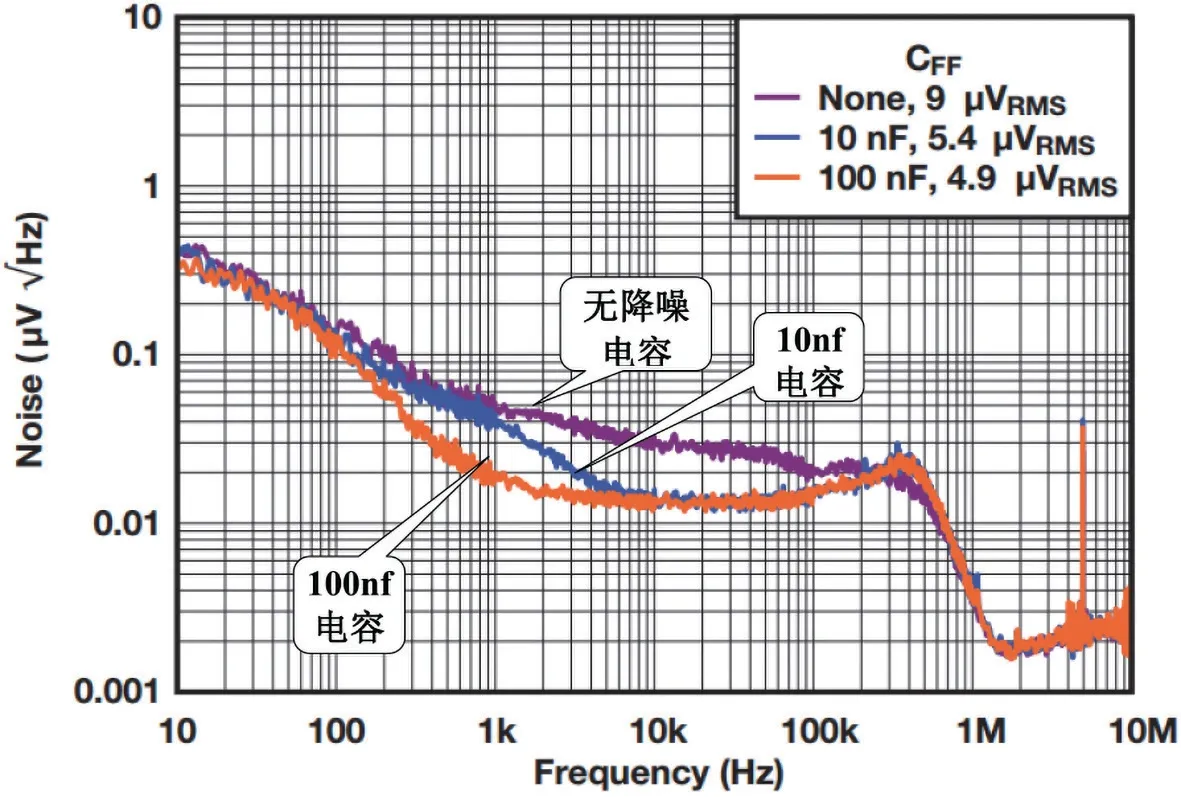

通过与顶部电阻R1 并联放置电容器,将在特定频率范围引入降噪功能,即电阻R1被短路,该频率范围内的噪声部分保持在单位增益范围内。使用不同CFF值的噪声曲线如图7所示[3]。

图7:噪声与频率和CFF 值的关系

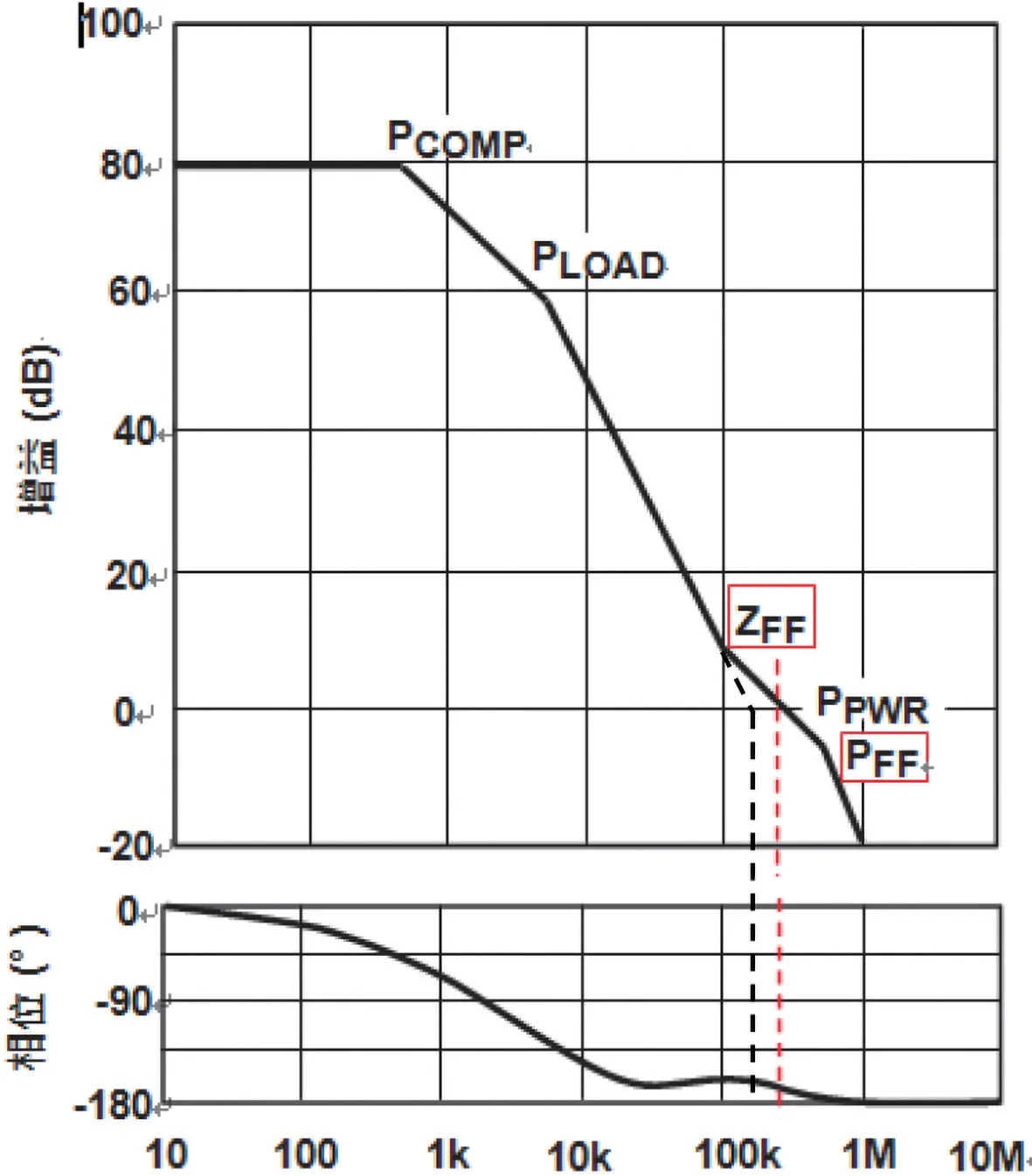

使用前置电容器能够改善稳定性[4],添加CFF会在LDO 反馈回路中引入零点(ZFF)和极点(PFF),可分别通过公式(2)和公式(3)进行计算:

将零点置于出现单位增益的频率之前可以提高相位裕度,如图8所示。

图8:使用前置电容补偿的典型LDO 增益/相位图

由图8 可得,没有ZFF时,单位增益将提前在200kHz 左右出现,增加零点后,出现单位增益的频率略微右移(约300kHz),相位裕度也有所提高。通过增加相位裕度,LDO 输出将减少振铃并更快稳定。因此添加前置电容器CFF能够提高电源稳定性、改善噪声性能。

1.4 配置输出电容器降低电源噪声

稳压电路包括LDO 及其外围电路,其中输出电容自身具有等效串联电阻(ESR)特性。稳压电路中输出电容表示为Cout及其等效串联电阻ESR,等效电路如图9所示。输出电容会为整个稳压电路环路引入一个零点。

图9:LDO 稳压电路中输出电容等效图

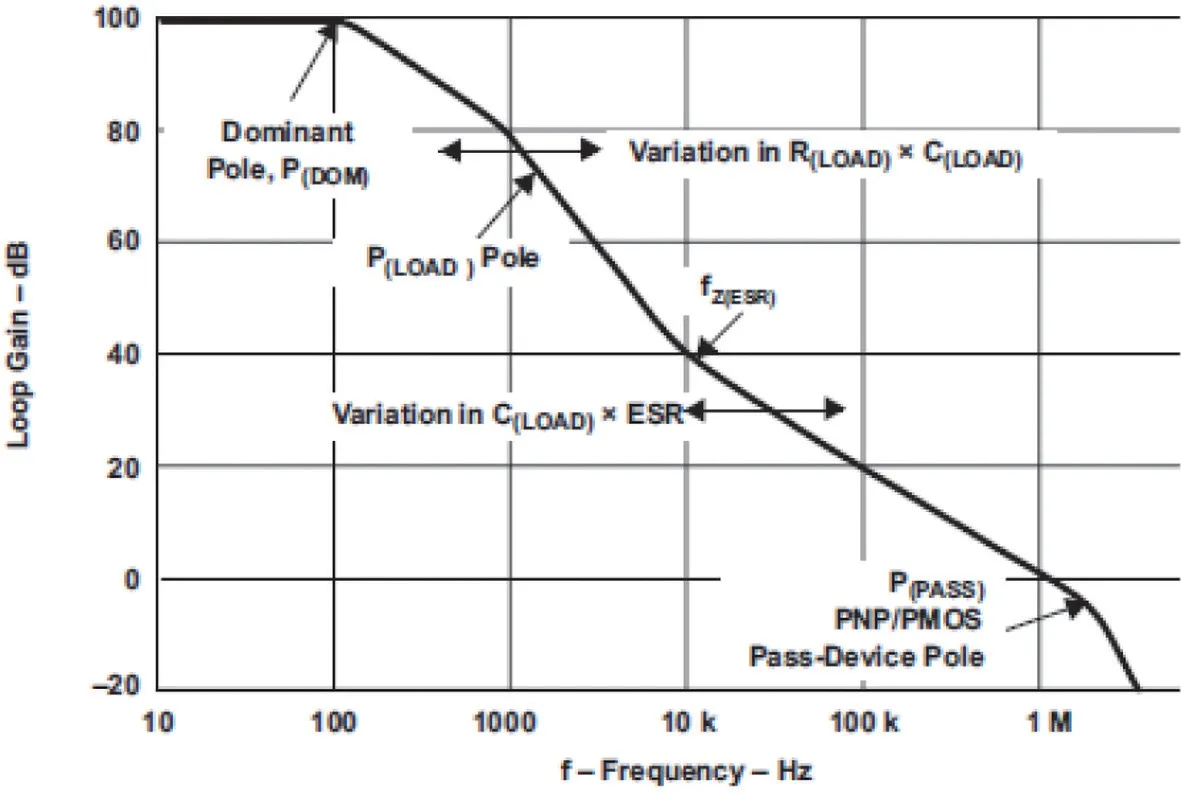

通过计算公式(4),可以求得输出电容引入零点的位置,如图10所示[4]。

图10:输出电容为环路引入零点示意图

输出电容为环路引入零点fZ(ESR)处于环路单位增益带宽以内,就可以对环路形成补偿作用。从而提高相位余度,使得环路保持稳定,降低稳压电路噪声。

2 工程验证

2.1 锁相环电路的电源管理设计

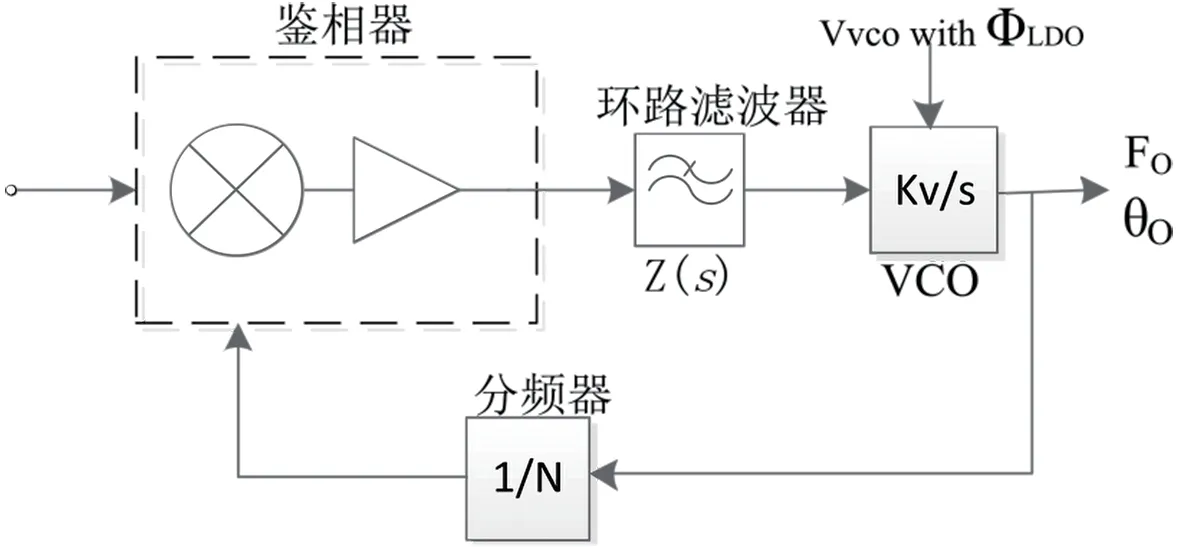

锁相环(PLL)电路对电源的噪声和纹波比较敏感,其工作原理如图11所示,基本元件为鉴相器、环路滤波器、VCO 和分频器。

图11:锁相环电路原理图

与压控振荡器噪声类似, LDO 的相位噪声贡献可以看成加性成分φLDO[5]。在LDO 给压控振荡器提供直流电源时,也将自身的噪声和纹波传输过去。LDO 的电源噪声引起的VCO 相位噪声贡献的公式如式(5):

式中LLDO是频率偏移f时, LDO 对VCO 相位噪声(以dBc/Hz 表示)的噪声贡献;Kpushing是VCO 推压系数,以Hz/V 表示;VLDO是给定频率偏移f下的噪声频谱密度,以V/√Hz 表示。

例如:推压系数为10MHz/V,在100kHz 频率偏移下测得相位噪声为–116 dBc/Hz 的VCO,电源噪声和VCO 噪声作为均方根添加,因此电源噪声应比VCO噪声至少低6dB(相当于两者有效值相差4 倍),以便将噪声贡献降至最低。所以LLDO应小于–122 dBc/Hz。使用公式(5),求解在100 kHz 偏移下,VLDO=11.2 nV/√Hz。通常可通过LDO 数据手册的典型性能曲线对比,可选取100 kHz 偏移下,电源噪声频谱密度优于11.2nV/√Hz 的型号。

2.2 提高LDO环路稳定性,降低噪声

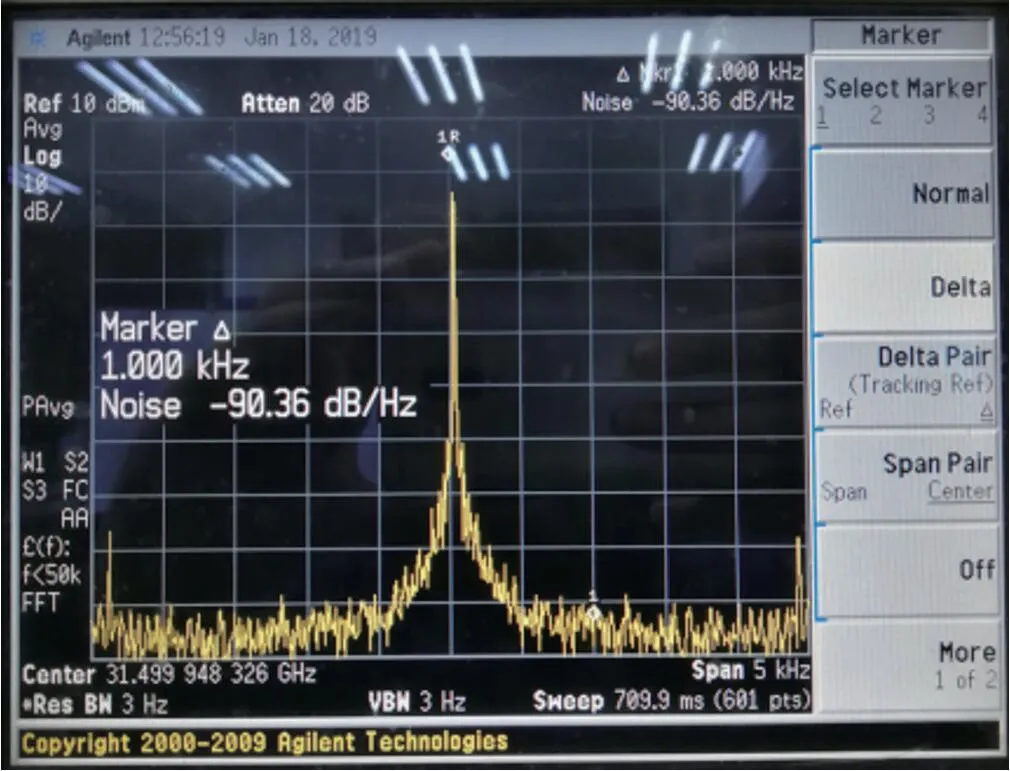

某课题的射频前端组件使用了一款国产LDO,对射频放大器供电。使用信号源和频谱仪对组件进行测试时,在常温状态下射频主信号旁边有多个杂散信号,如图12所示,经过分析,发现稳压电路不稳定。

该LDO 外围电路特别是输出电容决定整个稳压电路能否稳定。在图9 的基础上,输出电容Cout 处再串联一个电阻R3(作用等效于增加输出电容Cout 的ESR),更改后的外围电路如图13所示。当设置R3 为0.3 欧姆时,射频主信号旁边的杂散消除,如图14所示,电源噪声大幅降低。

图14:串联电阻R3 后的频域测试图

3 结束语

本文详细介绍了如何选取合适的PSRR 降低外部电源噪声,并通过使用降噪电容器(CNR)、前置电容器(CFF)、输出电容器(Cout)进一步降低电源噪声,当涉及对噪声敏感的模拟/射频应用,电路设计就需重点考虑上述问题。

案例一介绍了用定量计算的方法来确定所选LDO引入的噪声是否会恶化锁相环VCO 输出信号的相位噪声;案例二介绍了增加串联电阻R3 改进了某款国产低压差线性稳压器不稳定的情况,大幅降低了电源噪声。通过两个案例,验证了上述几种降低电源噪声方法的有效性。