星载遥感高光谱成像仪电子学抗辐照设计

2023-04-03刘永征陈小来张昕孔亮刘学斌石兴春

刘永征 陈小来 张昕 孔亮 刘学斌 石兴春

(中国科学院西安光学精密机械研究所,西安 710119)

随着星载成像遥感不断发展,空间辐照环境引发的星载遥感成像载荷工作失灵事件频现,如工作中突发遥测数据异常、突发数据传输芯片不执行总线指令、突发星务与测控组件总通信错误计数、突发现场可编程门阵列(FPGA)刷新数据错误、突发读取静态随机存取存储器异常、遥测异常的有效载荷管理单元广播频发等[1],因此各遥感卫星总体对载荷系统抗辐照设计的要求更加严格。

星载遥感用高光谱成像仪载荷,多数搭载的卫星平台轨道高度集中在400~900 km范围内[2],空间辐照环境主要是内地球辐射带的影响。典型高通量高光谱成像仪从材料的角度可分为光、机、电三部分。辐照环境对光学材料的影响主要表现为玻璃透过率降低、玻璃变色。空间辐照会使得星载遥感大孔径干涉成像高光谱成像仪的光学元件膜系退化,系统实际信噪比偏离理论设计,进而影响光谱复原精度,从而降低仪器探测识别精度。辐照环境会使电路噪声增大或电参数发生漂移,噪声增大直接影响大孔径干涉高光谱成像仪的干涉图信噪比,最终降低设备的光谱信噪比和弱光谱探测灵敏度;电参数漂移会降低原始图像信噪比,甚至导致成像功能失效。因此,如何实现星载高光谱成像仪的抗辐照设计逐渐成为星载仪器研制亟待解决的重要问题。

本文结合工程实现,对高光谱成像仪电子学中抗辐照设计进行了探索和总结。

1 抗辐照总体设计

基于星载遥感大孔径干涉成像光谱技术(LASIS)的高光谱成像仪,其电荷耦合器件(CCD)成像电路具有面阵大、帧频高、数据量大的特点,对空间辐照环境更为敏感,这就对从电子学角度对高光谱成像仪进行抗辐照设计提出了更高的要求。多年高光谱成像仪载荷的研制经验和测试结果均表明:在光机结构采取抗辐照设计条件下,整个遥感任务期内,高光谱成像仪的光机结构的辐照退化对整体性能影响要远小于电子学部分的衰退影响,故本文重点研究从电子学的角度进行抗辐照设计。

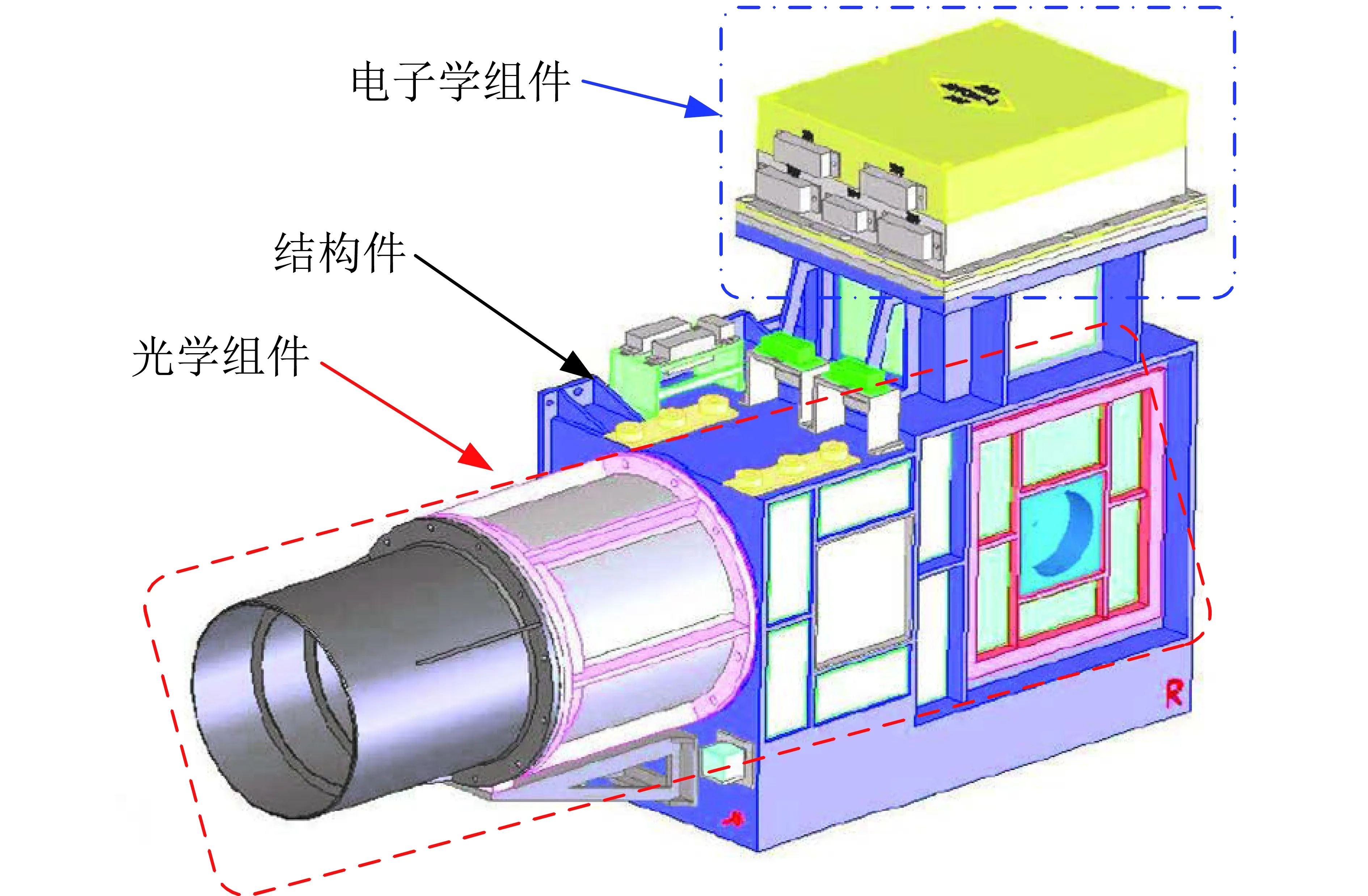

大孔径干涉高光谱成像仪(典型光机电结构如图1所示)从组成上分为光学组件、结构件、电子学组件三部分。光学组件由前置光学系统部件、准直光学系统部件、干涉仪、傅里叶镜构成,用于完成对遥感景象的光学干涉成像;结构件包含支撑各部分光学组件的成像仪主体、放置电子学电路的结构箱体;电子学组件主要包括光电转换电路、模拟信号处理电路、图像数据压缩电路、高速数据传输电路、成像仪控制电路等五大功能部分[3]。

图1 高光谱成像仪光、机、电三部分组成结构Fig.1 Optical,mechanical and electrical constructions of a hyperspectral imager

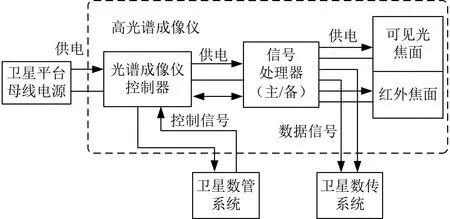

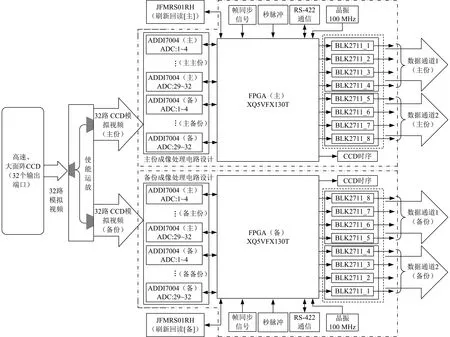

高光谱成像仪电子学的五大功能部分按照结构件独立性可划分为焦面组件(光电转换)、信号处理器电路和光谱成像仪控制器三台单机[4],如图2所示:光谱成像仪控制器用来提供分系统电源、与卫星数管系统通讯及收发整星指令;信号处理器在控制器指令下处理帧频、增益、通信及秒脉冲信号,并向控制器反馈遥测信息,给卫星数传系统发送图像数据;可见光焦面和红外焦面用于完成可见光近红外谱段、短波红外谱段的光电转换,实现从目标光信息到电信号的转换。高光谱成像仪为兼顾高空间分辨率和宽遥感幅面,焦面组件选用背照式大面阵分帧转移高速光电转换器件,有32个并行高速输出端口,每个端口模拟视频像元输出速率高达36 MHz。视频转换采用多片四通道高速模数转换器ADDI7004的大面阵、高帧频高速成像电子学系统实时对32个通道的高速模拟视频信号进行相关双采样及模数转换,实现2048×256像元面阵图像、帧频1500帧/秒的CCD成像指标[5]。

图2 星载高光谱成像仪电子学组成Fig.2 Electronic composition of a spaceborne remote sensing hyperspectral imager

高光谱成像仪受到辐射影响主要是地球内辐射带的质子、电子和重离子所产生的总剂量辐照效应和单粒子效应[6]。

影响星载高光谱成像仪的总剂量效应是因空间的带电粒子在电路的半导体器件内产生电子空穴对,从而引起电参数漂移,进而引发器件功能失效,导致成像电路工作异常;入射粒子与电路中半导体器件中的晶格原子发生碰撞,造成位移损伤,导致器件永久性失效[7]。在国际通用单位制中,用拉德(rad)和戈瑞(Gy)表示辐射剂量的大小,1 Gy=100 rad[8]。

单粒子效应主要影响到高光谱成像仪电路中的静态随机存取存储器(SRAM)、可编程只读存储器(PROM)、FPGA、数据总线等集成电路以及模数转换器(ADC)、直流转直流电源(DC/DC)、功率金属氧化物半导体(MOS)管、运放等模拟和数模混合电路。

高光谱成像仪抗辐照总体设计原则:综合使用金属结构材料优化屏蔽、电子元器件合理选型、应用电路上抗辐照加固设计3种途径。重点从两个方面展开设计:一是高光谱成像仪的结构壳体设计方面,加强金属壳体的屏蔽性能;二是电路设计方面,提高电路抗辐照水平,合理增大成像电路的辐照设计裕度。

2 抗辐照电子学设计

由于卫星所处辐射环境复杂,且航天产品用元器件的辐照敏感存在离散,卫星总体对载荷选用电子器件进行抗辐照设计提出了最小辐射设计裕度(RDM)的要求[9]。高光谱成像仪研制团队多年来在卫星平台的建造规范要求(rRDM≥2)基础上,综合抗辐射加严要求和成本控制,在设计中取rRDM=5,稳健地确保了高光谱成像仪抗辐照设计的可靠性。

(1)

式中:Df为元器件自身的辐射失效剂量;Da为元器件实际所处位置处的辐射剂量。

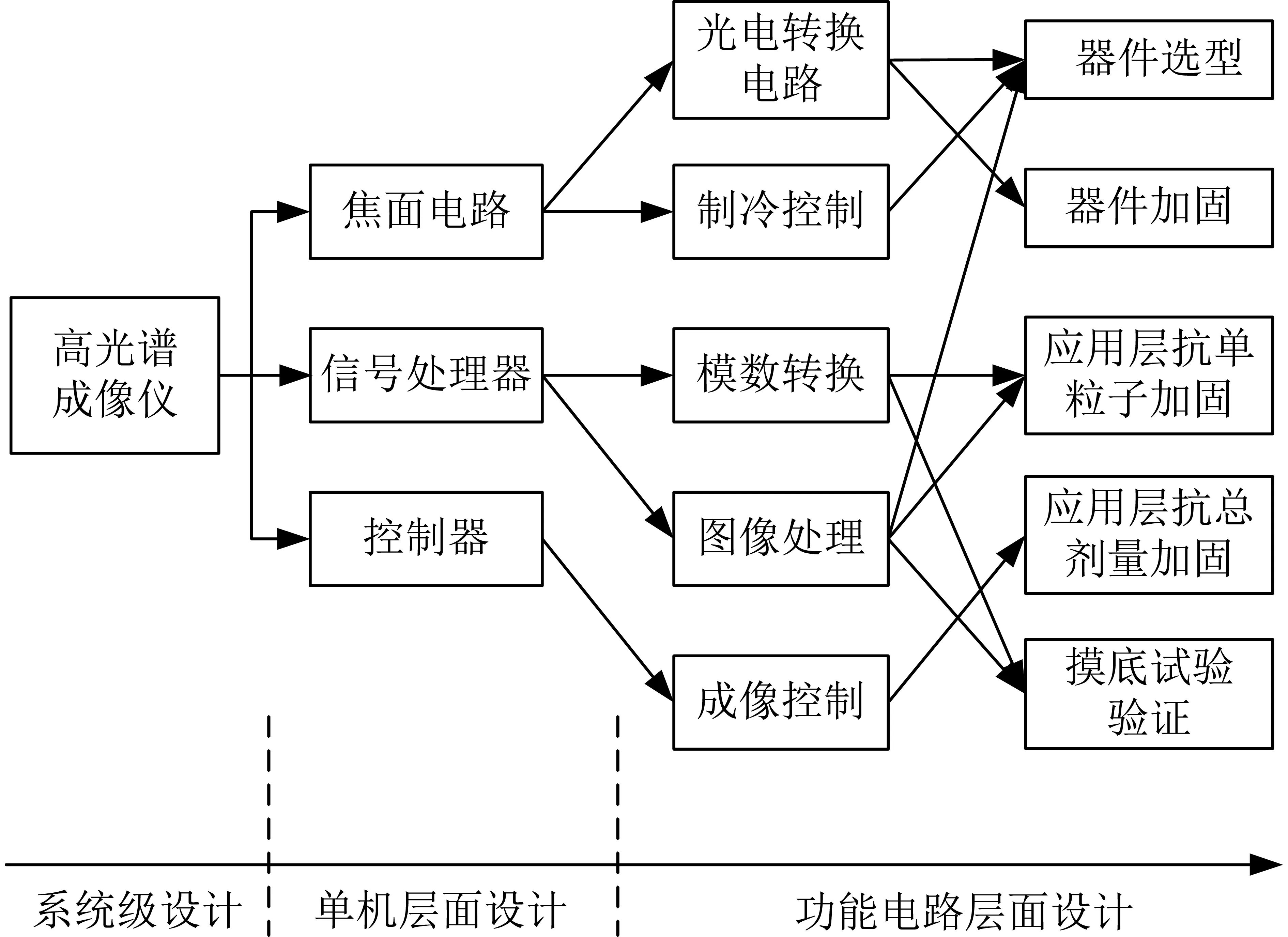

高光谱成像仪采取分层级抗辐照设计的思想,如图3所示,电子学设计从分系统电子学、实现单机、功能电路进行分层,然后从器件选型、器件加固、应用层单粒子加固、应用层抗单粒子加固、摸底试验层等技术手段实现。高光谱成像仪针对性分层级抗辐照电子学设计着重两方面:一是在电路设计前通过选用有较高抗辐射指标的元器件,增强电子学部分的抗辐照能力;二是应用级抗辐射设计,即在元器件使用中,从硬件电路设计、软件设计上采取抗辐射加固措施。

图3 星载高光谱成像仪电子学分层级抗辐照设计Fig.3 Layered anti irradiation design of hyperspectral imager electronics

2.1 目标化的抗电离总剂量设计

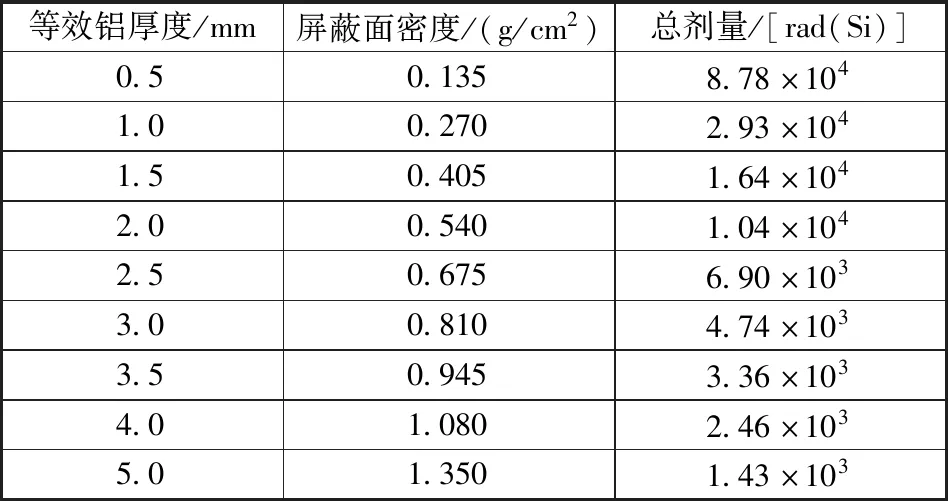

在搭载高光谱成像仪的卫星上,电离总剂量效应指标指电子器件敏感区域的能承受的累积吸收剂量。计算时先将卫星等效成实心球,根据轨道高度H=5×105m,计算球心处的辐射剂量与球的半径R之间的关系,得出卫星在轨寿命期间的辐射剂量随屏蔽厚度的变化曲线,计算数据见表1。

表1 5年期辐射剂量-常用屏蔽深度关系Table 1 Relationship between 5-year radiation dose and shielding depth

设计中选用元器件的原则是综合考虑宇航级器件价格前提下,优先选取有明确抗电离总剂量指标且满足RDM值为5的器件;某些器件不能查询到总剂量指标,但经过调研后能确认有充分的在轨飞行经历的,也进行了选用;对于辐照指标不能直接满足要求的器件,在应用电路上进行附加屏蔽措施。

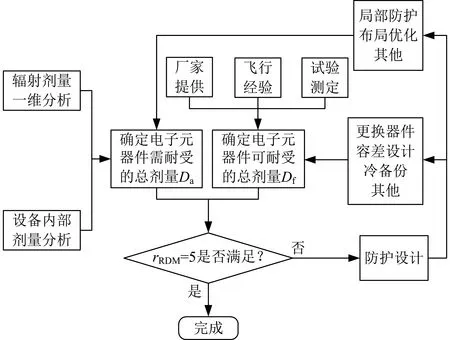

由表1可知,求得500 km圆轨道5年3 mm等效铝厚度的电离总剂量为4.74 krad(Si)。高光谱成像仪抗辐照设计按rRDM=5为5加严,选用电子元器件电离总剂量水平不低于23.7 krad(Si)。按照辐射指标要求,优先选择能直接满足抗辐照指标的电子元器件;对于辐照指标不满足要求的电路,先从应用电路设计方面进行应用加固,再从整体结构设计上进行屏蔽加固。图4描述了高光谱成像仪电子学抗电离总剂量设计的设计流程[10]:通过对设备内部辐照总剂量分析,确定选用电子元器件需耐受剂量Da;然后通过查询器件生产厂提供的辐照试验报告及数据包,明确选用器件可耐受的总剂量Df,以此计算分系统电子学实际是否满足rRDM=5,满足则完成该部分功能电路设计;不满足则通过防护设计进行进一步迭代优化,直至满足RDM设计要求。

图4 面向星载遥感目标的高光谱成像仪电子学抗电离总剂设计流程Fig.4 Design process of electronic anti ionization agent for hyperspectral imager for satellite borne remote sensing target

表2列举了高光谱成像仪关键电子学器件的辐照加固措施。

表2 高光谱成像仪关键器件抗辐照设计措施Table 2 Anti-irradiation design measures for key components of hyperspectral imager

光电转换器件CCD160-250-SFT在空间辐照环境下,会出现电荷转移效率(CTE)降低、体暗电流密度增大、暗信号退化等问题。该款探测器是高速、高灵敏度、高量子效率的背照式2048×256像元面阵CCD,像元尺寸16 μm×16 μm,满阱电荷容量240 ke-,暗电流0.5 nA/cm2,ηCTE>0.999 99。按照用户对光谱复原精度要求,允许5年任务末期CTE值衰减到0.999 90,根据辐射损伤关系,从器件结构屏蔽上加厚1 mm金属屏蔽。

制冷机驱动电路中使用FPGA产生脉宽调制驱动信号来驱动H桥臂的场效应管,频繁突变的电场产生瞬变的磁场,制冷机脉宽调制电路的金属氧化物半导体场效应晶体管(MOSFET)开关频率辐射干扰较强,故舍弃SRAM型FPGA,选用金属对金属结构(M2M)反熔丝工艺A54SX72A,它抗辐照性能好[10],且无需外部程序存储器存储配置文件,提高了制冷驱动电路的可靠性。

用作高光谱成像仪图像信号处理的关键器件XQ5VFX130T,其宇航级产品价格昂贵(市场价200万元/片)且货源紧缺,采用购买工业级器件进行升级筛选,并对其抗辐照能力进行摸底。电离总剂量试验结果表明:采用的这批XQ5VFX130T抗电离总剂量能力达到100 krad(Si),满足星载高光谱成像仪使用要求。

高光谱成像控制电路选用进口的883等级的54HC系列门电路器件,它们总剂量指标不足10 krad(Si),故对该部分电路增加了2 mm钽板附加屏蔽设计,从应用层面提高了控制电路的抗电离总剂量水平[11]。

2.2 针对性抗单粒子效应设计

单粒子在半导体材料中沉积的能量用线性能量传输(LET)衡量,它指高能粒子穿过单位长度硅材料时沉积的能量大小,单位是MeV·cm2/mg。

设计原则:综合器件采购成本的前提下,优先选用较高LET阈值和较低饱和翻转界面的元器件;对于单粒子翻转LET阈值大于15 MeV·cm2/mg的器件,直接选用;单粒子翻转LET阈值小于15 MeV·cm2/mg的器件,在电路设计上进行充分的抗单粒子翻转防护设计,并对防护效果进行评估。单粒子闩锁LET阈值大于75 MeV·cm2/mg的器件,直接选用;单粒子闩锁LET阈值介于37~75 MeV·cm2/mg的器件,电路上进行充分防护设计并评估无风险后选用;单粒子闩锁LET阈值小于37 MeV·cm2/mg的器件,进行充分防护设计并经过试验验证后方能使用。

首先,在选用作为高光谱成像关键器件的光电转换用CCD图像传感器时,为同时兼顾高空间分辨率、光谱分辨率以及高光谱成像仪采用的时空联合调制干涉成像原理,要求CCD满足大面阵、高帧频、多抽头等特性的同时,其抗辐照设计指标需满足空间任务寿命需求。为此,甄选了在芯片设计上使用抗辐照加固的超薄绝缘体上硅(UTSOI)工艺的大面阵高速CCD160-250-SFT,使得其对单粒子闩锁免疫,抗单粒子瞬态能力环比高了约100倍。

其次,针对处理器芯片XQ5VFX130T抗单粒子闩锁能力满足但抗单粒子翻转能力较弱的问题,在电路中设计FPGA的芯片配置存储区回读纠错功能模块,设计用回读刷线配合三模冗余来提升该芯片的抗单粒子翻转(SEU)能力。设计中将该FPGA实现的高光谱成像仪成像功能中驱动时序模块设计三模冗余;模拟视频处理和图像拼接功能模块实现配置刷新,配置刷新的硬件电路采用外部配合控制的反熔丝工艺A54SX72A(对SEU免疫),根据LASIS成像256帧状态一致方能提取谱信息的特点,回读时机设计在每次改变帧频或增益时。

对无抗单粒子效应(SEE)指标的四通道专用CCD模拟视频处理器ADDI7004(以下简称ADC),在应用电路上进行抗单粒子效应加固。设计时首先进行辐照试验和单粒子摸底试验确定其实际的抗辐照指标及单粒子指标,然后进行工业级器件的升级筛选。在视频信号的模数转换电路设计中,针对升级筛选后ADC抗单粒子能力较弱问题,进行应用层的针对性设计:采用热备份+冷备份的硬件电路设计(见图5),即在处理电路上设计成硬件主备份(主备各实现32路模拟视频处理的冷备份),此外,又分别在模数转换电路上设计热备份(32路分别又备份成64路),这样实现了电路在发生单粒子异常时,不通过冷备份即可进行模拟处理电路的热备份切换。

图5 高光谱成像仪抗单粒子双重主备电路结构设计Fig.5 Main and standby dual-circuit structure design of anti single particle for the hyperspectral imager

此外,在FPGA软件中的配置和控制ADC的软件模块中设计了健康状态监测,通过设计状态机实时监测同步字来判断单粒子闩锁是否发生,并配以动态刷新ADC的内部可编程配置寄存器的功能模块来提高其配置可靠性;当软件检测到ADC发生单粒子闩锁时,FPGA触发电源控制信号,采取强制断电掉电来解除闩锁。软件检测异常的功能模块设计如下(见图6):关键参数包括ADC芯片掉电需要的最小时间T0与上电需要的最小时间T1,ADC的复位时间T2,ADC判断为故障时间阈值T3,两次故障之间的最小间隔时间T4;设计工作过程:系统上电,对ADC的寄存器进行定时刷新;同时对ADC输出的行标志字进行检测,计算相邻两个行标志字的间隔T。

图6 ADC抗单粒子软件功能设计过程Fig.6 Function design of ADC anti single event software

步骤1:第一次故障判断。

情况A1:当T≤T3时,则判断为ADC工作正常,不采取额外的操作;

情况B1:当T>T3时,则判断为ADC发生故障。

步骤2:第一次故障处理。

停止刷新寄存器,将ADC的外部复位信号置为低电平,当复位信号的低电平持续时间达到T2之后,复位信号置为高电平,对ADC重新进行初始化参数配置操作;在此期间,FPGA对ADC对应的图像自动填0;ADC芯片继续工作,继续对ADC的寄存器进行定时刷新,同时对ADC输出的行标志字进行检测,继续计算相邻两个行标志字的间隔T。

步骤3:第二次故障判断。

情况A2:当T≤T3时,则判断为ADC芯片工作正常,不采取额外的操作;

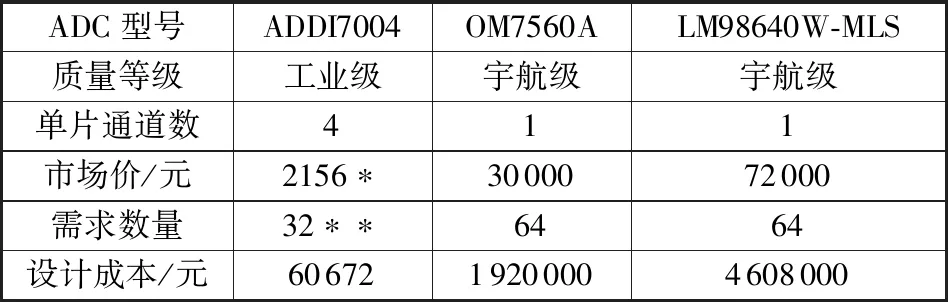

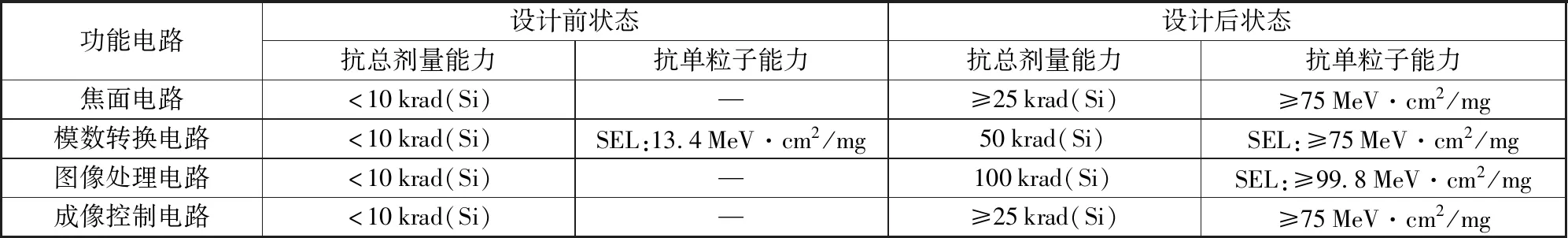

情况B2:当T3 情况C:当T>T4时,则判断为ADC芯片发生故障,且第一次故障处理解决了寄存器的单粒子锁定问题,则继续采用步骤2进行故障处理; 步骤4:对故障情况B2的处理。 停止寄存器的刷新,将ADC的电源芯片的使能置为无效,进行掉电操作; 掉电时间达到T0之后,将电源芯片的使能置为有效,进行上电操作; 上电时间达到T1之后,对ADC芯片进行复位操作(当复位信号的低电平持续时间达到T2之后,复位信号置为高电平)、配置寄存器参数的操作;在此期间FPGA对ADC芯片对应的图像自动填0。 在第二次故障处理后,若再次出现故障情况B2,则判定ADC彻底损坏无法修复。软件修复停止,转为硬件热备份切换。 为提高卫星载荷的抗辐照能力,单纯依赖选用抗辐照指标较高的宇航级器件,固然能提高产品的抗辐照能力,但研制成本较高[12]。高光谱成像仪抗辐照设计中从器件选型、电路设计、系统设计3个层面兼顾了抗辐照能力和研制成本。表3列出了在CCD模拟视频处理电路中,比对采用抗辐照指标较高的OM7560A或LM98640QML-SP与升级筛选ADDI7004的硬件设计成本,OM7560A采购单价约为人民币3万元/片,宇航级LM98640W-MLS国内销售价约8万元/片。通过综合对比,确定了在兼顾抗辐照能力的条件下,选择硬件成本最低的设计方案,即升级筛选工业级ADDI7004。 表3 高光谱成像仪关键器件抗辐照设计措施Table 3 Anti irradiation design measures for key components of hyperspectral imager 为测试高光谱成像仪的抗辐照设计有效性,按相关标准对高光谱成像仪鉴定级产品进行了地面模拟辐照试验。四路模拟视频处理器ADDI7004为高光谱成像仪分系统信号链路中的抗辐照最薄弱环节,可等效认为其即代表了分系统最低的抗辐照能力,进行的摸底试验主要是单粒子效应测试和辐照总剂量测试。 单粒子摸底测试中分别使用Bi/Ge/Ti/Cl/F粒子,在99.8/37.3/22.2/13.4/4.4 MeV·cm2/mg的LET阈值条件下,对同批次的ADDI7004进行了单粒子效应辐照试验,从试验数据得出结论:该批ADDI7004的单粒子锁定LET阈值大于13.4 MeV·cm2/mg; 用重离子回旋加速器(HIRFL)的Bi粒子,对同批次的XQ5VFX130T型FPGA进行单粒子辐照效应评估,试验表明:该批次器件抗单粒子锁定的LET阈值大于99.8 MeV·cm2/mg,单粒子翻转阈值仍显不足,需考虑软件刷新设计。 用钴-60γ射线源,剂量率设为0.1 rad(Si)/s,对同批次的ADDI7004分别在总剂量为0 krad(Si)、30 krad(Si)、50 krad(Si)、高温加速退火后,共4个测试点进行了测试,试验结论如下:该批器件抗电离总剂量能力大于50 krad(Si)。 用钴-60γ射线源,剂量率设为10 rad(Si)/s,对同批次的XQ5VFX130T型FPGA进行辐照评估,总剂量点分别为0 krad(Si)、100 krad(Si)、高温加速退火后共3个测试点进行了测试对比,得出试验结论:该批次器件抗电离总剂量能力达到100 krad(Si)。 表4给出了分系统功能电路在辐照设计前后的能力对比情况,通过在电路应用中的抗电离总剂量薄弱环节局部增加金属屏蔽防护等加固设计,使得仪器电子学电离总剂量敏感器件抗辐照设计余量RDM大幅提高;通过更换器件、软件加固及动态刷新等机制,分系统功能电路抗单粒子锁定能力显著提升,分系统满足500 km轨道高度5年期遥感高光谱成像任务需求。 表4 高光谱成像仪抗辐照设计前后有效性比对Table 4 Effectiveness comparison of hyperspectral imager before and after anti irradiation design 本文依据高光谱成像仪工程化电路设计中的探索及迭代积累的经验,结合目前最新的抗辐照设计及测试技术,提出了针对性地进行星载高光谱成像仪的分层级抗辐照设计方法,将整个系统电子学研制分层成器件、模块电路、系统电子学,按照“先器件,后应用;先电路设计,后辐照屏蔽”的设计原则,实现了星载遥感高光谱成像仪在兼顾研制成本条件下的长寿命、高抗辐照设计指标,并且经过了工程化测试验证。为确保大孔径干涉高光谱成像仪在技术创新和工程化实现两方面均保持高灵敏-(高分辨率、高信噪比)、识谱准(高光谱分辨率)的领先优势夯实了基础,也为寻求星载高光谱成像仪抗辐照设计的高效方法和技术手段进行了有益探索。2.3 抗辐照能力与设计成本的均衡化

3 测试与试验验证

3.1 单粒子测试验证

3.2 辐照总剂量试验测试

4 结束语