一种面向超高速以太网的双模RS解码器设计

2023-02-19李继豪沈剑良

李继豪,沈剑良,陈 艇

(中国人民解放军战略支援部队信息工程大学 信息技术研究所,河南 郑州 450002)

2017年IEEE发布了802.3bs协议,标志着200 Gb/s,400 Gb/s以太网正式投入使用。从早期的10 Mb/s发展到现在的400 Gb/s,以太网带宽的不断增大提升了信道容量,但也带来了信道损耗、信号间干扰、误码率等问题[1]。为了降低传输误码率,满足以太网对传输可靠性的要求,IEEE以太网标准规定100 Gb/s以上以太网必须使用FEC对传输过程中发生的错误进行检测与纠错[2]。

当前100 Gb/s以上以太网使用的FEC纠错码有两种:RS(528,514,7)码和RS(544,514,15)码。RS码是在伽罗华域GF(2m)上运算的一种线性分组循环码,对于RS(n,k,t)码,n是码字长度,k是信息位长度,t=(n-k)2表示最大可纠错个数。RS码具有极强的随机错误和突发错误纠正能力,广泛应用于有线通信、无线通信、光通信等领域[3]。

根据IEEE 802.3第73条自动协商结果,端口中的PCS层需要支持两种不同规范的FEC编解码方案。为在同一个端口中支持两种规范,解码器中需要两个专用实例分别执行RS(528,514)和RS(544,514)的解码功能,而同一时间只能按照一种规范来进行传输。这意味着在以RS(528,514)为FEC方案的数据传输过程中,只有RS(528,514)解码器占用的资源处于工作状态,RS(544,514)解码器资源处于空闲状态,造成了资源浪费。

当前主流的方法是对以太网FEC解码模块中的两种RS解码器分别进行优化设计,通过对解码器中SC、KES、CSEE模块的并行设计[4-5]、流水线处理[6]、降低关键路径,来提升传输速率,降低时延。但随着以太网传输速率提升到800 GB,1.6 TB甚至更高,以太网支持的FEC类型更多,针对每一种FEC解码器进行优化设计的方法产生的效果越来越小,并没有从根本上解决解码资源占用率高、资源利用率低的问题,解码芯片中包含多个独立的解码模块,造成了面积、资源和功耗的浪费。

RS码的多模解码器最早由Hsu Huai-Yi设计[7],实现了0≤t≤8,0≤n≤255多种RS码的解码。该设计不足之处在于:需要手动配置来更换RS码编解码模式,最大吞吐量仅为3.2 Gb/s,无法适用于超高速以太网。文献[8]中提出了一种适用于Polar码、LDPC码、Turbo、卷积码的多模解码器,支持WiMAX等多种协议,但该设计考虑的是不同种类FEC码之间的融合,没有考虑不同参数RS码的解码器融合问题。

本文针对以上问题,将双模RS解码器的思想引入以太网解码器设计,提出一种能够针对RS(528,514)和RS(544,514)两种FEC编码方式进行解码的双模解码器,同时基于Vivado等软件构建该RS双模解码器设计的仿真测试平台。

1 RS解码原理

以太网中RS解码采用硬判决解码,BM算法及其改进算法由于关键路径短、易于硬件实现,是当前以太网RS解码器硬件设计中的主流算法[9]。

硬判决RS解码器主要包含三个模块:

1)SC模块。根据接收到的码字,SC模块计算求出校验子Si(0≤i≤2t-1),如果Si全为0,则传输的数据没有产生误码。

2)KES模块。KES模块对SC模块产生的伴随式S(x)进行求解,得到错误多项式Λ(x)和错误值多项式Ω(x),这一过程称为关键方程求解。

3)CSEE模块。CSEE模块使用钱搜索算法求解出错误多项式Λ(x),得到每个错误出现的位置,通过Forney公式计算每个位置处码字的错误值。

除了这三个主要模块之外,还有用于存储接收数据的缓存区,RS解码器工作流程如图1所示。

图1 硬判决RS解码器流程

1.1 SC计算

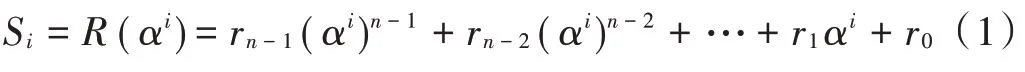

RS解码器输入为接收信息多项式R(x)的各项系数,R(x)=rn-1xn-1+…+r1x+r0,SC模块根据接收码字多项式R(x)计算出校验子Si,公式如下:

如果所有校验子值都为0,表明传输过程中没有发生错误,接收码字多项式R(x)等于发送的码字多项式C(x);否则表明传输过程中发生了错误。错误多项式表示为:

式中:ejv为错误幅值;xjv表示错误位置;v表示错误个数且0≤v≤t,接收码字R(x)=C(x)+E(x),将ri=ci+ei代入式(2)可得:

令αjl=βl来指示错误位置,则有:

当0≤v≤t时,2t个方程可以解出2v个未知数β1~βv,ej1~ejv,由此求出错误多项式E(x)与解码输出码字R(x)。当v>t时,传输过程中发生的错误个数超出了RS(n,k,t)码的纠错能力上限,无法恢复发送端的原始信号。

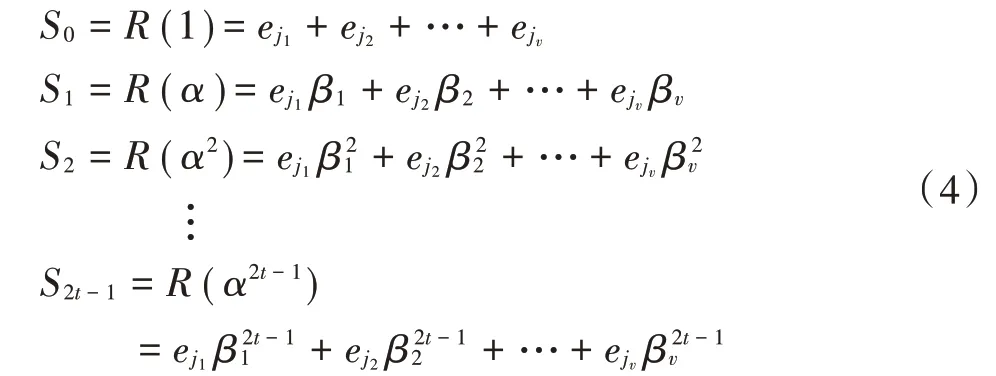

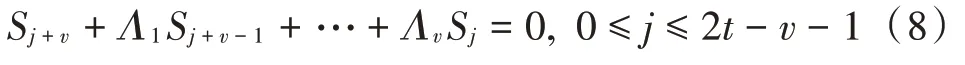

1.2 关键方程求解

直接求解2t个方程会带来大量的复杂计算,采用间接方法能降低计算复杂度,易于硬件实现。错误位置多项式表示为:

令Λ(x)=0的根为β-1k(k=1,2,…,v),代入式(5),经过变换:

对k求和:

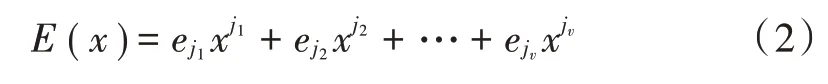

将式(4)代入式(7)得:

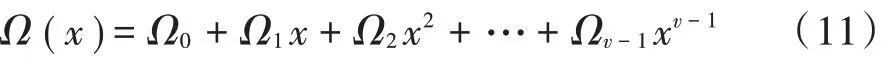

由Ω(x)=S(x)·Λ(x)得:

由式(8)得出式(9)中x次数高于v-1的项系数全为0,而S(x)中Si(i≥t)的项数均为0,因此Ω(x)最高次数不超过2t-1,即:

式(10)称为关键方程[9],Ω(x)为错误值多项式,满足:

关键方程的求解是RS码解码过程中最关键的步骤,Berlekamp和Massey最早提出BM算法对关键方程求解[10],此后研究者们不断对BM算法进行改进,提出了无求逆的IBM算法[11]、RIBM算法[12]、ePIBM算法[13]等。

1.3 钱搜索与Forney算法

在完成关键方程求解后,下一步是根据错误位置多项式Λ(x)和错误值多项式Ω(x)计算错误位置和错误值,采用钱搜索算法完成错误位置搜索,通过Forney算法计算出错误值。钱搜索算法对r n-1,rn-2,…,r1,r0依次进行验证,将有限域中的所有元素代入Λ(x)中求解,求出Λ(x)的根,这个遍历GF(2m)域中所有元素求解Λ(x)根的过程就是钱搜索。二进制码可以通过对错误位置进行比特翻转完成解码,但对于多进制码,还必须计算错误位置处的错误值,在得到错误位置之后,借助Forney算法可完成错误值ejl的计算,其公式表示如下(本文中m0取0):

2 双模RS解码器硬件结构

2.1 设计思路

文献[7]中给出了多模RS解码器的设计思路,属于同一种伽罗华域的RS码,其解码器的各个模块都具有相似性,这为融合设计提供了可能。

当前100 GB以太网FEC的两种规范RS(528,514)码和RS(544,514)码具有共同的域GF(210),域中每个元素对应的位数和值都相同,因此两者共用一个元素值表。SC模块中RS(528,514)中的校验子计算逻辑是RS(544,514)中计算逻辑的一个子集,后者的校验子计算电路经过修改可以直接用于前者的校验子计算。两种RS码KES模块中的初始值λ,b,γ,k和计算步骤相同。CSEE模块中钱搜索对GF(210)域中全部1 024个元素依次验证,寻找使得Λ(x)=0的根,根的倒数代入式(12)计算错误值。由于RS(528,514)和RS(544,514)共用所有元素,遍历根的过程完全相同。基于以上分析,本文针对以太网中RS(528,514)和RS(544,514)两种FEC解码标准设计了一种通用的RS双模解码器。

2.2 并行双模RS子模块设计

2.2.1 双模SC模块

本文设计的SC模块校验子计算结构包含2t2个SC计算单元PE0,如图2所示。解码器接收到码字后,此模块进行伴随多项式计算,当解码模式为RS(528,514)时,调用其中的t1=14个PE0单元完成校验子计算,RS(544,514)的解码模式下使用全部的t2=30个PE0单元完成30个校验子Si的计算。

图2 双模SC模块校验子计算结构

融合后的SC模块相较于单模解码器,既省去了14个校验子计算单元,又减小了一种解码模式运行时另一套解码模式空闲的资源数量,提高了资源利用率。除此之外,SC计算单元PE0中乘法器输入元素α0~α2t2-1的存储空间同样共享。

p路并行的SC模块每个时钟周期传输p个符号数据,同一时钟内每个PE0需完成p个符号的计算量,即p次加法运算与p次乘法运算,被乘数αi具有规律性,提前计算出所有被乘元素存入矩阵即可在单周期内完成并行计算。

2.2.2 双模KES模块

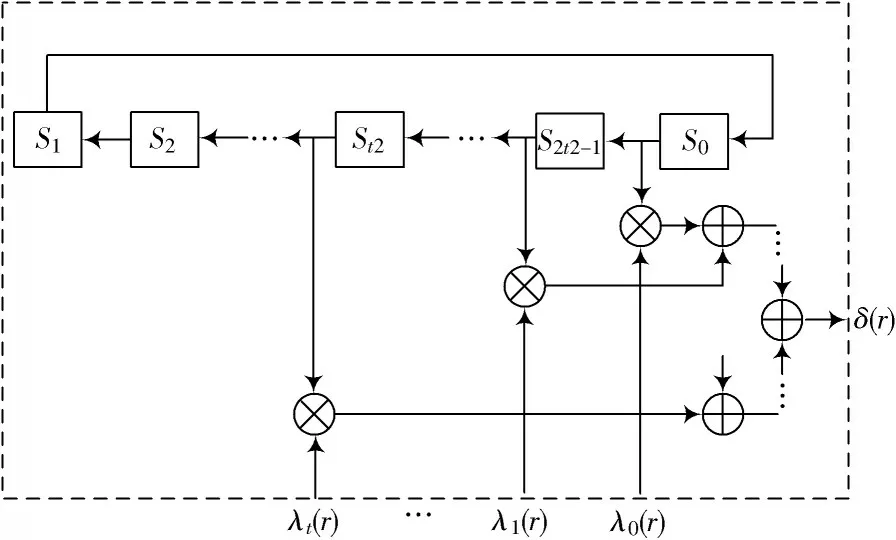

KES模块随着伴随式的输入,完成计算过程。本文双模KES模块采用IBM算法,KES模块电路结构分为DC和ELU两部分,如图3、图4所示。

图3 KES模块DC结构

图4 KES模块ELU结构

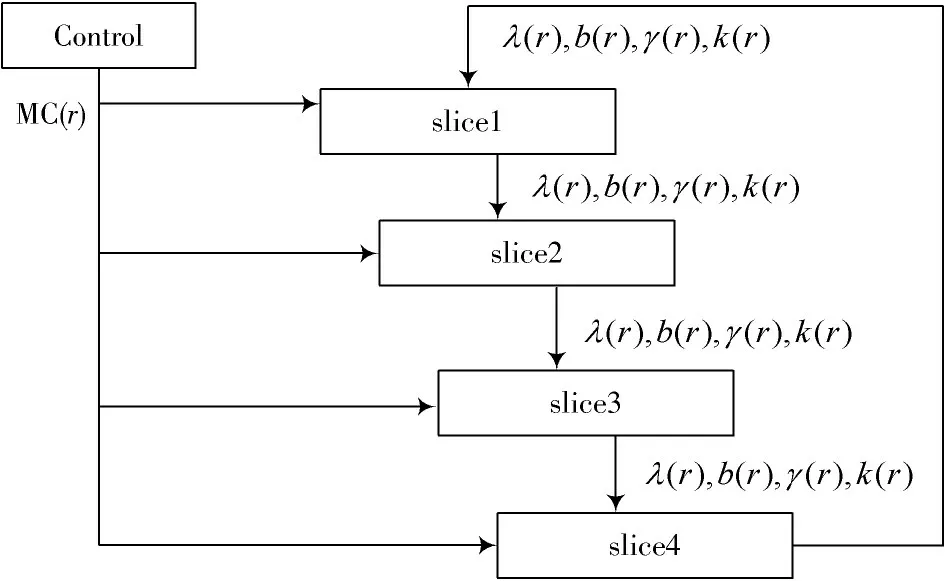

图4中,MC(r)为控制信号,前2t次迭代,DC模块中寄存器存放有SC模块计算的校验子值S1,S2,…,S2t2-1,S0。首次迭代时,ELU模块根据初始值尝试计算出2t个关键方程的解,获得第一次迭代的λi(t)值输入DC模块。经过2t2次迭代后错误位置多项式Λ(x)各阶系数Λi=λi,第2t+1次迭代DC块中寄存器内的值更新为S1,S2,…,St,0,…,0,S0,Λi作为输入历经t次迭代计算出错误值多项式Ω(x)各阶系数Ωj。当工作模式为RS(528,514)时,调用双模KES模块的部分资源完成计算。传统基于IBM的RS解码器3t次迭代需要3t个周期,本文在双模KES模块的基础上设计了流水线结构,采用4个slice,每个时钟周期迭代4次,进一步降低解码时延,其具体结构如图5所示。每个slice包含一个DC模块与ELU模块,同一slice的DC模块中存储Si的寄存器每个时钟周期移位4次。在流水线处理模式下,上一个slice的输出作为下一个slice的输入。采用4个slice的流水线结构虽然会增加额外的资源开销,但是能够缩减KES模块迭代时间,满足以太网中FEC解码器中的传输速率。slice模块受控制信号MC(r)的控制,可以通过设置在RS(528,514)模式下启用2个slice,RS(544,514)模式启用4个slice,使两种模式下KES模块解码周期相同,实现多个使能信号的复用。

图5 基于流水线的双模KES结构

2.2.3 双模CSEE模块

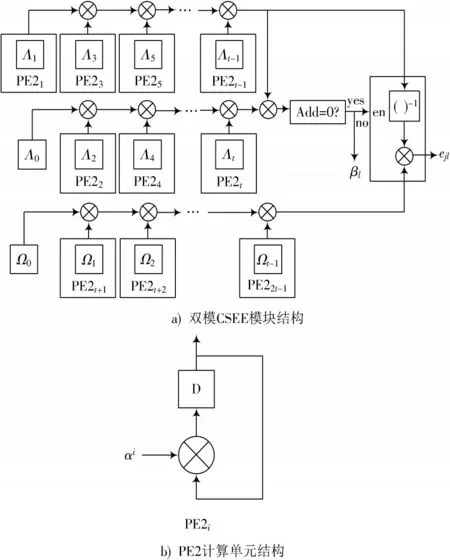

图6a)给出了双模CSEE模块的结构图,每个PE2计算单元包含一个乘法器和一个寄存器,如图6b)所示,使用2t-1个PE2单元完成错误位置与错误值的计算。PE21-PE2t中寄存器存储了KES模块计算的Λi,PE2t+1-PE22t-1中寄存器存储了Ωj。

图6 PE2计算单元结构和双模CSEE模块结构

将GF(210)中所有元素代入式(5)进行验证,如果Λ(αi)=0,则r n-i出现错误。传统CSEE模块时延为n个周期,采用l路并行的方式,可将延时缩短为n l,再经过流水线处理,进一步降低CSEE模块时延。错误位置计算出后,式(12)计算错误值的过程中有求逆运算,为了提高计算速度,将GF(210)中n个元素与其求逆后的值一一对应存入查找表中,将除法操作转换为查找表操作。RS(528,514)码和RS(544,514)码同属于伽罗华域GF(210),具有相同的本原多项式x10+x3+1,因此同样共用一个查找表。

3 仿真及性能分析

本文实验的仿真部分在Vivado、VCS等平台上进行,基于第2节的双模RS解码器设计了100 GB以太网标准下双模RS解码器,输入为4路80 bit位宽的SerDes并行数据,时钟频率为333 MHz。双模解码器每个时钟周期内输入32个符号数据,RS(544,514)码的每个码字恰好在17个周期内传输完成。为保证双模解码器解码流程的一致性,需提前将RS(528,514)码的每个码字进行预处理,在每个码字最后添加16个符号的数据“0”,补足544个符号,预处理流程开始于SerDes数据传输之前,传统100 GB以太网在将数据送入解码器之前同样会进行预处理,因而本文设计预处理部分不归于双模RS解码器设计,不占用解码器资源。通过硬件描述语言Verilog进行设计,对双模RS解码器进行功能验证,RS(528,514)解码模式的功能验证结果如图7a)所示。其中,rsd_data_i是输入信号,被标记的rsd_data_o为输出信号,rsd_chfr_err_den_i和rsd_chfr_err_num_i分别对应错误位置和错误值,err_mag_o是计算得到的错误图样,men_rd_data_i是存储在FIFO区的输入数据,symb_err_o为错误计数信号。对于添加的7个错误,设计的RTL代码能成功完成纠错,在Testbench频率设置为500 MHz时,RS(528,514)工作模式的时延为31个时钟周期62 ns。

图7b)给出了RS(544,514)解码模式的功能验证结果,输出信号rsd_data_o和插入的15个错误err_mag_o被标出,结果显示成功完成了对接收码字中的15个符号进行纠错,产生的时延为32个时钟周期64 ns。由此推算333 MHz的时钟频率下,两种解码模式的时延分别为93 ns和96 ns,优于文献[4]中的106 ns和166 ns。实验证明,设计的双模RS解码器能够成功实现RS(528,514)和RS(544,514)两种模式的解码。使用Vivado软件平台对双模RS解码器进行综合验证和布局布线仿真,FPGA选择Xilinx公司Virtex UltraScale+HBM系列xcvu35pfsvh2892-3-e,I/O标准选择LVCMOS12。对100 GB以太网下集成两种单模RS解码模块的传统以太网RS解码器同样进行仿真测试。为了对比公平性,参考文献[4]的设计思路撰写了两种单模解码器的RTL代码,保持与本文双模RS解码器代码风格、内部功能模块一致性。选择输入并行数p=32,每个周期传输32个符号的数据,时钟周期同为333 MHz。表1给出了100 GB以太网双模RS解码器与传统RS解码器[4]资源开销对比。

图7 RS(528,514)、RS(544,514)码功能验证

结果表明,使用传统方法设计的RS解码器资源消耗为118 962个LUT,10 100个FF,本文设计的双模RS解码器消耗80 518个LUT,6 309个FF,分别减小了32.32%的LUT与37.53%的FF资源开销。各个子模块之间的使用资源对比同样在表1中给出,相比于传统RS解码器,SC、KES、CSEE模块LUT开销分别降低了28.11%,22.32%,34.45%,FF开销分别降低了31.94%,29.10%,44.60%。双模RS解码器不仅降低了资源开销,还减少了解码器中空闲资源数量。传统解码器中两种解码实例独立存在,没有共用的资源和内存,以RS(528,514)的解码模式为例,RS(544,514)工作模式的资源处于空闲状态,实际上的资源利用率不到50%。双模RS解码器各个子模块之间存在资源共享、内存共享,工作时空闲的资源更少,减小了静态功耗。

表1 双模RS解码器资源使用情况

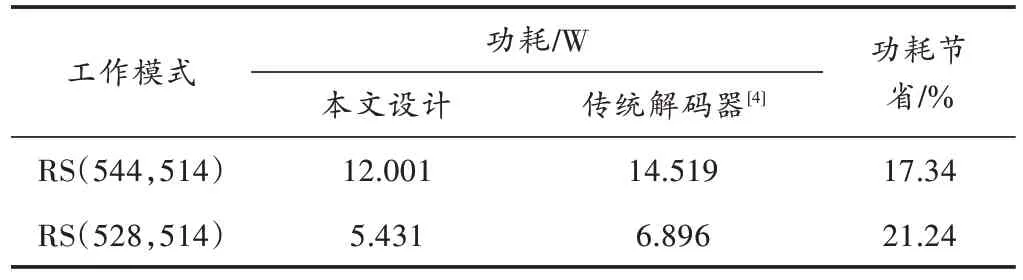

表2所示为双模RS解码器与传统解码器的功耗情况,通过对比,本文设计的双模RS解码器至少能降低17.34%的功耗。

表2 双模RS解码器功耗对比

当前100 GB及以上以太网FEC编解码规范只有RS(528,514)和RS(544,514)两种,事实上,本文设计中的双模RS解码器不仅能实现这两种工作模式的解码,而且对于满足元素域为GF(210),n≤544,t≤15的任意RS(n,k,t)码,此设计都能在现有的资源下实现前向纠错功能。综上,本文设计中的双模RS解码器不仅能解决当前100 GB以上以太网中RS(528,514)和RS(544,514)两套解码模块资源不能共享的问题,还具有可扩展性,当更高速率以太网采用RS码作为FEC标准时,该设计思路同样有效。

4 结 论

本文提出一种面向超高速以太网的双模RS解码器设计,通过对各子模块进行理论分析与优化设计,实现不同工作模式下资源复用和部分内存共享,达到降低资源开销和功耗的目的。实验部分通过硬件描述语言Verilog构建100 GB以太网下的双模RS解码器,在Vivado等平台上进行仿真验证。实验结果表明,该双模RS解码器相对于集成了两个单模RS解码模块的传统FEC解码器至少降低了32.32%的LUT与37.53%的FF资源开销,以及17.34%的功耗。