高分辨雷达成像目标模拟系统均衡方法研究

2023-01-17王立权韩志强陈泓玮杜溢华

徐 啸,王立权,韩志强,陈泓玮,杜溢华,许 哲

(上海机电工程研究所,上海 201109)

随着军事需求的不断增强以及电子对抗技术的飞速发展,宽带成像制导技术正成为各个国家的研制热点。宽带信号可实现较高的距离分辨率,具有较强的抗杂波能力,在高分辨成像方面具有很大的优势[1],国内外已有多款宽带高分辨雷达模拟系统研制成功。在针对高分辨雷达成像导引头所设计的宽带半实物仿真系统中,射频信号需经多级变频、移相、放大、滤波等信号处理[2]。系统通过实时在线调取幅相补偿数据库,均衡链路器件引起的幅相误差。补偿后的系统角模拟精度主要由频率步进Δf决定。想要获得较高的角模拟精度,需要选择较小的频率步进,而较小的频率步进会增加校准的工作量且难以适用于宽带成像系统[3]。

传统的半实物仿真目标模拟系统升级为能够模拟高分辨成像目标的瞬时宽带系统,理论上可以将馈电系统中的所有窄带器件全部替换成宽带器件,但是目前宽带衰减器及移相器等器件尚未能达到工程级别,且价格昂贵,系统改造成本急剧增加[4];文献[5]提出了一种提高射频半实物仿真宽带信号角模拟精度的方法。该专利提出了一种以数字化幅相表补偿宽带信号的方法,解决了宽带雷达信号模拟的技术难题,但本质上模拟精度仍取决于补偿频率步进。本文提出了一种基于数字调制的高分辨雷达成像模拟系统均衡方法,该方法首先用数字调制的方式实现传统的精控单元,并基于VLSI 算法设计三路并行幅相补偿滤波器,完成高分辨雷达成像目标角位置精确模拟。

1 幅相误差对高分辨雷达成像目标模拟系统的影响分析

半实物仿真目标模拟系统一般通过经典的幅度重心算法[6],精确控制目标在三元组阵列内的位置。

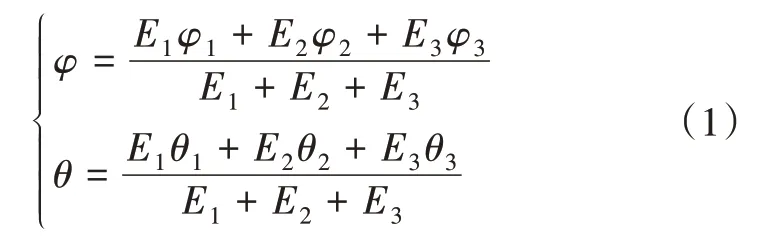

根据幅度重心公式,目标的空间位置可以表示为

式(1)中,E1、E2、E3分别表示3 个天线辐射的能量;φ1、φ2、φ3是3 个天线的相对方位角;θ1、θ2、θ3为3 个天线的相对俯仰角。

幅度重心公式使用的前提是3 个喇叭天线辐射的射频信号相位是一致的。通过控制三元组的3 个天线的幅度值精确定位三元组的辐射中心所在的空间位置[7]。传统的射频阵列系统一般对单频点进行校准,很难保证宽带内3 个通道所有频点的幅度相位保持一致,难以实现高分辨雷达成像目标角位置模拟。

另外,SAR 图像由距离向和方位向2 个脉冲压缩过程组成,由于幅相误差对每个距离向脉冲压缩响应影响一样,不会引起方位向额外的幅相误差,进而影响方位向脉冲压缩峰值处相位,因此,只需分析信号单通道幅相误差对SAR 距离向脉冲压缩后峰值处相位的影响。文献[8]分析了仅存在幅度误差时,不影响脉压峰值处的相位,即幅度误差不会对图像的相位保持特性产生影响。因此,只需分析通道相位误差对成像距离向脉冲压缩后峰值处相位的影响。

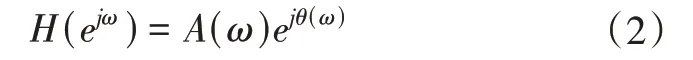

假设系统的传递函数为

其中,A(ω)是系统的幅频失真特性函数,θ(ω)是系统的相频失真特性函数。为分析带内误差对系统的影响,可作如下展开[7]:

由成对回波理论[8]可知,信号通过幅相特性非理想的系统时,在输出端除期望信号分量外,还会出现成对回波,成对回波与主回波叠加,将影响脉压响应主瓣展宽系数(Kml)、峰值旁瓣比(PSLR)和积分旁瓣比(ISLR),进而影响最终的制导精度。

2 基于数字调制的均衡方法设计

2.1 数字均衡算法总体架构

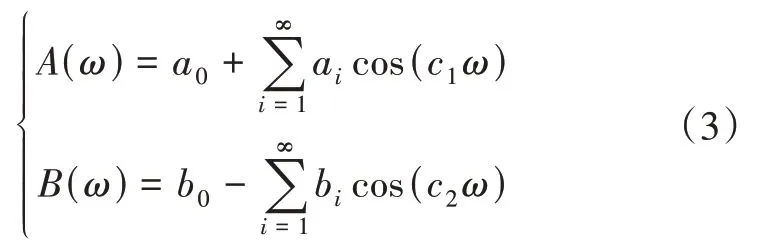

传统的半实物目标模拟系统主要包含仿真控制系统、回波模拟器以及阵列馈电系统,如图1所示。闭环仿真时,仿真控制系统通过调取幅相补偿表的方式完成单频点补偿。对于本文研究的高分辨成像模拟系统,该方法无法同时完成有效工作带宽内全部频点补偿,因此,需要一种宽频带的补偿方法,精确地补偿链路幅相畸变,以达到高分辨雷达成像系统的模拟要求。

图1 传统半实物目标模拟系统组成Fig.1 General architecture of the traditional HWIL target simulation system

本文将模拟器输出的三路信号直接连接至阵列馈电系统的精控前端,通过调节模拟器三路信号的幅度和相位实现目标位置的空间合成,并利用模拟器的数字平台进行全链路均衡运算,完成高分辨雷达成像目标模拟。

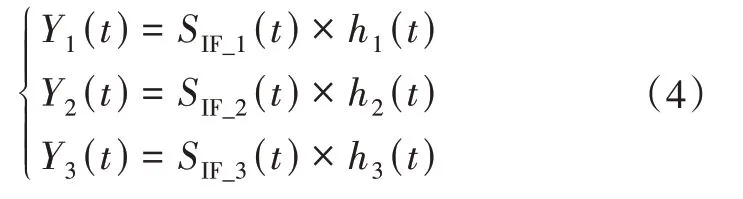

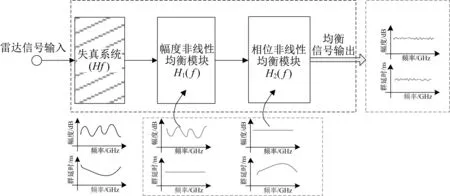

本文设计的数字均衡算法总体架构如图2所示。主动雷达信号经过模拟器下变频链路之后变成中频信号,中频信号经过DRFM 进行相关数字信号处理之后再经过均衡补偿模块,补偿后三路数据通过上变频传输给信号模拟器的输出端,即Y1(t)、Y2(t)、Y3(t)。

Y1(t)、Y2(t)、Y3(t)分别传输至馈电阵列系统的A、B、C3个链路,h1(t)、h2(t)、h3(t)为3个通道传递响应函数,馈电系统接收计算机实时控制模块下发的控制指令选通指定的支路,将信号传输至天线阵列系统中对应的三元组天线,完成高分辨雷达成像模拟。

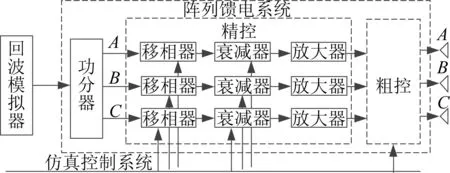

2.2 幅相均衡模块设计

工程上通常用复系数FIR 滤波器来实现系统的幅相补偿,但是此类滤波器的设计方法存在误差约束方法不足、群延时误差约束非凸性、设计方法通用性差等问题[9]。为高效实现高分辨雷达成像目标模拟,本文采用对称系数FIR 幅度补偿滤波器和全通相位补偿滤波器结合的方法设计幅相均衡模块如图3所示。

图3 数字均衡模块结构设计Fig.3 Structure design of the digital equalization module

由于脉冲响应系数为有限项,因此FIR滤波器始终是稳定的,并且一般情况下系数满足一定的对称性,能够得到严格的线性相位,保证数字信号不发生畸变。本文幅度非线性均衡模块采用对称系数FIR滤波器实现,其传递函数与系统幅度响应函数A(ω)存在如下关系:

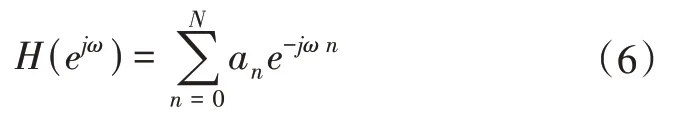

N阶FIR滤波器的传递函数如下:

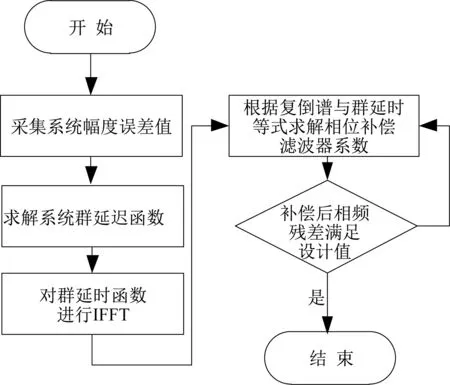

在得到系统的幅度误差失真特性之后,即可基于Matlab滤波器设计工具快速求解幅度非线性均衡滤波器系数,具体设计流程如图4所示。

数字全通滤波器幅度恒定,其相频特性可以根据需要做出相应设计[10]。一般情况下如果系统对相位特性有特殊要求,而又要求不能改变其原有的幅度响应,全通滤波器是较好的选择。

N阶全通滤波器的传递函数如下:

其中,z=ejw,ω=2πf,f是归一化频率,根据式(6)可以求出整个滤波器的相频响应,即

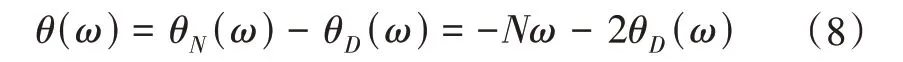

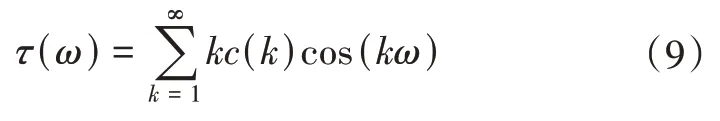

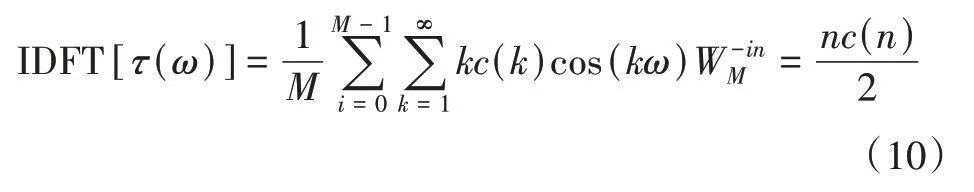

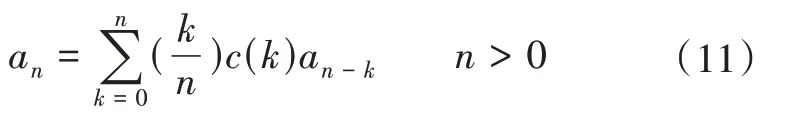

其中,θN(ω)和θD(ω)分别是H(z)的分子多项式N(z)和分母多项式D(z)的相频响应。由全通滤波器的性质可知:它的分母具有最小相位;而一个最小相位序列的群延迟函数及其复倒谱系数之间满足如下关系:

对式(8)进行傅里叶反变换得到

再根据式(9),得到

其中,a(0)=1。由式(10)可得全通相位均衡滤波器传递函数H(z),全通均衡模型可以根据群延迟函数建立。具体设计流程如图5所示。

图5 相位非线性均衡滤波器设计流程Fig.5 Flow chart of the nonlinear equalization filter design for phase

2.3 基于FFA级联的均衡算法高效实现结构

在高速信号处理领域,系统架构一般采用并行处理方式,在架构中FIR滤波器单元被多次重复利用,造成硬件资源浪费,实现一个L路N阶的并行滤波器,需要消耗(N×L)个乘法器[11]。本文所研制的高分辨雷达成像模拟系统时,若数字处理架构采用一路高速并行计算,所计算的滤波器阶数为100阶,那么仅这一模块所需要的乘法器就达到1600个,三路滤波器消耗的乘法器资源达到4800个,而本文研制系统采用的KU115平台乘法器数量为5520,占用量达到86.9%,严重影响其他功能的实现,所以需要寻找新的并行解决方案。

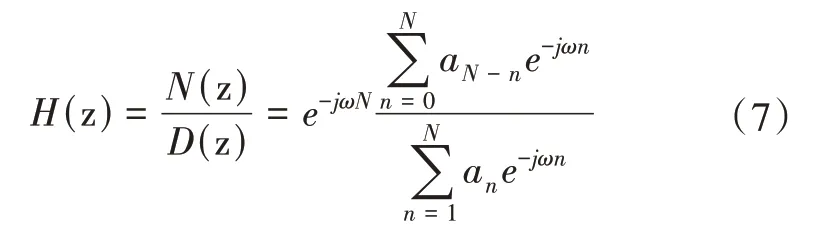

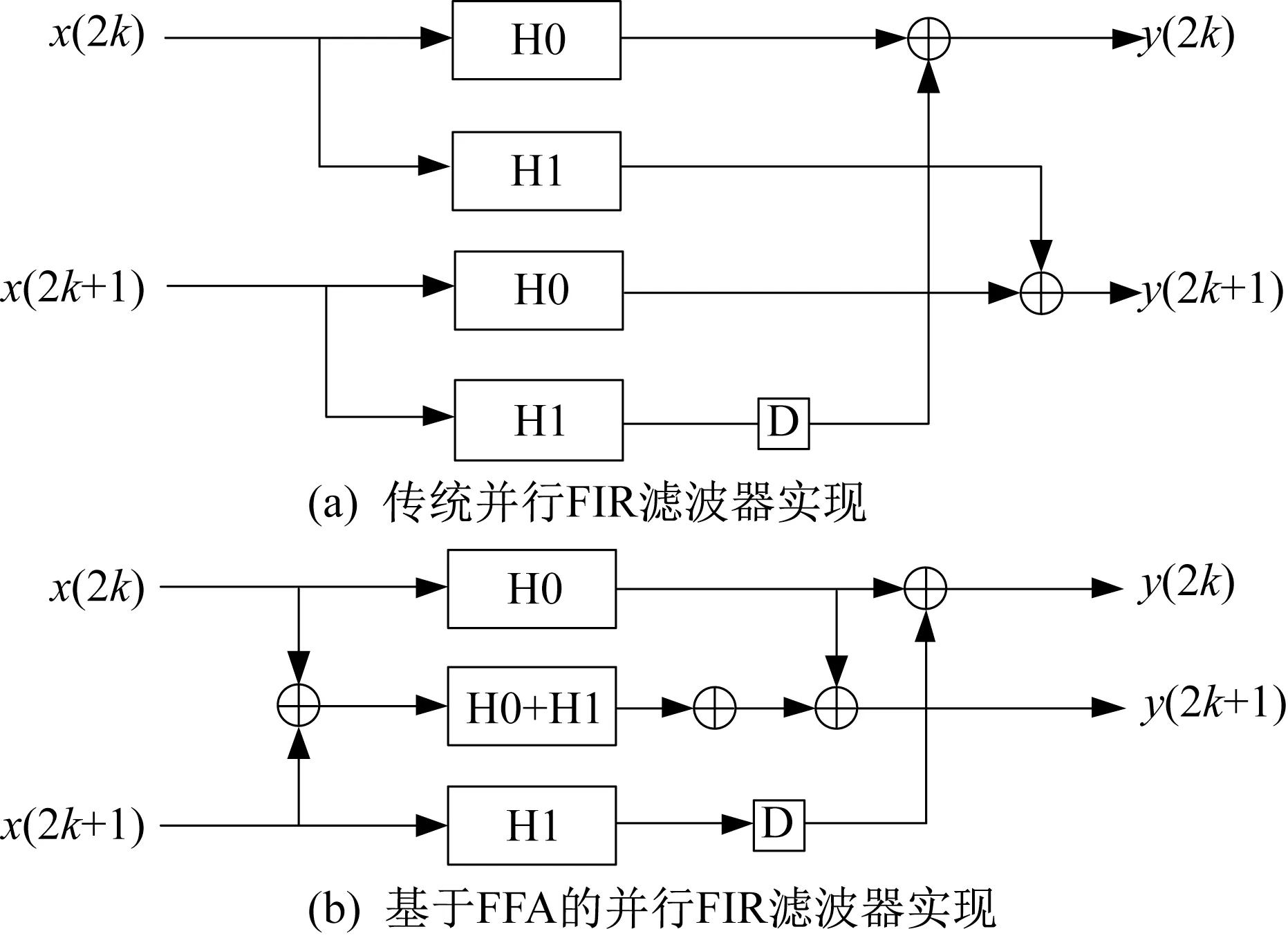

快速FIR算法(FFA)相较于传统的多相分解技术可以降低一部分资源消耗,缩减系统的算法强度,实现L路N阶的滤波器仅需(2N-N/L)个乘法器。例如,滤波器阶数N=4、并行路数L=2,传统并行方法需要8次乘法器,而二路并行快速滤波方法仅需要6次乘法,如图6所示。

图6 2种并行滤波器实现结构Fig.6 The implementation structures of two parallel FIR filters

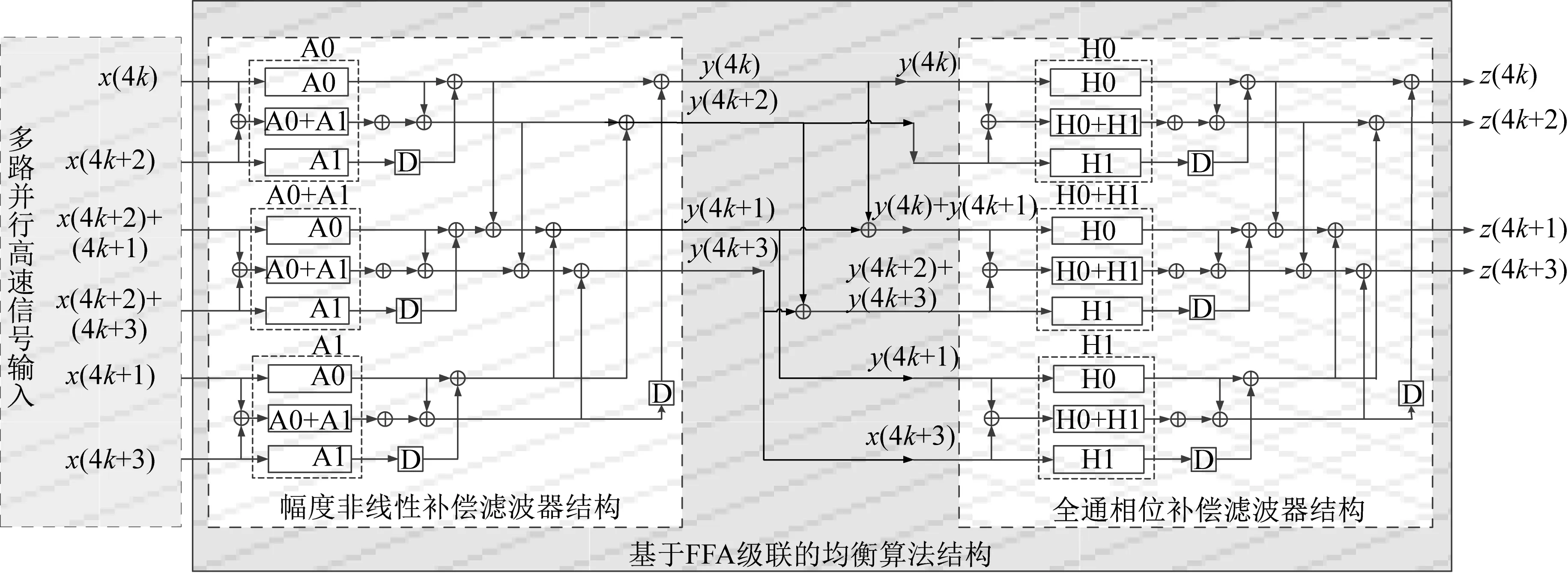

本文通过对FFA算法进行深入研究,对于小尺寸的并行滤波结构使用FFA算法,具有非常高的效率。但是,随着并行路数的增加,所需要的延时器的数量会越来越多[11]。为有效减少延时器数量,高效实现均衡算法,结合高分辨雷达成像模拟系统数字平台四路并行的特点,本文设计了基于FFA级联的均衡算法高效结构,使用2个二路并行FFA级联成需要的四路并行结构,然后将幅度非线性补偿滤波器和全通相位补偿滤波器2个结构前后串联,组成高效均衡滤波结构,如图7所示。

图7 基于FFA级联的均衡算法结构Fig.7 The structure of equalization algorithm based on cascade FFA

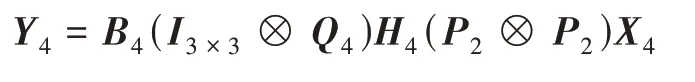

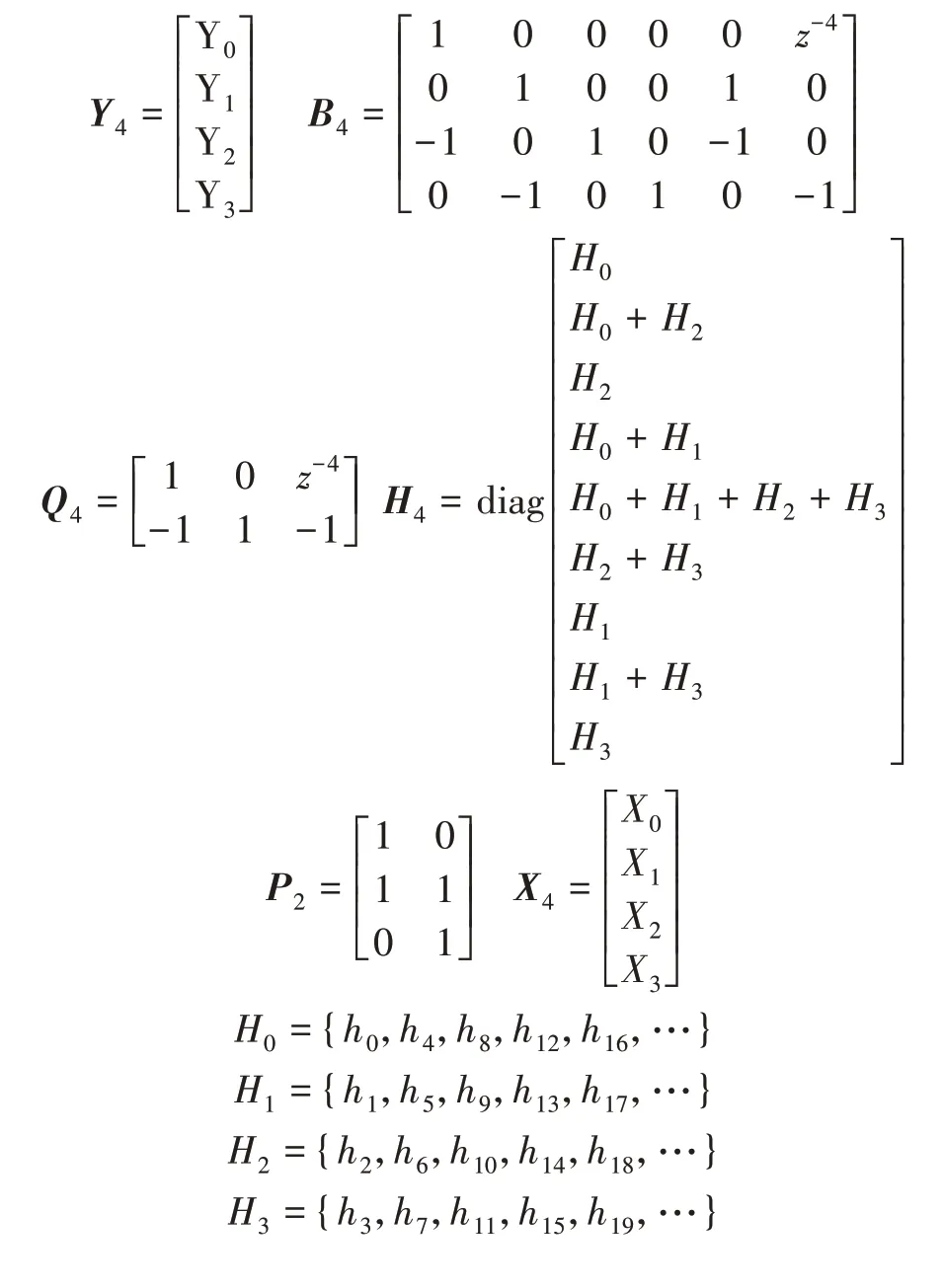

二路并行FFA 级联可组成四路并行滤波器结构。四路并行结构需要9 个长度为N/4 的滤波算法,均衡滤波器由一个四路并行幅度补偿滤波器和一个四路并行相位补偿滤波器级联组成,总需18N/4 个乘法器。降低复杂度的四路并行FIR 滤波器用矩阵形式表示如下:

其中

3 仿真与实验验证

3.1 系统幅相特性验证

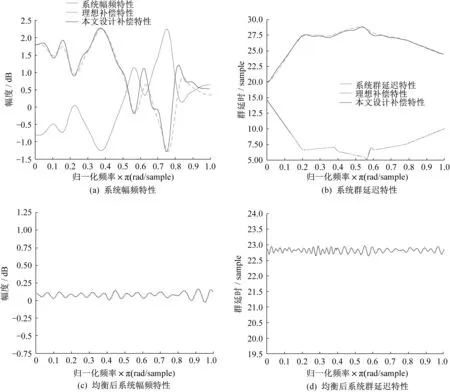

本文采用已有的带宽为2 GHz高分辨雷达成像模拟系统来验证所设计的非线性失真均衡算法,通过测试手段已获得系统3 个通道的幅相非线性失真参数,其中通道1 的幅度及群时延特性曲线如图8所示。根据测得的曲线进行相应的均衡滤波器设计,得到理想的补偿滤波器曲线,如图8所示(长虚线),本文所采用的四路并行全通均衡滤波器实现结构,对于N=128 阶滤波器而言,所需乘法器个数为576 个,而传统方法需要1024 个,节约了43.75%的乘法器资源。设计的均衡滤波器幅相特性如图8所示(实线)。

本文设计滤波器的幅频响应如图8(a)(实线)所示,与理论幅频曲线误差(图8(a),长虚线)比较,其误差如图8(c)所示,两者拟合度较高,收敛度较好,剩余幅值波动范围小于0.1 dB,相比于均衡前带内幅度最大波动4 dB,通带内波动改善了3.9 dB。本文设计的滤波器的群延迟响应如图8(b)(实线)所示,与理论幅频曲线误差(图8(b),长虚线)比较,有效带宽内的群时延波动小于2 ns,低于一个系统量化采样的周期,说明系统通道的非线性相位失真得到了有效的均衡校正。

图8 均衡前后系统幅相特性Fig.8 The amplitude and phase characteristic before and after equalization

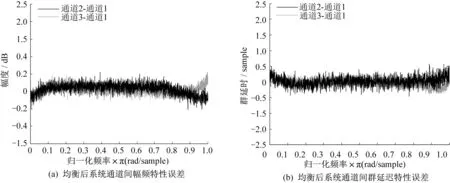

以通道1为参考通道,将另外2个通道间的幅度与群延迟曲线与参考做差得到相对误差曲线。通道间的幅度波动低于0.4 dB,群时延波动低于1 个采样周期,满足技术指标,如图9所示。

图9 均衡后通道间幅相特性误差Fig.9 The error of amplitude and phased characteristic between channels after equalization

3.2 高分辨成像效果验证

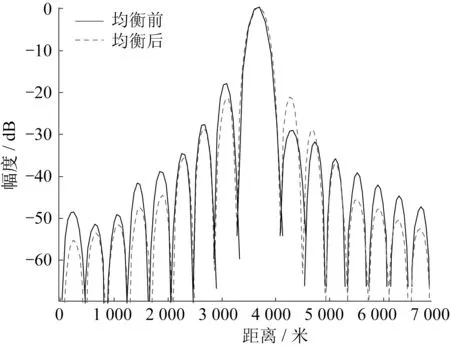

对均衡后高分辨成像模拟系统的成像效果进行验证,通过系统校准链路采集闭环回波数据进行脉冲压缩处理,得出脉压波形如图10所示。可以看出系统经过均衡之后,由三次相位误差引起的旁瓣不对称有所改善,峰值旁瓣比抬升,远端旁瓣降低,积分旁瓣比降低。

图10 均衡前后信号脉压结果对比Fig.10 Comparison of pulse compression results before and after equalization

4 总 结

本文针对高分辨雷达成像模拟系统中出现的幅相非线性失真问题,提出了基于数字调制的均衡方法,并分析了该算法在宽带数字域的实现结构,提出了基于FFA 的级联滤波器的FPGA 高效实现结构。与传统阵列补偿方法对比,实现四路128 阶均衡器,本文的方法需要576个乘法器资源,而传统方法需要1024个,节约了43.75%的乘法器资源。最后通过补偿前后幅相效果以及高分辨脉压波形的对比,验证了本文并行均衡算法的高效性。本文算法具有通用性,可广泛应用于包含数字信号处理平台的高分辨雷达成像模拟系统中。