一种基于ZYNQ的视频采集处理系统

2022-11-25魏洪健徐琦琳孙科学

魏洪健,徐琦琳,张 瑛,孙科学,2*

(1.南京邮电大学 电子与光学工程学院,江苏 南京 210023;2.射频集成与微组装技术国家地方联合工程实验室,江苏 南京 210023)

0 引 言

实时视频处理技术在工业生产、缺陷检测、自动驾驶等领域有不可替代的作用,同时各个领域也对图像处理带宽、实时性及清晰度有了更高的要求。以往的基于ARM(Advanced RISC Machine)数字图像处理系统[1-2]虽然能满足复杂的图像处理需求,但因为其处理器取样率低,难以得到带宽及实时性的保障。而基于DSP(Digital Signal Processing)的处理框架[3]能满足高实时性的需求,但在开发高复杂度的集成系统时周期长,且系统并行度低。在目标识别、机器验布、流水线产品缺陷检测等领域[4-6],图像处理系统需要采集产品实时的高清画面,并且同步处理视频特征信息,图像的有效信息通常只会存在1~2帧,这就要求系统要具有极高的实时性。此外对不同产品检测时算法的选择也不同,这便要求处理系统不仅需要具有高实时性的特点,也要具有一定的灵活性。而ARM+FPGA(Field Programmable Gate Array)的异构处理框架可以很好地兼顾两者。FPGA在处理高带宽视频数据时能充分展现其强大的并行计算能力[7],对已经相对成熟的图像预处理算法可以用Verilog HDL硬件描述语言来实现硬件的加速。因此以FPGA来实现数字图像处理算法,用ARM进行控制的系统框架可以满足对视频处理有较高实时性需求的领域。

该文设计了一种基于Xilinx公司推出的ZYNQ系列ARM+FPGA异构结构作为处理核心的视频数据实时采集、处理、控制、输出的框架,可支持高清1 280×720分辨率下60帧的实时处理。结合了双核ARMCortex-A9处理器强大的驱动能力、高灵活性、可配置性与FPGA并行、高速、再编程的特点,实现了软硬均可重复编程的结构。基于Verilog HDL硬件描述语言实现了图像的均值模糊,中值滤波,高斯模糊、边缘特征锐化、二值化、色彩空间转化、sobel边缘检测、形态学腐蚀与膨胀等经典图像预处理算法,均采用流水处理的形式最大化处理速度来保障系统的实时性[8],并且可以通过上位机来实现不同预处理算法的组合与实时切换,所有算法均封装为IP核来增加算法的灵活性与可移植性。主要由软件处理系统PS(Processing System)端与硬件可编程逻辑PL(Programmable Logic)端的软硬协同方式进行工作。

1 系统整体框架

系统采用ZYNQ系列的XC7Z020-CLG400芯片作为主控,OV5640摄像头作为视频数据源,另外还包括一台支持HDMI高清接口的显示器。搭建了视频数据的输入、输出通路以及硬件算法模块,整体结构框图如图1所示。PL硬件部分负责完成视频输入、硬件算法设计、视频输出等部分。PS处理器部分实现对整个系统的控制,包括硬件初始化流程,本地网络初始化以及UDP网络数据的接收与判断,并且通过AXI4总线对图像处理算法模块进行控制。PL与PS通过AXI(Advanced eXtensible Interface)协议进行数据互通,实现软硬件的协同工作。

从视频数据采集并在系统中的传输处理直至显示角度,可将系统按功能划分为如下主要模块:

(1)视频数据采集模块:系统通过500万像素CMOS摄像头采集外界视频数据,输入至PL硬件部分完成数据采集。摄像头初始化由PL部分IIC时序控制器完成,在上电后2秒内即可完成初始化,正常输出视频流数据。

(2)视频输入模块:摄像头RAW数据传入后,通过Video in to AXI4StreamIP将数据格式转化为 AXI-stream格式进入demosaic模块,对视频色彩进行插值还原,同时将单个像素数据由RAW转化为RGB888格式,最后再经VDMA(Video Direct Memory Access)缓存至DDR3中,完成视频输入通路搭建。

(3)视频输出模块:首先通过AXI4Stream to Video out将图像数据按行从DDR存储器中读出,再经过硬件算法处理模块,对视频数据进行流水线式处理,实时输出处理后的视频数据,在经过HDMI编码器,将标准VGA时序协议视频编码为HDMI差分信号进行输出。

2 系统关键部分实现

2.1 摄像头初始化

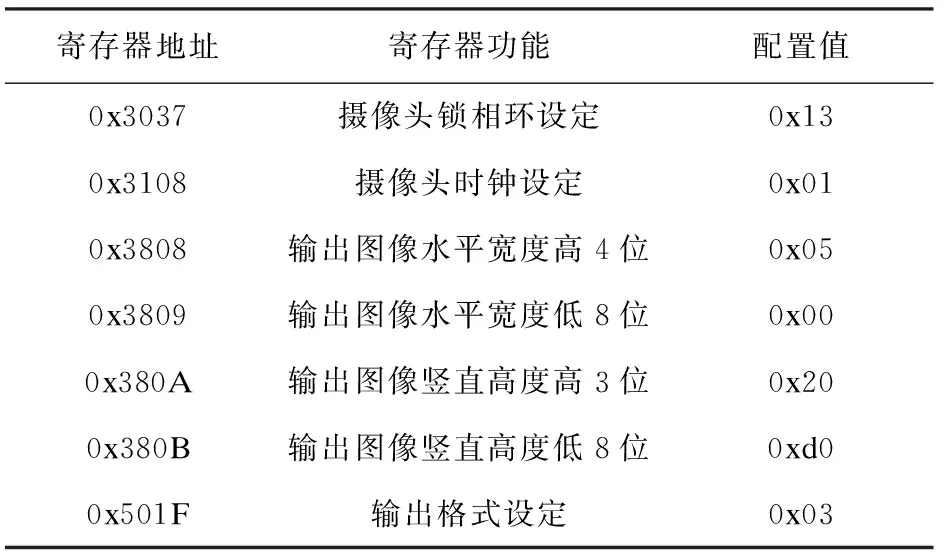

系统的图像源由OmniVision公司的OV5640摄像头进行采集,其拥有2 592×1 944(500万像素)的感光阵列,最大输出能达到QSXVGA(2 592×1 944)下的15帧输出,支持SCCB(Serial Camera Control Bus)协议控制。SCCB协议是一种向上兼容IIC协议的摄像头寄存器配置协议,在主机以单字节发送数据至从机时完全兼容IIC协议。系统选择了1 280×720(92万像素)下60 FPS格式的视频流输出。由硬件PL端完成IIC时序控制器对摄像头内部控制寄存器以单字节写的格式进行初始化设置,表1列出了部分关键寄存器地址、功能及配置值。系统总共对OV5640内部寄存器进行253次SCCB读写配置。

表1 OV5640部分关键寄存器配置

输出图像的水平宽度为0x0500为1 280,竖直高度为0x02d0为720,即设定为1 280×720的输出分辨率。此时可计算出输出像素的时钟为1 650×750×60=74.25 MHz。

2.2 摄像头数据Demosaic

CMOS摄像头是由覆盖在硅衬底上的滤色片测量不同波长的光强度来采集图像数据,且每种滤色片只能对应一种颜色,即每个像素原始数据只包含一种颜色信息,要通过临近像素的可用信息来还原出原像素的三种颜色分量,而人眼对绿色的敏感度最高,因此往往CFA(Color Filter Array)阵列由1/2的绿色分量与1/4的红色与蓝色分量组成,bayer阵列共有四种排列模式,如图2所示。

从CMOS摄像头输出的RAW格式的数据,通过Video in to AXI4Steam转化为AXI-stream格式的数据进入Sensor Demosaic电路,利用5×5矩阵通过色度方差来抑制在还原像素时产生的颜色混叠效应,提升传感器输出图像色彩质量。同时由于CMOS摄像头OV5640数据输出引脚只有10位,实际上摄像头的输出为每2个pix clock输出一个RGB565格式的像素数据,Sensor Demosaic同时也对按字节接收到的RAW数据进行格式重构,转换RAW格式为24 bit的RGB888格式。Sensor Demosaic偏移地址0x28寄存器[1:0]的值对应了全部四种bayer阵列格式。可以在PS端通过AXI总线来设定像素的阵列模式,色彩还原后仍然以AXI4-Stream格式输出到DDR中进行视频缓存。

2.3 图像处理IP封装

图像卷积运算作为图像预处理中应用最广泛的方式,由FPGA实现流水线运算时,能达到最高的实时性[9],这是因为FPGA在处理图像进行运算时以行为单位,而CPU、GPU、DSP在处理时是以帧为单位。如图3(左)所示,图像的传输是从左上角的第一个像素开始,向右输出1整行1 280个像素点后,向下移动一行开始传输第二行的像素数据,直至720行扫描结束后完成整帧的输出。通过ShiftRegister缓存图像的前两行数据,同时接受当前数据作为第三行,就实现了三行数据的同时缓存。每个时钟的上升沿到来时,ShiftRegister中每个数据会向后移动一位,移位寄存器将最后一个数据作为当前的输出。图3(右)结构中ROW1~3即为当前的三行像素数据输出,通过对三行数据的一个缓存打拍处理,就可得到图3(左)中原图像左上角像素的3×3矩阵窗口,此时每经过一个时钟周期,就相当于该3×3矩阵窗口在像素阵列中向右移动一格,即实现步长为1的图像卷积运算。

得到图像的3×3像素矩阵后,通过与不同的卷积模板进行运算后再替换原像素点数据,如此遍历整幅图像之后即可实现图像的滤波操作。常见的处理有用9个数据平均值代替原像素点值的均值滤波;用9个值中的中值来代替原像素点的中值滤波。

以sobel边缘检测[10]为例,其原理是根据像素灰度值与其周围的离散差值来近似计算出该点不同方向上的梯度。根据式(1)求出原像素矩阵I与两个3×3核的卷积结果水平积分因子Gx与竖直积分因子Gy,再通过式(2)求出近似梯度G,判断G与边界阈值S大小即可判断出该点是否为边缘点。

(1)

(2)

(3)

为验证硬件算法的实时性,通过Vivado与Modelsim进行联合仿真,编写测试文件模拟VGA时序驱动,每帧读取不同的图片,经过硬件处理后再保存为新的图片,共进行三帧的仿真即处理三张不同的图片,第四帧开始时结束仿真。结果表明,所述设计能满足视频处理实时性的要求。

2.4 硬件算法模块实现

现代数字图像处理的模型一般分为多级的形式,由视频采集前端、图像预处理以及图像信息提取三个部分构成。其中视频采集前端往往是由采集端对原生图像数据进行最基本的处理,不会对原始图像数据的信息特征产生较大影响。本系统中OV5640摄像头内部已集成了ISP图像信号处理单元,其中包括AEC(自动曝光控制)、AWB(自动白平衡)、gamma矫正、BLC(黑电平矫正)等图像补偿功能。

该系统针对图像预处理以及图像信息提取给出了不同的方案,读者可根据实际情况选择或者增删图像处理模块。系统硬件算法内部结构如图4所示,其中图像处理算法包括三种预处理滤波、边缘检测以及基于拉普拉斯算子的图像边缘增强、图像形态学腐蚀与膨胀。均采用PL端硬件流水的形式完成图像处理,封装为通用视频接口的IP核,保证了系统的可扩展性与灵活性。视频选择器为封装了AXI接口的数据接收自订IP核,接收PS端的控制,可从输入的视频数据中选择一路输出。PS端通过对视频选择器的控制即可实时调整系统硬件算法的组合。

2.5 PS端实现

PS软件部分[11]主要实现的内容包括开启DDR视频缓存通道[12],初始化硬件算法模块,设置开发板IP地址以及对UDP网络数据的处理。SDK中处理的流程框图如图5所示。系统上电后,首先PS端将通过AXI总线对硬件算法模块中的3个视频选择器进行初始化配置,设置其默认输出原始视频数据。随后通过AXI总线向PL端的IIC时序控制器发送启动信号,开始对OV5640摄像头内部寄存器进行配置,共发送253个SCCB协议数据。PL端寄存器配置数据完成后,硬件端通过ZYNQ中IRQ_F2P接口发送硬件的中断信号。IRQ_F2P为ZYNQ提供的硬件中断接口,硬件中断号ID有[91:84],[68:61]共16个,可以设置边沿触发或电平触发,本系统中使用上升边沿触发模式进入中断处理函数。通过硬件中断功能软件端可以在硬件信号触发后最快地做出响应,即最优先处理中断处理函数中的程序部分。中断处理函数中包括PS端对PL端VDMA进行初始化配置。 视频数据的DDR读写地址为0x01100000,缓存三张图像。则从0x01100000开始的1 280×720×3个地址内会按BGR顺序存放第一帧的图像数据,从地址0x013A3000(0x01100000+1 280×720×3)开始会存放第二帧数据,以此类推。

物联网技术已被广泛应用在SOC领域,本系统基于RTL8211E千兆路由芯片[13-14],PS端部署lwip(light weight IP)轻量化IP协议实现网络通信。通过UDP协议完成与上位机的数据交互,实现对系统的远程控制。PS端不断读取上位机发送的UDP网络数据包,根据网络指令通过AXI总线协议对图4中的3个视频选择器的输出进行切换,也可以改变二值化阈值与sobel边缘检测阈值。

3 测试结果与分析

在vivado平台与modelsim仿真器完成系统的设计与仿真后,进行工程的综合、实现、生成比特流文件,导出hardware进入SDK环境进行ps端程序开发。完成后创建FSBL(First Stage Boot Loader)工程对SDK中C程序进行固化。

开启系统等待初始化流程结束后显示器通过HDMI线接收来自系统的1 280×720分辨率下60帧视频数据,图6为在正光源照射下的书本文字显示结果,其中左上至右下依次为原图(a)、高斯滤波(b)、图像锐化(c)、sobel边缘检测(d)、中值滤波+sobel边缘检测(e)、中值滤波+sobel边缘检测+图像腐蚀(f)的处理效果图。

图7为拍摄带有浮雕表面二维码图像的处理结果,其中左上至右下依次为原图(a)、图像锐化(b)、sobel边缘检测(c)、高斯滤波+sobel边缘检测(d)、高斯滤波+sobel边缘检测+图像腐蚀(e)、二值化显示(f)的处理结果。

上述两种不同物体的实时图像采集结果很好地证明了所述系统功能完备性以及算法有效性,通过不同的算法组合最终均可获得较好的图像特征信息,并且能直观地观察到每个中间级算法处理的结果。

以硬件流水线实现图像处理算法时,其延时是可以计算出的[15]。该文所述设计中,处理算法使用的3×3缓存矩阵会使图像同步时钟延迟一行来进行数据同步,1 280 p分辨率下则会延迟1 560个延时,后续则在进行不同流水线算法时处理所用的延时不同。表2中给出了该系统中通过硬件算法与在ZYNQ芯片中ARM端调用OpenCV库[16]处理一帧图像的延时对比。

表2 不同算法处理延迟时间

对比软硬件在图像处理速度上的差异,该系统在进行各种图像的处理时均有更快的速度,且实现的算法复杂度越高,则硬件流水处理的提升越大。

4 结束语

该文提出并实现了一种基于ZYNQ-7020芯片的视频实时采集、处理、显示平台,充分结合了ARM的灵活性与FPGA在图像处理领域的高实时性。平台集成了多种经典的图像预处理算法,延时低、易于替换与扩展,为复杂图像处理算法实现提供良好的基础平台。经测试所述系统实时性高、性能稳定,可应用于动态捕捉、缺陷检测、视频前端处理等领域。