加速Flash 系列FPGA 芯片功能验证方法

2022-10-12丛红艳张艳飞

胡 凯,丛红艳,闫 华,张艳飞,李 涌

(1.中科芯集成电路有限公司,江苏无锡 214072;2.中微亿芯有限公司,江苏无锡 214072)

1 引言

现场可编程门阵列(FPGA)芯片集成资源的数量和设计的复杂性日渐提高,研发周期和面市时间的压力使实现验证的完整性和高效性受到挑战。为了验证整个FPGA 芯片逻辑功能的正确性,必须做大量的验证工作,验证工作量已经占到芯片整个研制流程工作量的60%~80%[1-3]。Flash 系列FPGA 芯片集成了基本功能模块(VERSATILE)、系统配置模块(CFG)、静态随机存取存储器(SRAM)、时钟管理模块(CCC)、输入输出模块(IO)等。在Flash 系列FPGA 芯片验证中(也称为FPGA 芯片的系统级验证),验证重点及难点主要集中在验证芯片集成的正确性及配置过程和全局信号的连线的正确性。

FPGA 芯片系统级验证侧重于不同子系统之间的信号交互以及实现不同验证场景的验证用例,为了提高验证覆盖率,验证对象需要包含大量的验证用例,所消耗的验证时间很长,而配置下载时间即下载位流文件约占整个验证时间的2/3,因此,如何对Flash 系列FPGA 芯片设计中的复杂验证对象进行验证、提高验证功能覆盖率已经成为缩短总体产品验证时间所面对的挑战。为了加快仿真速度,提高验证效率,本文提出了一种加速Flash 系列FPGA 芯片的系统级验证方法。

2 传统Flash 系列FPGA 功能仿真验证方案

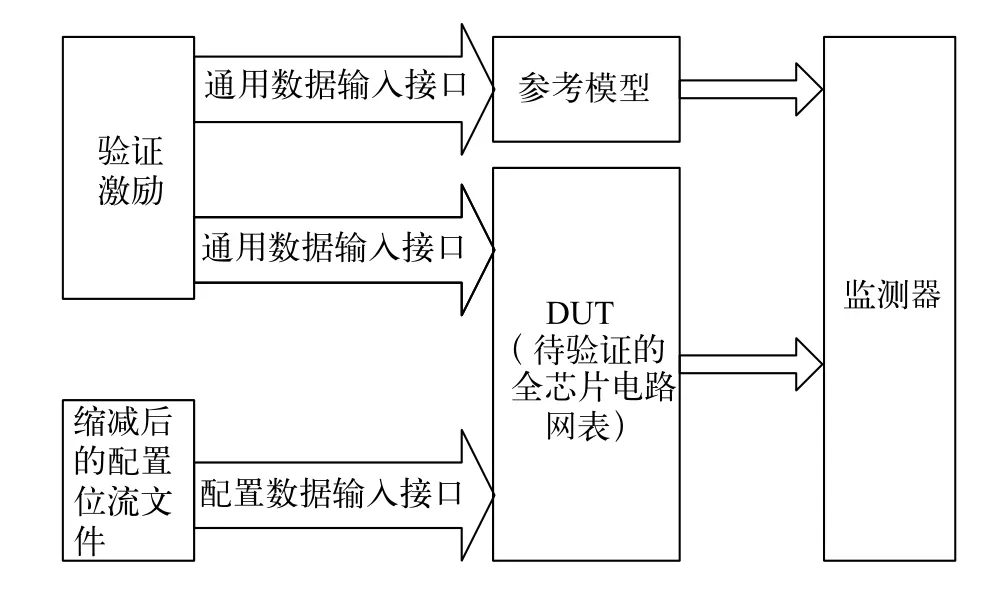

全芯片验证平台如图1 所示,其主要包括验证激励、缩减后的配置位流文件、被测电路(DUT)、参考模型和监测器,DUT 为待验证的全芯片电路网表,缩减后的配置位流文件通过DUT 的配置数据输入接口输入到DUT 中,将相对应的验证激励通过DUT 的通用数据输入接口输入到DUT 中,同时验证激励通过DUT 的通用数据输入接口输入到参考模型,利用监测器监测DUT 的输出是否与参考模型的期望值一致[4-6]。采用此方法的优点是验证对象为全芯片电路,模块功能简单且占用配置位流帧数较少的验证用例,可以显著降低验证时间,提高验证效率。但是对于全芯片电路功能复杂、占用配置位流帧数较多的验证用例,采用此方法不能有效提高验证效率,验证时间依然很长。

图1 全芯片验证平台

3 加速Flash 系列FPGA 芯片系统验证方法

FPGA 芯片中的逻辑资源排布结构及其帧分布如图2 所示,FPGA 芯片中的逻辑资源主要包括VERSATILE 和互连线资源。配置位流的第1 帧对应芯片顶部的第1 行电路,最后1 帧对应芯片底部最后1 行电路,完成第1 帧到最后1 帧的全部配置码流的下载耗时较长。在2U 服务器,即1 TB 内存、Intel(R)Xeon(R) Gold 6254 CPU@3.10 GHz,万兆网络硬盘,10 TB 存储容量条件下,采用1 个简单的移位寄存器完成全部配置位流下载,需要7~8 d 时间,如果验证用例包含的芯片资源较多,那么仿真验证的时间会更长。

图2 FPGA 芯片中的逻辑资源排布结构及其帧分布

某一验证用例需要的逻辑资源为第M~N 帧,位流截取方法是将第M 帧作为配置寄存器字段的第1 帧,将第N 帧作为配置寄存器字段的最后1 帧,第M~N帧的数据即是需要配置寄存器的字段,删除配置寄存器字段的第1~M-1 帧以及第N+1 帧至最后1 帧,得到所需要的配置位流文件,这样就可以根据验证对象是芯片电路的某些区域来选择配置位流文件大小,大大缩短仿真验证时间[7-8]。对于覆盖率驱动验证,所用资源较多的、位流文件较大的验证用例,采用该方法的缺点是不能有效提高验证效率,仿真耗时仍然很大[9]。

通过解析配置位流文件可以得出配置位流与芯片电路之间的映射关系,即字/位线(WL/BL)分布规律,解析并使用脚本实现比特流的规律提取,该方法针对单个验证用例解析配置位流文件,可以有效缩短仿真时间,提高仿真效率,使得FPGA 全芯片集成验证的配置时间大大缩短。针对FPGA 全芯片集成验证时的大量验证用例,该方法通过维护一个特征参数库、利用触发参数触发每个验证用例进行仿真验证,可以减少人工重复作业时间,实现仿真环境自动化。

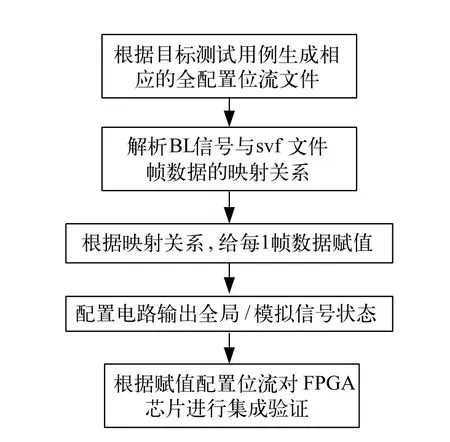

以某一款Flash 系列FPGA 芯片为例,1 帧配置码流共计2912 bit 配置数据,对应数据移位寄存器(DSR)电路的每1 BL 输出位,在不了解全芯片Flash单元的WL/BL 坐标的情况下,以帧为单位,每打开1个WL,就赋值相应的2912 个DSR 电路的BL 输出位。这种方法相当于逐帧赋值配置码流,统计DSR 电路的所有BL 输出信号与2912 位配置码流的每一位对应关系,通过脚本实现每1 帧的赋初值操作,大大减少了下载和配置位流数据的时间,因此可以有效缩短仿真验证时间,提高仿真验证效率,缩短了FPGA 全芯片系统级验证时间。具体流程如图3 所示:(1)梳理DSR 电路所有BL 信号的位线顺序,即电路BL 信号与svf 文件帧数据的映射关系;(2)根据svf 文件帧数据与电路BL 信号映射关系编写脚本,实现赋值每1帧数据的功能;(3)梳理CFG、地址移位寄存器(ASR)、DSR 均属于配置电路的一部分输出信号类型,根据ASR、DSR、CFG 与其他电路之间的互连关系,将互连信号分为WL 信号、BL 信号、全局信号、控制信号(如BL 中继控制信号、IO 初始化配置信号)等;(4)根据配置电路输出信号分类,对相应信号做配置,完成前后2 种状态的赋初值,模拟配置完成前后的信号状态,保证芯片除配置电路以外的部分实现正常的功能;(5)完成上述关系梳理及脚本编写后,通过全芯片验证环境调试,根据赋值的配置位流对FPGA 进行集成功能验证。

图3 目标验证用例的流程

4 仿真验证结果

用面向对象的验证语言System Verilog,建立Verilog+CDL 的混合验证环境(协同仿真环境)。采用Synopsys 公司的VCS 的仿真工具设计仿真验证[10]。

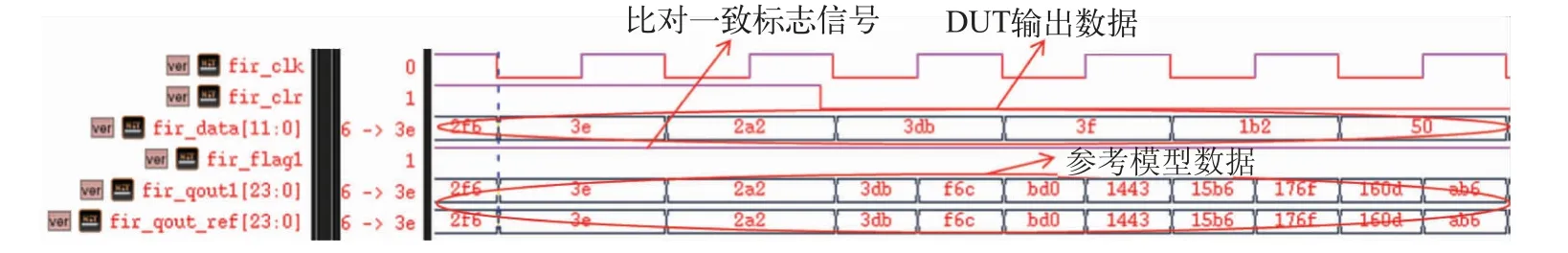

1)单个应用61 阶有限脉冲响应(FIR)滤波器,位流截取方法与配置位流文件的解析方法验证结果如图4 所示,DUT 输出与参考模型输出结果一致,功能验证正确。

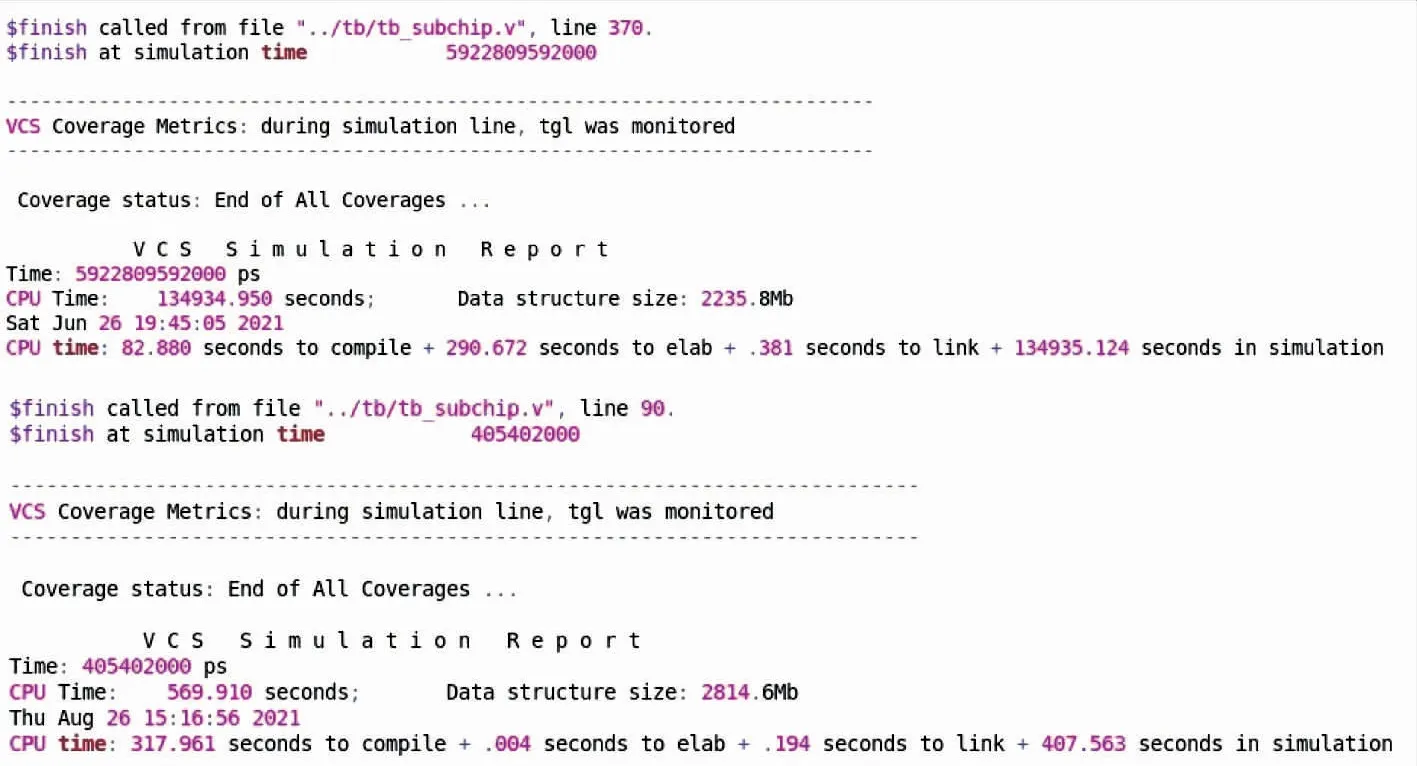

2)单个应用61 阶FIR 滤波器用例仿真运行结果和时间如图5 所示,采用位流截取方法验证FIR 滤波器的时间约为37.58 h,而采用配置位流文件的解析方法验证FIR 滤波器的时间为725.72 s,大大缩短了验证时间。

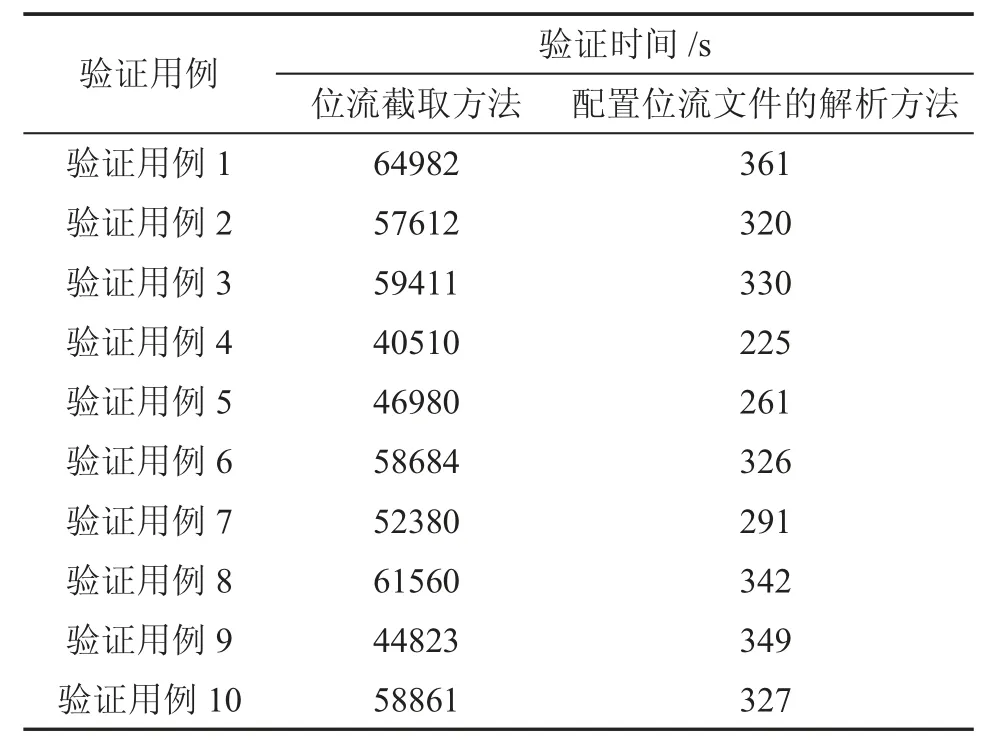

3)在2U 服务器条件下,多个用例验证仿真时间结果如表1 所示。从表1 可以看出,基于覆盖率驱动的验证,在需要运行多个功能复杂的用例条件下,配置位流文件的解析方法是位流截取方法速度的180~200倍,大大提高了验证效率。

图4 位流截取方法与赋值配置位流文件的解析方法功能验证结果

图5 单个用例位流截取方法与配置位流文件的解析方法运行时间比较

表1 多个用例验证时间比较

5 结论

本文对Flash 系列FPGA 芯片集成验证方法进行了研究,针对所用资源多、功能复杂的验证用例位流截取方法验证周期长、验证效率低的问题,提出了使用配置位流文件的解析方法,该验证方法可以根据验证用例需求,赋值相应的配置位流,减少下载和配置位流数据的时间,从而大大减少仿真时间,提高验证效率,最大限度提高验证电路的覆盖率,满足大规模电路功能仿真的需求。该方法已成功应用于Flash 系列FPGA 芯片电路功能验证工程实践中。