基于FPGA 的数据输出显示电路设计

2022-09-26廖超平

廖超平

(广西机电职业技术学院,广西 南宁 530007)

在非常多的数字系统的设计中存在数据输出显示模块,数据输出显示模块首先要将用二进制(BIT)码表示的计算结果转换成用户习惯使用的十进制(BCD)码,然后转换成整数部分第一位不为零的数字前的零不显示的大家习惯的输出形式,在通过显示器(通常是LCD 显示器)显示出来。在基于FPGA 设计数字系统时数据输出显示电路模块是经常使用的。基于FPGA 设计数字系统时数据输出显示电路在各种智能仪表、电子秤和数控机床等数字系统的设计中广泛使用。

1 数据输出显示电路设计方法原理分析

1.1 二进制-BCD 转换

数字系统使用的数据通常是二进制码,在输出前要转为BCD 码。二进制-BCD 转换电路利用加3 或0再移位方法进行,详细原理请参考文献[1]。

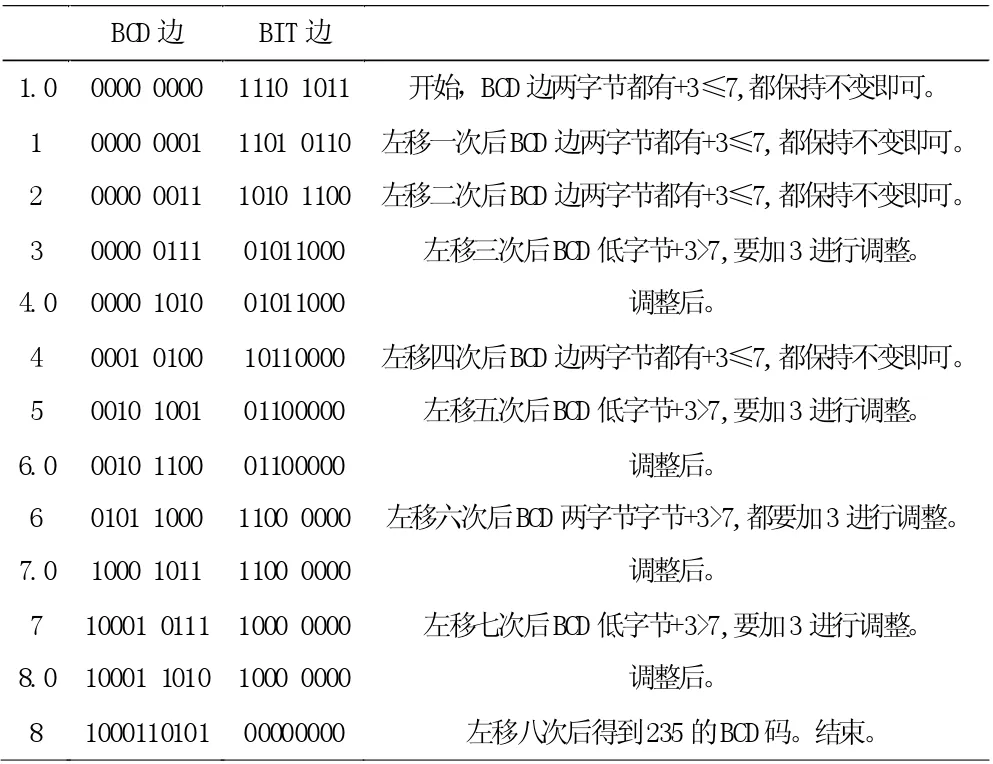

下面举例说明。假如有一个八位二进制数1110 1011(十进制数235),要把它转成十进制数的BCD 码[2]:

在上面处理过程中,每次移位前,先判断BCD 边的每个字节特点,若是(0,0,0,0)-(0,1,0,0)这几个值时,即+3≤7,向左边移动一位后,没有对高一位的进位,而且本位最大也符合十进制的表达形式,故这字节加0,即保持不变即可。

如这个BCD 边字节是(0,1,0,1)-(1,0,0,1)这几个值时,即+3>7,向左边移动一位后,最少也存在对高一位的进位,进位是逢十进一,所以要进行修正。修正的方法就是加3 后再移位。

上面分加3 或0 移位两种情况,原因是为了保证下一次移位后,符合十进制数进位和十进制数的表达形式,即每位十进制数码应该只能是:0-9 这十个数码。

BCD 边 BIT 边1.0 0000 0000 1110 1011 开始,BCD 边两字节都有+3≤7,都保持不变即可。1 0000 0001 1101 0110 左移一次后BCD 边两字节都有+3≤7,都保持不变即可。2 0000 0011 1010 1100 左移二次后BCD 边两字节都有+3≤7,都保持不变即可。3 0000 0111 01011000 左移三次后BCD 低字节+3>7,要加3 进行调整。4.0 0000 1010 01011000 调整后。4 0001 0100 10110000 左移四次后BCD 边两字节都有+3≤7,都保持不变即可。5 0010 1001 01100000 左移五次后BCD 低字节+3>7,要加3 进行调整。6.0 0010 1100 01100000 调整后。6 0101 1000 1100 0000 左移六次后BCD 两字节字节+3>7,都要加3 进行调整。7.0 1000 1011 1100 0000 调整后。7 10001 0111 1000 0000 左移七次后BCD 低字节+3>7,要加3 进行调整。8.0 10001 1010 1000 0000 调整后。8 1000110101 00000000 左移八次后得到235 的BCD码。结束。

1.2 数据的译码

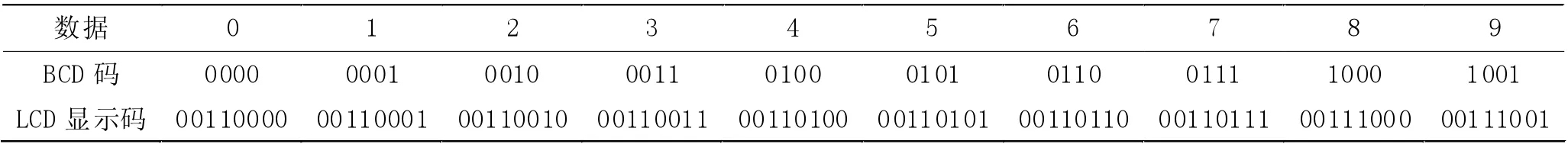

数字和字母要用LCD 显示器显示出来,要译码成LCD 显示器显示的数据格式,数字0-9 的1602LCD数据译码表如下:

所以,要输出的数字要先转换为BCD 码,再在其前面加上"0011"。如D0 (7 downto 0)<= "0011" &DIN(3 downto 0)。

对于字母则要详细查找1602LCD 数据译码表,这里省略。

数据 0 1 2 3 4 5 6 7 8 9 BCD 码 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 LCD 显示码 00110000 00110001 00110010 00110011 00110100 00110101 00110110 00110111 00111000 00111001

1.3 LCD 控制电路设计方法原理

要用LCD 显示的数据主要有数字和字母;有一经显示就不变的静态显示,有需要不断刷新的动态显示。另外,LCD 控制电路通常有两种设计方法,一是状态机方法,二是计数器方法。

综合考虑以上LCD 显示的数据的特点,我们采用对有可能显示数字和字母的LCD 显示范围采用重复扫描的方式显示数据,对不变的静态显示采用每次刷新都重复显示同样的数据,而变化的动态显示则每次刷新时及时更新显示数据。对于扫描的控制,这里采用计数器方法,因此方法具有直观、容易迁移到别的设计的特点。

LCD 控制过程分为初始化阶段和循环扫描两行输出阶段。

(1)1602LCD 的一般初始化过程

启动电源

等待30mS;

写指令3CH(不检测忙信号);

以后每次写指令、读/写数据操作均需要检测忙信号或有足够延时;

写指令3CH:显示模式设置;

写指令01H:显示清屏;

写指令06H:显示光标移动设置;

写指令0CH:显示开及光标设置。

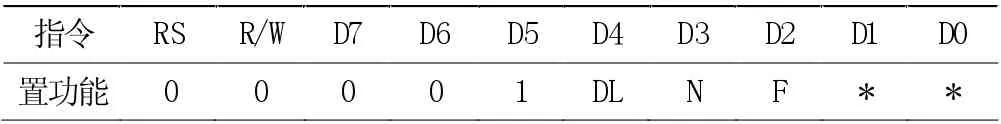

1602LCD 的一般初始化过程用到的指令如下:

显示模式设置:

指令 RS R/W D7 D6 D5 D4 D3 D2 D1 D0置功能 0 0 0 0 1 DL N F * *

DL:1-8 位数据接口、0-4 位数据接口;N:1-2 行显示、0-1 行显示;

F:1-5X10 字 体、0-5X7 字 体。当 数 据 位 为00111100 [0x3C]时,设置8 位数据接口,16×2 显示,5×10 点阵。

清显示:数据位为00000001 [0x01]

指令 RS R/W D7 D6 D5 D4 D3 D2 D1 D0清显示 0 0 0 0 0 0 0 0 0 1光标和显示模式设置:指令 RS R/W D7 D6 D5 D4 D3 D2 D1 D0置输入模式 0 0 0 0 0 0 0 1 I/D S I/D:光标移动方向,1-右移,0-左移;S:屏幕上所有文字是否左移或者右移。1-有效,0-无效。当数据位为00000110 [0x06]时,光标右移,整屏显示不移动。显示开关及光标设置:指令 RS R/W D7 D6 D5 D4 D3 D2 D1 D0显示开/关控制 0 0 0 0 0 0 1 D C B D:显示(1 有效);C:光标显示(1 有效),B:光标闪烁(1 有效)。当数据位为00001100 [0x0C]时,开显示和光标不显示,光标不闪烁。(2)循环扫描两行输出阶段两行循环扫描中则有三种情况:一是空白,此时输出空白符,指令如下。指令 RS R/W D7 D6 D5 D4 D3 D2 D1 D0写数据 1 0 0 0 1 0 0 0 0 0二是不变字符,此时直接输出所要求的字符如“i”。指令如下。指令 RS R/W D7 D6 D5 D4 D3 D2 D1 D0写数据 1 0 0 1 1 0 1 0 0 1三是输出变化的数字,例如输出频率的各位数字。这时输出由一个总线信号(例如D0(7 downto 0))赋予。指令 RS R/W D7 D6 D5 D4 D3 D2 D1 D0写数据 1 0 D0(7 downto 0)

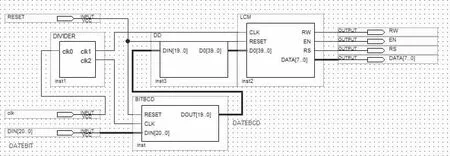

2 数据输出显示电路原理框图

原理框图,见图1。

图1 原理框图

基于FPGA 设计数字系统时数据输出显示电路主要包括三部分:首先是二进制-BCD 转换电路模块(BITBCD),此模块实现将用二进制(BIT)码表示的计算结果转换成十进制(BCD)码;其次是数据译码模块(DD),此模块实现将原始的十进制(BCD)码转换成用于LCD 显示的代码;最后是LCD 显示输出模块(LCM)模块。

3 各组成模块设计

3.1 二进制-BCD 转换电路模块(BITBCD)

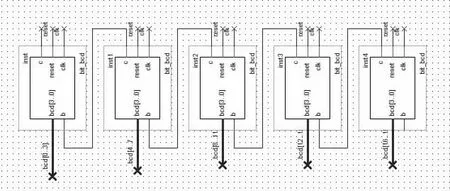

DIN[19..0]是20 位二进制的BIT 输入,clk 是移位时钟信号,RESET 为复位信号。它的内部包含有五个BIT-BCD 单元,见图2。

图2 五个BIT- BCD 单元

每个单元负责一位BIT、BCD 数码的移位和实施BIT- BCD 转换的加3 或加0 运算[1]。转换过程开始后,先复位,并行输入20 位二进制数的BIT 码。然后,在每次奇次时钟到来时五个单元各自进行加3 或加0,每次偶次时钟到来时实施移位。经过了40 个时钟,20 次移位和运算完成整个转换过程。

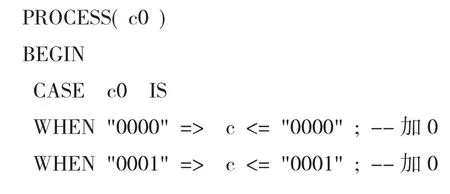

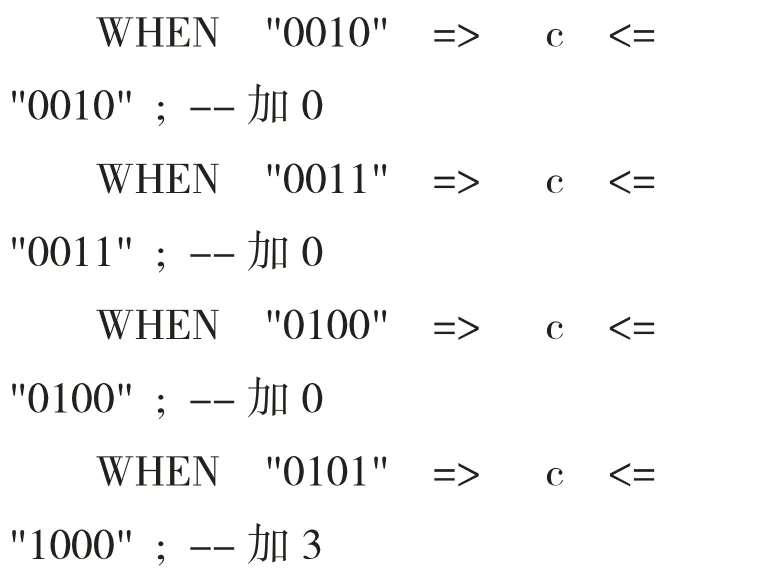

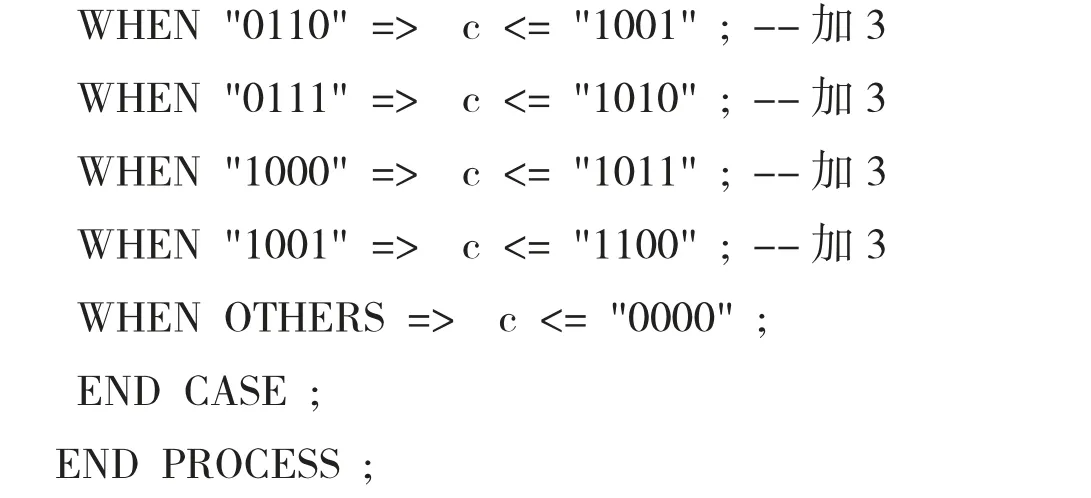

其中,BIT- BCD 单元的加3 或加0 进程VHDL代码如下[3]:

在上面例子的BCD 边的每个字节是(0,0,0,0)-(0,1,0,0)这几个值时,向左边移动一位后,没有对高一位的进位,而且本位最大也符合十进制的表达形式,故加0,即保持不变即可。

在 BCD 边的每个字节是(0,1,0,1)-(1,0,0,1)这几个值时,向左边移动一位后,最少也存在对高一位的进位,进位是逢十进一,所以要进行修正。修正的方法就是加3 后再移位。

以后每次移位都遵守同样的规律,移动20 次后,即完成转换过程。

3.2 数据译码模块(DD)

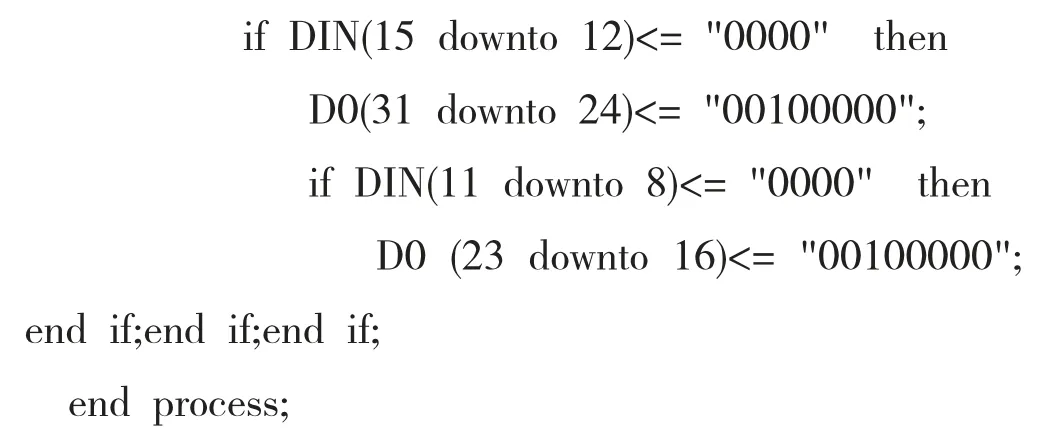

此模块将信号DIN (19 downto 0) 中的十进制(BCD) 码转换成用于LCD 显示的代码信号D0(39 downto 0),转换时要考虑整数部分第一位不为零的数字前的零不要显示。其主要VHDL 代码如下:

--整数部分第一位不为零的数字前的零不要显示。

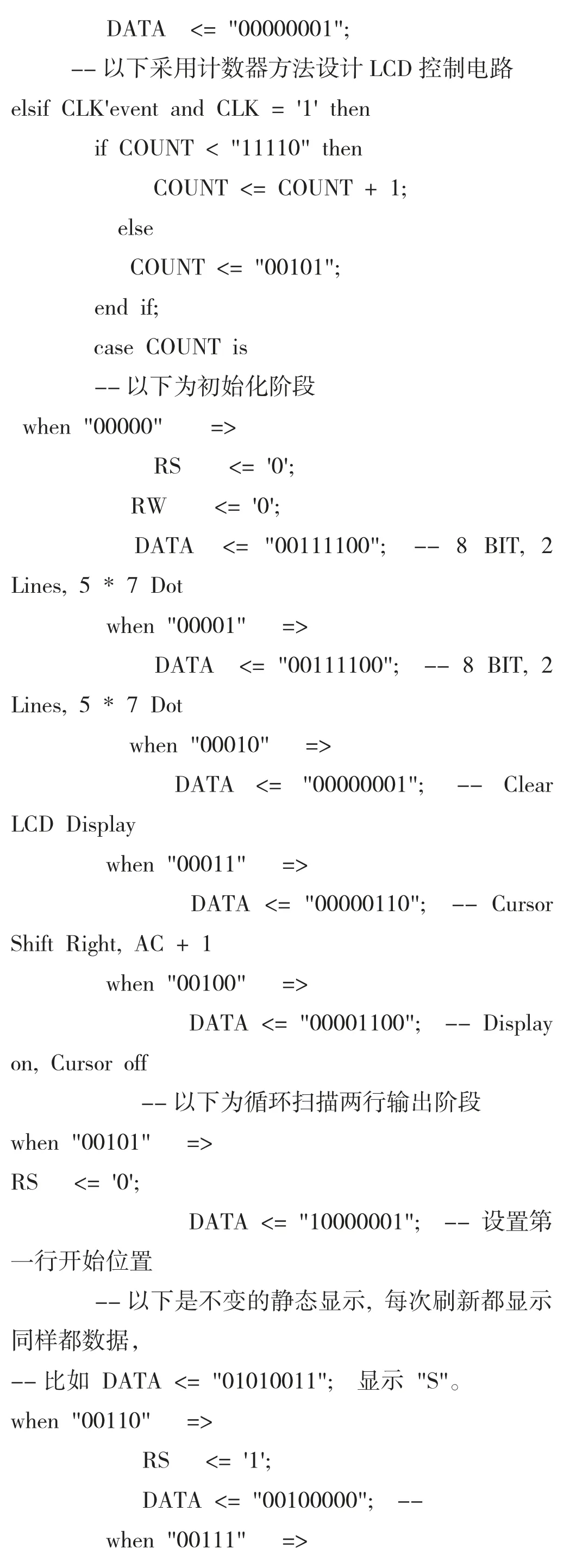

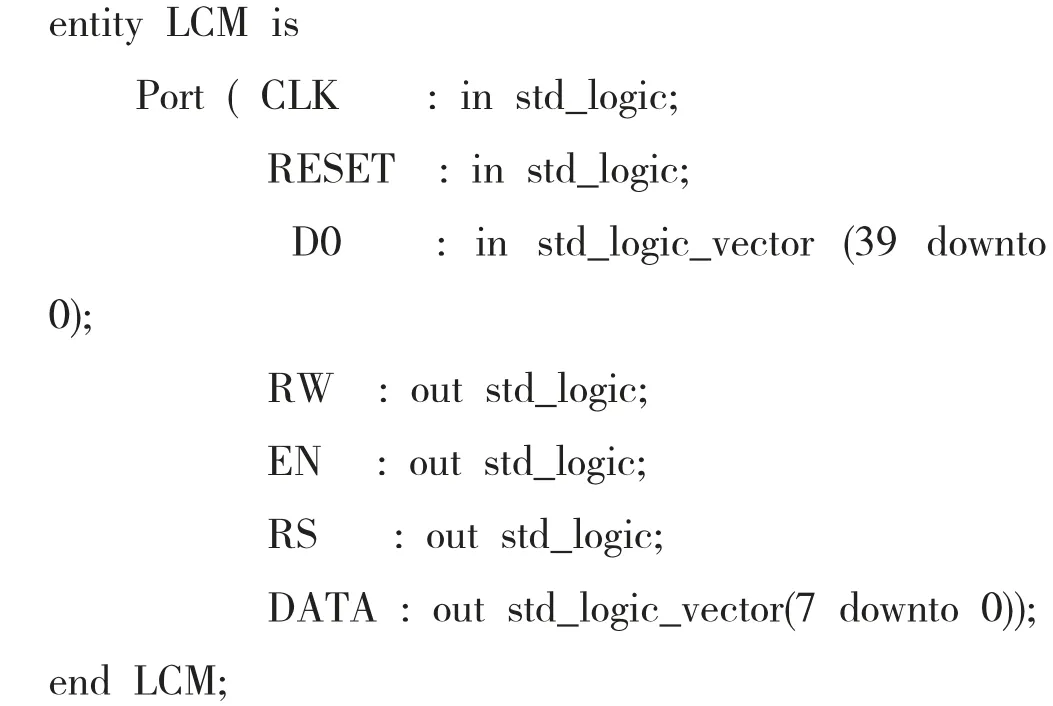

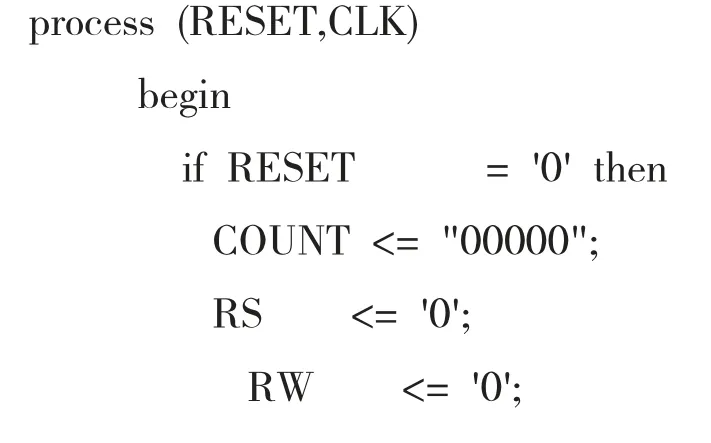

3.3 LCD 显示输出模块(LCM)

LCD 控制过程有两阶段:初始化阶段和循环扫描两行输出阶段;有一经显示就不变的静态显示,有需要不断刷新的动态显示。LCD 控制电路设计方法采用计数器方法。

其主要VHDL 代码如下:

实体声明:

主要进程:

在基于FPGA 的数字系统设计中,经常涉及到数据输出显示电路。而我们的设计经验表明应用EDA工具能方便地设计数据输出显示电路,特别是采用计数器描述显示驱动的方法,具有设计可读性及可迁移性,不失是一种好方法[4]。