高延迟信道下CAN总线控制器芯片的优化设计

2022-09-22靳旭

靳 旭

(1.北京全路通信信号研究设计院集团有限公司,北京 100070;2.北京市高速铁路运行控制系统工程技术研究中心,北京 100070)

1 概述

在轨道交通领域,CAN总线因其较高的实时性、可靠性等特点被广泛应用[1]。在对已流片的CAN控制器芯片进行大量测试的过程中,发现了一些单片测试时没有发现的问题,其中最值得注意的,是芯片在总线负载较大或收发器延时较大的情况下,容易发生通信错误、甚至无法通信的问题[2]。这主要是由于总线的延时超过原芯片设计的极限值,导致芯片内无法及时处理总线上的数据。在单片测试过程中,主要测试功能的正确性,器件选用的也都比较常规,对一些极限性能测试考虑不足。而在芯片设计时,选择性地忽略一些特殊的情况,使整体电路简化,也是比较常见的,但实际应用如果处于某些极端情况下,就会出现问题。本文基于原始芯片的设计方案,在对测试过程中发生的故障问题进行仿真、分析的基础上,对芯片进行优化,将其中发送器进行重新设计,并完成仿真验证,得到符合优化设计思想的结果,达到了流片的条件。

2 CAN总线相关概念

在介绍CAN总线控制器芯片的优化设计之前,首先需要了解一下有关CAN总线的一些基本概念。由于完整的CAN总线协议涉及相关内容较繁琐复杂,下文只介绍与本次优化设计关系紧密的部分概念。

2.1 线与原理

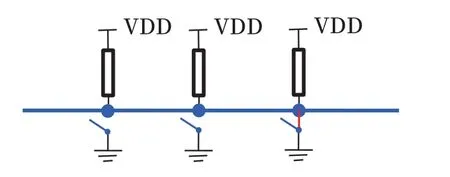

CAN总线符合“线与原理”,即多个节点并接到同一总线上时,只要其中一个节点输出低电平,总线就为低电平;只有所有节点输出高电平时,总线才为高电平[3]。如图1所示,类似并联接地,只要有一个节点输出低电平,总线电平就会被拉低。

图1 CAN总线“线与原理”示意Fig.1 Schematic diagram of CAN bus “Wire-And principle”

2.2 总线优先级判定准则

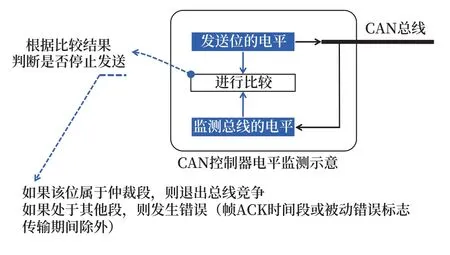

CAN总线上所有设备会随时监控总线数据,当检测到总线上有数据发送时,当前设备会等待总线空闲之后再发送。如遇同时发送的情况,当有设备监测到其他节点在发送时,发送帧优先级较低的节点会自动停止发送[4]。一般来说,接收与发送的信号可能会在仲裁段发生相异,即两个节点同时发送的情况。这时,发送ID编号更小的节点因为“线与原理”的存在,有更高的优先级,可以继续发送下去,而ID编号较大的节点因为检测到发送和接收的数据不一致,会停止发送。而如果检测到接收与发送不同的比特在仲裁段之外,则意味着发生了其他错误,这不属于总线优先级判定问题,可从错误寄存器中读取相关错误类型,如图2所示。

图2 总线优先级判定说明Fig.2 Determination description of bus priority

假设节点A、B和C都发送相同格式、相同类型的帧,如标准格式数据帧,它们竞争总线的过程如图3所示。优先级最高的节点A一直在发送,节点B和节点C则先后检测到总线上接收的数据与发送数据不同而停止发送。

图3 总线优先级判定Fig.3 Determination diagram of bus priority

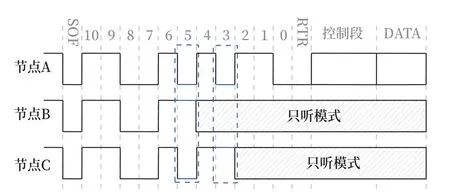

2.3 CAN总线ACK应答机制

在CAN总线通信过程中,总线上出现的帧按时间顺序依次为帧起始、仲裁段、控制段、数据段、CRC段、ACK段和帧结束[5]。当一个接收节点接收的帧从起始到CRC段之间的内容都没有发生错误时,它将在接下来的ACK段发送一个显性电平,这是CAN总线的ACK应答机制。而发送节点会在ACK段发送隐形电平,经过线与之后,如果有正确的ACK显性信号,则表示总线上有节点正确地接收到了本次发送的数据。发送节点可以根据是否收到显性电平来判断发送的帧是否被接收到,进而判断是否发送失败需要重新发送。数据帧结构及ACK段详细说明如图4所示。

图4 ACK应答信号的位置和判断方式Fig.4 Position and judgement method of ACK response signal

3 原始设计的优点和问题

3.1 设计优点

CAN总线控制器芯片初版设计,基于CAN通信的特点,即总线上需要实时监控对比发送和接收数据,没有设计独立的发送器,而是用接收器作为一切判断的基础。芯片在内部对接收总线做了定时心跳脉冲采样来监测总线上数据,同时,出于对设计简化的考虑,发送总线也采用了类似定时脉冲的方式进行处理,即做出同样一系列定时心跳脉冲信号来控制发送时的数据内部采样。

CAN总线控制器中通常通过在一比特数据的时间内进行采样来判断当前数据是“0”还是“1”。芯片通常会有配置采样点的寄存器,来调整在每比特数据中间采样的位置,可以设置1次采样或3次采样,比如NXP公司的SJA1000T芯片[6]中就有类似的设置,如图5所示。应用中一次采样使用较多,下文也都以一次采样为例来叙述。

图5 CAN总线接收端采样点配置Fig.5 Sampling point configuration at the receiver of CAN bus

如上文所述,原设计中,发送器脉冲没有独立的控制信号,发送脉冲在配置完成后一直存在,它和接收脉冲的时间差即为每比特数据开始的时刻与采样点位置的时间差。在通信速率不高(小于500 kbit/s)的情况下,几百纳秒的延时对于一位数据长达几微秒的时间来说影响较小。理论上,这种设计方式没有太大的问题,总线上理想状态下没有延时,实际应用中即使有延时,如果不运行在高速通信状态或者遇到延时特别大的情况,通信也不会发生问题。而这种设计方法减少了一套发送器的设计,降低了一定的复杂度。同时,发送、接收耦合在一起也不容易发生两者匹配的问题。实际应用中,在较低通信速度、较小的总线延时条件下,信道情况接近理想情况,通信并不会出现问题。

3.2 风险问题

在高速通信的情况下,常用的芯片外部电路连接方式如图6所示。

图6 常见的CAN总线连接方式Fig.6 Common connection type of CAN bus

在实际设计过程中,需要在总线控制器和总线收发器间增加光耦隔离器件,保证信号隔离[7]。可以看到,从A发送信号开始,整体延时时间为从控制器A 发送 → 隔离A → 收发器A →总线传播→收发器B → 隔离B → 控制器B接收。而如果控制器B要回应信号,则总延时翻倍。

当通信速度到达1 Mbit/s(CAN2.0协议允许的最大通信速率)时,由于每个比特只有16个周期(在16 MHz晶振条件下),即1 μs,而CAN总线通信在输入/输出端都要连接收发器和隔离器件,器件性能较差时,两者的最大延时均可达100 ns左右。从上述收发过程可以看出,从发送端发送出数据到接收端收到数据并回复,外部延时可达800 ns,再加上内部数据同步和CAN总线上的延时,最大可能会超过1 μs。这与1 Mbit/s通信速率下,一比特数据的时间已经可以匹配。对于ACK应答功能,即使将采样点移至最右端(87.5%处位置),在最坏情况下仍然无法保证发送节点在一比特数据时间内能够收到应答信号,这就会造成发送节点进入不断发送的死循环状态,直至超出错误限值进入静默。

4 优化设计的分析和方案

影响总延时的一个很重要的原因是开始计算“延时”的时刻,即从发送节点刚刚发送数据的时候,这是原方案中无独立发送器设计的结果,然而对于CAN总线上的一个节点来说,它对一段数据的判断应该是从接收到这段数据的时间开始。比如节点A发送数据给B的时候,A并不是在发送出去数据的时刻就立即收到了自己发送的数据,在CAN总线的通信中,A同样需要在通过隔离器件和收发器之后,才能收到自己发送的数据,所以这种情况下,使用A接收到数据的时间作为A进行一切判断的基准才是更为合理的。而原设计中因为发送、接收紧密耦合,发送“开始”和接收“采样”的时间差在配置之后即为恒定值,在原本时间裕量就不大的情况下,“多一倍”的外部延时会造成芯片内部如何优化都无法补偿的时序问题。

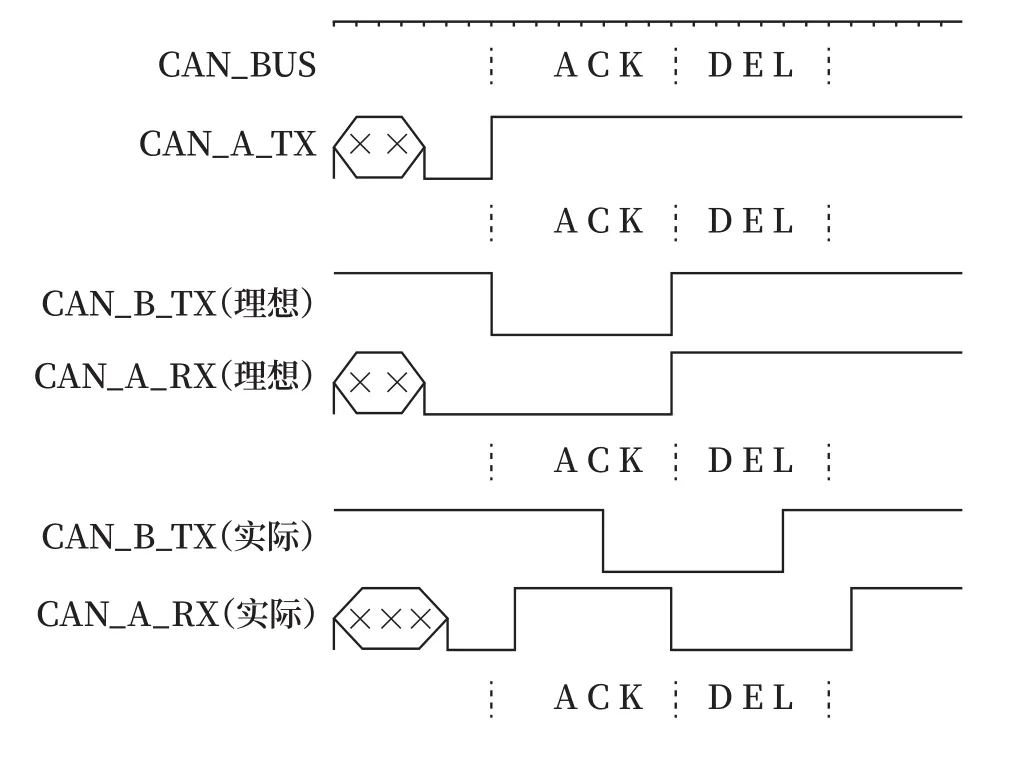

4.1 时序分析

下面以ACK应答错误为例对发生错误的时序情况进行分析。如图7所示,CAN_A为帧发送节点,CAN_B为帧接收节点,按照CAN通信协议,CAN_B需要在ACK槽期间内向CAN_A回复一位低信号,来表示接收正常。在理想(或延时较小)情况下,回复时间很容易满足要求;而在实际情况下,由于CAN_B端的发送和CAN_A端的接收都有延时,时间很可能超过以CAN_A发送时刻为起始时间的一比特位宽绝对时间,内部如果以发送接收都用固定脉冲方式来设计,就无法通过调节采样点以规避这个问题。实际上,即使关闭应答机制,较大延时造成的影响同样会使得通信过程中发生其他错误,例如位错误或CRC校验错误等,但都不及ACK应答错误表现得明显,限于篇幅在这里不再展开分析其他错误情况。

图7 ACK应答错误时序分析Fig.7 Timing analysis of ACK response errors

4.2 优化方案

发生这种问题的核心原因其实就在于接收采样脉冲与发送采样脉冲采用了同一套逻辑,两者之间的时间差是不依赖于外部电路、绝对的时间差。也就是说,这种情况下是以发送时刻为起始点计算,即发送“开始”和接收“采样”的时间差恒定,调整采样点最多也只能到当前比特位的结尾。然而,如果外部的电路出现较差延时的情况,绝对的时间相位差调整是不足以应对的。

实际上,采样点的概念本就应该是对接收信号而言,只有这样,才能把总线上发送节点自身从发送到接收的延时抵消掉,减少对通信产生的影响。而原版的设计中,是忽略了这一点的。所以优化设计的关键就是重新设计独立的发送器,解开发送器和接收器的耦合关系,将所谓的“延时时间”的起始,修改成从发送节点“接收到自己发送到总线上的数据”的时刻,其实这也更符合“接收”这个行为的定义。

当然,由于CAN总线存在总线信号监控的需求,发送和接收不可能完全独立。其中比对发送数据和接收数据就是解耦合过程中遇到的最大挑战。可以使用的一个解决方案是人为设定一个最大的延时阈值。例如设置为不超过随后一比特数据的时间,这个阈值以外的信号不再进行比对。在可容忍的延时时间之内,根据外部电路不同的情况,采样点正在采样的信号可能是在发送的当前信号,也有可能在发送的下一周期信号(延时较大),但是总信号的顺序编号是可以记录下来的,这样就可以根据当前信号的编号来比对数据,即可解决发送、接收数据比对的问题。

5 优化后仿真

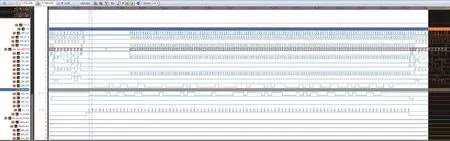

在按照优化思路对原设计进行修改之后,对新设计进行仿真验证是必须要做的。如图8所示,在1 Mbit/s的通信速率下,当把外部延时设置为800 ns(从发送端发出信号,经过隔离器件、收发器、总线延时,再经过接收端的收发器、隔离器件到达接收端的时间)时,芯片仍然保证可以进行正常通信,而在原设计中,超过300 ns就会出现仿真失败的情况。

图8 在1 Mbit/s通信速率下,模拟总延时800 ns时的仿真结果Fig.8 Simulation results when the total delay is 800 ns under 1 Mbit/s communication rate

为了在芯片流片之前保证功能没有错误,需要进行大量仿真来尽可能覆盖更多的功能。经过比较完备的仿真案例验证,新的芯片设计在优化发送器的基础上,成功改善了芯片在高延迟信道下通信性能,同时并没有引入其他的错误,可以认为优化设计后的芯片从功能层面具备了流片的条件。

6 结论

本文针对已流片的CAN控制器芯片在测试中发现的通信问题,从CAN总线协议的特点出发,介绍CAN总线相关的基本信息,阐述原设计的思路和存在的弊端,在此基础上通过分析出现问题信号的相互时序关系,确定了优化设计的方案。并在执行方案后对芯片的功能进行了完整的仿真验证,最终使得优化设计的芯片具备了重新流片的条件。