I2C主从通信协议扩展驱动设计①

2022-08-23方振国毛春雨

严 寒, 方振国, 汪 珺, 郭 伟, 毛春雨

(淮北师范大学物理与电子信息学院,安徽 淮北 235000)

0 引 言

I2C总线协议是由Philips公司开发的一种同步串行总线。相比于其它的串行协议来说,I2C总线拥有占用资源少、可以有多个主机控制和能挂载多个从机等优点,使得其被广泛的应用在系统内多个IC之间的通信。对于I2C协议挂载多从机进行数据传输也得到了业内人士的广泛应用和研究。其中,孙靖实现了嵌入式控制器基于I2C总线体系的外围设备扩展应用[1],但在设计中挂载在总线上的外围设备是通过器件地址进行区分,对器件地址相同的设备没有进行研究。邱永华通过PCF8574和数字开关实现了可连接器件地址相同的模块的I2C接口扩展器[2],但可连接数目受限,灵活扩展配置性能较差。基于可重构并行处理平台ZYNQ对I2C协议进行了扩展设计,有效的补充了了相同地址下的主从通信协议并解决了传输速率的自主选择问题。

1 I2C总线工作原理

I2C总线是一种简单的双向二进制同步串行总线,只需要使用一根时钟线(SCL)和一根双向数据线(SDA)即可在器件中进行传输信息[3]。主机和从机之间以一个字节(8bit)为单位进行双向传输,根据通信速率的不同,主机和从机进行数据传输时需要严格的遵循I2C的传输规范。读写操作如下:

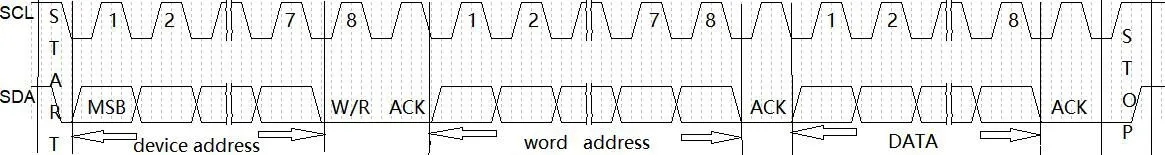

写数据操作分为Byte Write和Page Write两种,Byte Write时序如图1所示,根据时序图单字节写数据流程如下:主机发送起始信号->主机发送7位器件地址+1位写命令R/W(0为写)->主机发送8为字地址->从机返回响应信号ACK(0表示数据写入成功)->主机发送8位写数据->从机返回响应信号ACK->主机发送停止信号。

图1 写数据过程

读数据操作分为Random Read和Sequential Read两种,Random Read时序如图2所示,根据时序图单字节写数据流程如下:主机发送起始信号->主机发送7位器件地址+1位写命令R/W->主机发送8为字地址->从机返回响应信号ACK->主机发送起始信号->主机发送7位器件地址+1位读命令R/W(1为读)->从机返回响应信号ACK->从机发送8位数据->主机发送停止信号。

图2 读数据过程

2 系统设计

I2C主从通信扩展协议驱动系统如图3所示,设计主要包括参数配置、I2C总线接口、编码片选器三个部分,其中参数配置中有从机切换装置和I2C传输速率切换装置。

图3 I2C协议扩展驱动系统图

由系统框图可知,挂载在I2C总线上的从机拥有相同的器件地址,总线通过选通器对从机进行区分。为了节约资源,总线对所有从机都发送时钟信号(SCL),只对片选器选通的从机进行双向数据传输(SDA),为了防止数据误发,片选器一次只能对一个从机保持选通状态(即参数配置中从机切换装置每次只能选定一个从机进行数据传输)。为了实现I2C总线传输速率调节便利,设计中设置了低速(100Kbps)、中速模式(400Kbps)和高速模式(3.4Mbps)三种传输速率[4],可通过参数配置中的传输速率切换装置自由切换。

以I2C总线挂载4块从机为例,从机片选真值表如表1所示,由表可知,4块从机通过二进制进行编码需要2根切换线,可以通过从机切换装置控制切换线状态从而完成I2C总线和切换从机进行选通。

表1 从机片选真值表

3 设计验证

设计中的FPGA采用的Xilinx公司ZYNQ-7000开发平台,该开发平台集成了ARM处理器的软件可编程性和FPGA的硬件可编程性[5-7],设计软件采用Xilinx Vivado 2020.2,使用Verilog语言,并且使用Vivado软件中的逻辑分析仪进行设计验证。

设计验证中使用片选按键作为从机和传输速率切换装置,4块AT24C02 EEPROM模块作为从机,AT24C02器件地址为7’1010000。验证过程中往从机字地址8’b00110011中发送固定数据8’b01010101,通过对从机中发送的数据和读取的数据进行对比来验证本设计。

验证步骤如下:

1)配置传输速率为400Kbps,选定从机3;

2)写入数据到从机3,再从从机3读取写入的数据;

3)传输速率不变,选定从机4;

4)写入数据到从机4,再从从机4读取写入的数据;

5)选定从机4,分别切换传输速率切换为100Kbps,3.4Mbps,往从机写入数据。

使用100Kbps传输速率对选通从机3进行数据读写的时序图如图4,5所示,由图可知,数据传输过程中I2C总线只对从机3的双向数据线(sda)进行数据传输,且写入的数据和读取的数据皆为8’b01010101,其余从机双向数据线处于空闲状态。

图4 从机3数据写入时序图

使用100Kbps传输速率对选通从机4进行数据读写的时序图如图6,7所示,由图可知,数据传输过程中I2C总线只对从机4的双向数据线(sda)进行数据传输,且写入的数据和读取的数据皆为8’b01010101,其余从机双向数据线处于空闲状态。

图5 从机3数据读取时序图

图6 从机4数据写入时序图

图7 从机4数据读取时序图

F= 1/Ts

(1)

传输速率计算公式如公式1所示,其中F表示传输速率,Ts表示单个时钟信号周期消耗的时间。由图6可知4个时钟信号周期消耗1000个系统时间间隔,而系统时钟为50Mhz(20ns),故系统时间间隔为10ns。因此此时传输速率为式(2):

F=4/(1000*10ns)= 400Kbps

(2)

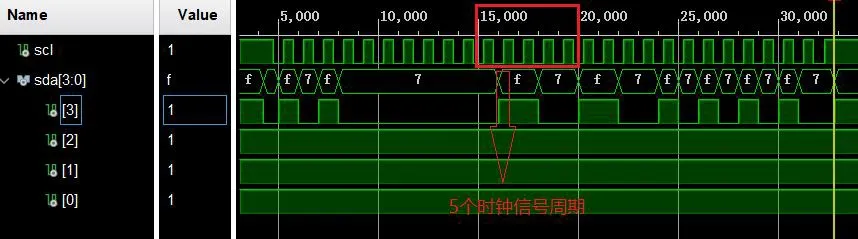

使用传输速率为100Kbps往从机4写入数据的时序如图8所示,由图可知5个时钟信号周期消耗5000个系统时间间隔。因此此时传输速率为式(3):

图8 传输速率100Kbps从机4数据写入时序图

F=5/(5000*10ns)= 100Kbps

(3)

使用传输速率为3.4Mbps往从机4写入数据的时序如图9所示,由图9可知3.4个时钟信号周期消耗100个系统时间间隔。因此此时传输速率为:

图9 传输速率3.4Mbps从机4数据写入时序图

F=3.4/(100*10ns)= 3.4Mbps

(4)

4 结 语

为了使主机可以通过I2C总线对拥有器件地址相同的从机进行数据传输和I2C总线可以自由切换传输速率,提出来一种基于FPGA的I2C扩展驱动设计方案,并通过ZYNQ-7000硬件开发平台,AT24C02 EEPROM模块和Vivado软件完成本设计,通过Vivado软件中的逻辑分析仪抓取的波形可以看出,主机可对任一从机进行数据传输,并且可以自由切换I2C总线的传输速率。设计结构简单、扩展性强、可移植性高,具有一定的实用价值,设计中若需要扩展从机设备,只需要增加系统的管脚资源而不用消耗其它硬件资源。