基于FPGA的多目标数字图像模拟器

2022-07-27张维达张甫恺

张维达,张甫恺,邹 悦,张 秒

(中国科学院长春光学精密机械与物理研究所,吉林长春 130033)

0 引言

目标跟踪一直以来都是计算机视觉领域的关键问题,最近随着人工智能技术的飞速发展,运动目标跟踪问题得到了越来越多的关注[1]。目标跟踪在图像处理角度可定义为根据已知目标图像位置预测后续所有影像中目标在图像中的位置的过程[2]。在实验室条件下获得持续稳定的多目标数字图像较为困难,因此需要设计一套能够模拟多个运动目标并实时输出的多目标数字图像模拟器[3]。Camera Link 接口作为高速相机最主要的标准接口之一,它的出现使得高速图像源数据和图像采集装置之间的速度得到匹配[4],在目标跟踪领域也有大量跟踪器采用Camera Link 接口作为标准输入接口。Camera Link串并芯片最高传输速率有限,是Camera Link数据传输系统的接口速率瓶颈之一[5],因此在多目标数字图像模拟器的设计中,利用FPGA串并转换接口替代传统的接口转换芯片,从而突破接口转换芯片的传输速率限制,实现高帧频数字图像输出。

为检验跟踪器的跟踪性能,模拟器中输出的图像目标的运动轨迹需要具有一定的随机性。线性反馈移位寄存器(linear feedback shift register,LFSR)是一类随机位序列生成器[6-7]。每个移动目标依据LFSR生成的具有随机性质的数据序列,确定其下一帧的移动方向、移动距离,从而实现具有一定随机性的运动轨迹。

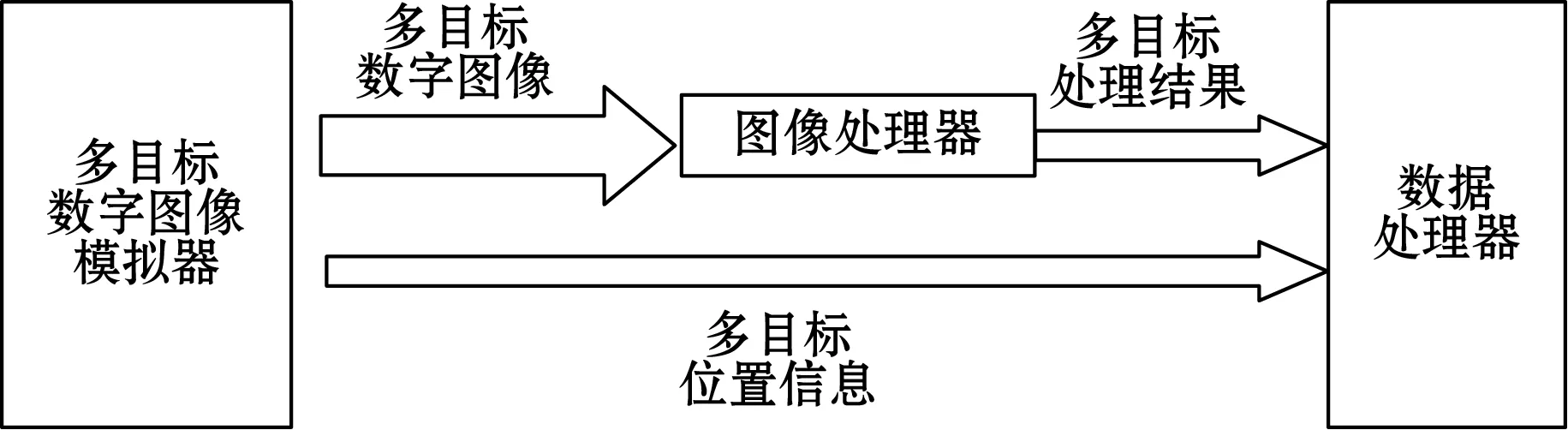

设计一个通讯模块,从图像生产模块中获得每个运动目标在当前图像中的位置信息并依次编号,按照约定的通讯协议,与带有多个模拟目标的数字图像同步输出。图像处理器接收带有多个运动目标的数字图像,并将多目标处理结果发送给后端的数据处理器。数据处理器同时接收当前图像的多个目标的位置信息以及图像处理器多目标处理结果,通过比较2组数据,实现对多目标数字图像处理器跟踪性能以及处理延时的检验,整个系统的工作原理如图1所示。

图1 多目标数字图像模拟器工作原理

1 系统组成

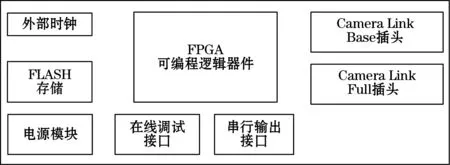

多目标数字图像模拟器的硬件主要由FPGA以及相应的外围电路构成,主要包括FPGA、外部时钟、FLASH存储模块、电源模块等。其中外部时钟负责给整个系统提供时钟基准;FLASH存储芯片负责存储系统的程序数据文件并在每次上电时完成对FPGA的逻辑初始化工作;电源模块负责为整个系统供电,并保证上电过程中不同电平的上电顺序。在线调试接口即JTAG接口,能够实现程序的烧录及在线仿真。串行输出接口采用接口芯片将FPGA输出的TTL数字信号转换为标准422差分信号,输出给后端的数据处理器。Camera Link输出接口采用标准的Full模式接口,包含Base和Medium/Full 2个独立的MDR26物理接口,能够实现最高6.8 Gbps的数字图像数据输出。整个系统的硬件组成原理框图如图2所示。

图2 系统硬件组成

2 FPGA逻辑模块

FPGA是整个系统的逻辑处理核心,其内部分为时钟模块、行/场信号生成模块、背景生成模块、随机数生成模块、目标轨迹规划模块、目标叠加模块、Camera Link编码模块和串行输出模块。其中随机数生成模块和目标轨迹规划模块依据目标数量配置,每个运动目标均含有独立的随机数生成和轨迹规划模块。FPGA逻辑模块框图如图3所示。

图3 FPGA逻辑模块框图

时钟模块主要由系统内部PLL组成,其主要功能是接收外部40 MHz低速时钟,经过内部锁相环锁频后,输出驱动行/场信号模块的像素时钟以及随机数生成模块的驱动时钟,时钟模块还为整个系统提供系统复位信号,是整个逻辑系统的基础支撑模块。

行/场信号生成模块内部主要由定时计数器组成。计数器由像素时钟驱动,每2.5 ms生成1个场信号起始脉冲,10个像素时钟后,产生首行起始的脉冲信号。为了生成1 920×1 080分辨率的10 Tap/8 bit数字图像,每个行有效信号应该持续192个像素时钟周期,每个场有效信号持续时间内应包含1 080个行有效信号。同时行/场信号生成模块还能够同步输出当前行/场信号对应的具体行数和每行的相对位置,为后续的背景生成模块和目标叠加模块提供目标叠加的位置依据。

随机数生成模块接收时钟生成模块的驱动时钟,利用线性反馈移位寄存器生成32位随机数。线性反馈移位寄存器的输入为驱动时钟、使能信号以及随机数种子,输出为32位随机数。根据系统模拟的目标数N,设置N+1个相互独立的随机数生成模块。模块0产生的随机数送入背景生成模块,输入时钟为像素时钟;模块1~N产生的随机数送入轨迹规划模块,输入时钟为与场信号同步的控制时钟。

背景生成模块在行/场信息有效的情况下,对数字图像信息进行充填,为了保证目标对比度,每个像素的低3位采用随机数生成器生成的随机数充填,高5位置0。

轨迹规划模块接收随机数生成模块产生的随机数据。将接收的随机数的数值分为4个区间,每个区间分别对应目标的上、下、左、右4个移动方向。移动的步长由随机数序列的低4位决定,保证每次移动的最大距离不超过15像素。为保证运动目标一直在有效区域内,设计了一个目标运动限制区,达到限制区域的运动目标被强制改变为向图像中心运动。

目标叠加模块同时接收多个轨迹规划模块输出目标的中心位置,并将中心位置及其周围15像素范围内的数字图像替换为目标图像,所有目标的图像替换同步进行,从而实现多目标数字图像的模拟功能。

串行输出模块从目标叠加模块中获取当前全部移动目标的中心位置的坐标,每个坐标包含x方向,y方向数据,共计4 byte。将其10个目标的40 byte数据依次存储在FIFO中,以当前数字图像场信号的上升沿作为串口发送的触发条件,依照约定的通讯协议向外发送。通过接口芯片将FPGA发出的TTL电平信号转换为标准422串行数字信号。

3 Camera Link数字图像输出

Camera Link数字图像输出采用带宽利用率最高的Full-80bit模式进行,采用2个标准Camera Link物理接口Base接口和Medium/Full共用接口。每个接口包含4路数据差分信号,采用7∶1的串并转换比,将7 bit的并行信号转换为1路串行信号,每组信号在单个像素时钟周期内传输的数据总数为28 bit。标准的Camera Link协议中,28 bit数据中的第25位为数字图像场信号Fval,第24位为数字图像行有效信号Lval,第26位为数据有效信号Dval。Base、Medium和Full 3组差分信号的定义完全相同,因此整个传输通道的有效带宽利用率为25/28=89.28%。在Camera Link Full-80bit传输模式下,Base差分对中保留第24位、25位作为数字图像数据的行有效信号、场有效信号,Medium和Full差分对中仅保留第27位作为行有效信号,整个传输通道不再保留数据有效信号,从而使得有效带宽利用率提升为(26+27+27)/84=95.24%。

4 仿真调试

多目标数字图像模拟器采用Vivado软件平台开发,平台具有事前仿真和实时在线仿真2种仿真验证工具,其中实时在线仿真工具包为ILA在线仿真工具。ILA在线仿真工具在Synthesis阶段后,通过添加ILA内核实现信号的在线仿真、观测。ILA内核具有较高的灵活性,能够自由选择观测信号的种类、数量以及参考时钟,设计过程中可以部署多个ILA内核以实现对不同时钟域信号的观测。

为了验证数字图像的画幅完整性,需要对数字图像的行、场信号进行观测。根据Camera Link Full-80bit协议,Base通道第25位为场信号Fval,Meidum通道的第27位为行有效信号Lval,将2个信号以及行、场计数器同时加入观测信号,设置触发条件为场信号Fval的下降沿。多目标数字图像的行、场信号在线仿真时序图如图4所示。通过观察行、场计数器可以知道,此时数字行数为1 080行,每行的持续时间为192个像素时钟周期。由于Full-80 bit模式下,每个像素时钟周期内能够同时传输10 tap数字图像,因此每行能够输出的数字图像数据为1 920像素,在线仿真结果满足数字图像模拟器设计要求。

图4 行、场信号在线仿真时序图

对随机数生成模块0使用的线性反馈移位寄存器输出进行在线仿真观测,数据观测时钟为像素时钟,单次采样数据总量为1 024。将采集观测的随机数据依据数值大小转换为图形数据,如图5所示。通过观测数据波形可以看到模块0输出的数据具有一定的随机性,满足背景生成模块和轨迹规划模块的数据需求。

图5 随机数生成模块输出波形图

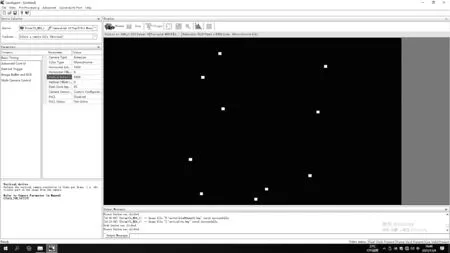

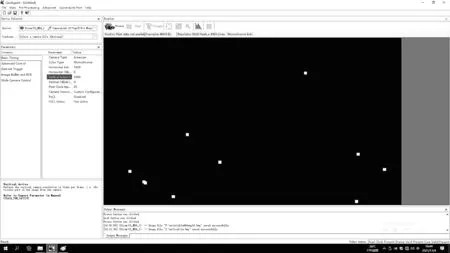

采用Xtium-CL MX4采集卡作为多目标数字图像模拟器输出数字图像的采集终端。将采集卡设置为10tap-8bit采集模式,通过Sapera CamExpert实时监控软件可以观察到当前数字图像的帧频为400 Hz,如图6所示,数字图像的采集分辨率为1 920×1 080,可以观察到共有10个移动的数字图像目标分布在整个图像区域内。通过Pixel Viewer工具检查图像中背景的像素值,如图7所示,可以观察到数字图像的背景灰度值由无规律的数字充填,充填的最大值为7。

(a)实时采集图1

(b)实时采集图2图6 多目标数字图像采集图

图7 背景充填像素数值分布图

5 结论

设计了基于FPGA的多目标数字图像模拟器,能够在Camera Link Full-80bit模式下,以85 MHz的像素时钟输出分辨率为1 920×1 080的数字图像,输出最高帧频为400 Hz的数字图像。图像具有通过线性反馈移位寄存器LFSR生成的具有随机噪声的背景和10个轨迹具有一定随机性的运动目标。通过FPGA在线仿真,可以观察到多目标数字图像模拟器生成的数字图像能够达到预期的数字图像分辨率和帧频,随机数生成器工作正常。通过高速数字图像采集卡采集并显示高速数字图像,验证了数字图像的完整性以及运动目标轨迹的随机性。