基于万兆以太网的Cameralink数字图像光纤传输系统

2022-07-27张甫恺张维达

王 岩,张甫恺,张维达,邹 悦

(中国科学院长春光学精密机械与物理研究所,吉林长春 130033)

0 引言

随着科学技术的迅速发展,人们对用于航天航空、雷达和通信等领域的图像传输需求越来越高。Cameralink接口因具有实时性好、稳定性高、可用于高速传输等优点,现已成为工业相机应用最广泛的接口之一[1]。该接口是由多家相机生产厂商和数码相机供应商联合制定的高速串口通信协议接口,采用低压差分信号(LVDS)进行传输,包含11对LVDS信号和4个电源信号。Cameralink接口有Base、Medium、Full 3种工作模式[2]。Base模式使用1个连接器,通过端口A-C进行数据传输,最大传输速度为2.0 Gbit/s。Medium模式使用2个连接器,通过端口A-E进行数据传输,最大传输速度为4.8 Gbit/s,如果使用2个相同的Medium接口,就可成为双Medium接口。Full模式使用2个连接器,通过端口A-H进行数据传输,最大传输速度可达5.4 Gbit/s[3]。

由于数字成像技术在帧频、带宽和分辨率等方面的要求越来越高,所产生的数字图像数据量也越来越大。因此,将大量的图像数据进行传输对传输通道有非常高的要求。万兆以太网作为新一代网络传输标准,仍然保留了以太网帧结构,可兼容当前已有的网络传输环境,很大程度上降低了开发成本[4-5]。万兆以太网采用光纤代替网线来作为物理传输媒介,传输带宽提升至10 Gbit/s,比千兆以太网提升了10倍,最长传输距离可达40 km,可满足大量图像数据传输的需求[6]。

1 系统设计

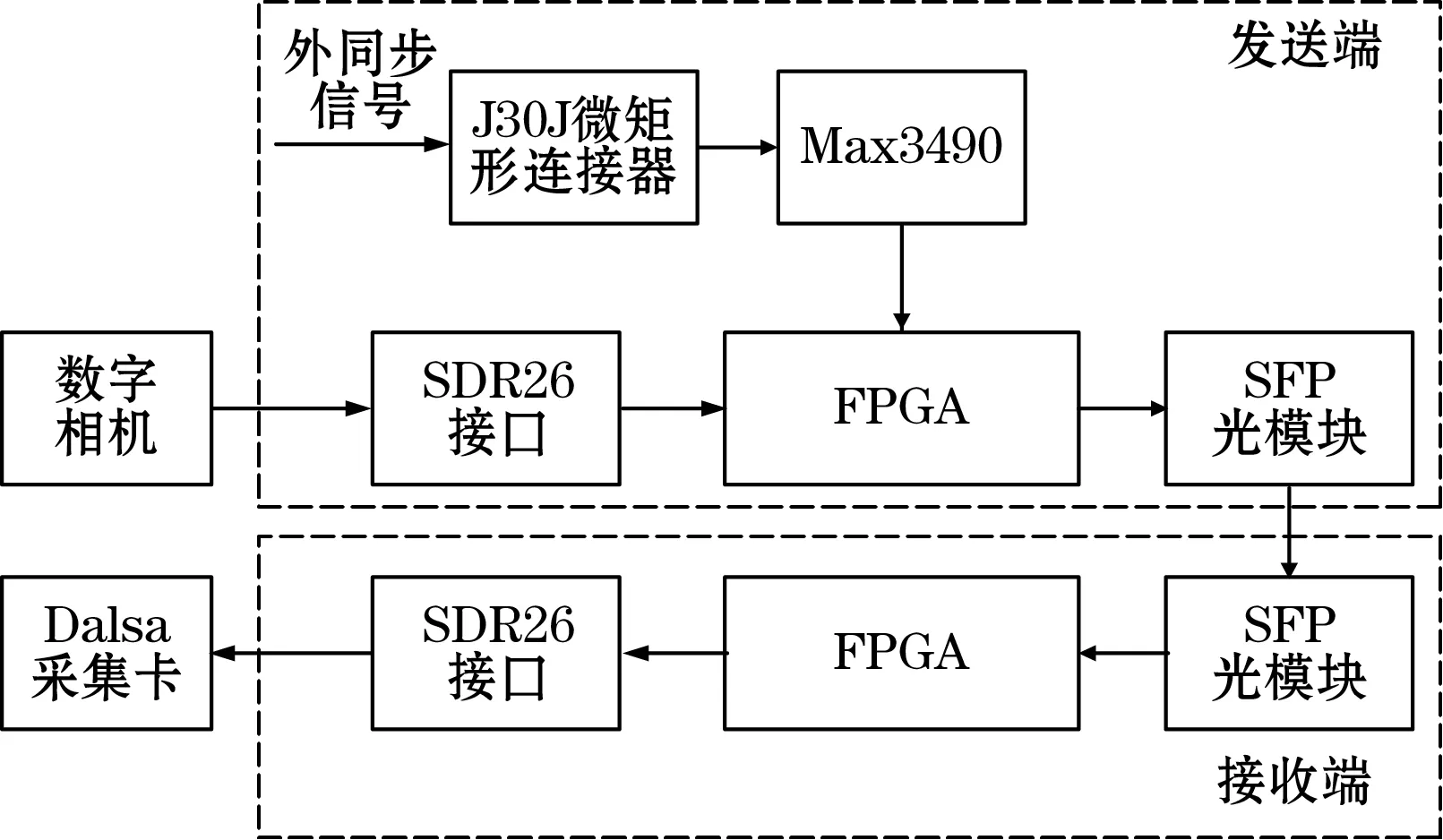

系统采用Kintex-7系列的XC7k325T芯片作为核心处理器,主要实现Cameralink接口电路、J30J接口电路、万兆以太网接口等。Kintex-7系列拥有超高的性价比,为高端功能提供了平衡优化的配置。该系列具有高性能的10.3 Gbit/s串行连接器、低成本优化的6.5 Gbit/s串行连接器及存储器,能支持大量10G光学有线通信设备和无线网络设备[7]。系统设计框图如图1所示。数字图像由SDR26接口接入发送端FPGA板卡,经FPGA数据处理后转化为AXI4-stream数据流通过SFP光模块连接的光纤传输到接收端。接收端FPGA板卡将接收到的AXI4-stream数据流再转换为Cameralink协议的图像数据通过SDR26接口输出到Dalsa采集卡。

图1 系统设计框图

2 主要功能模块设计

2.1 Cameralink图像接口模块

当采用Cameralink协议传输图像时,发送端相机会输出4对差分数据和1对时钟差分信号。根据协议需将这5对差分信号转化为CMOS/TTL信号,接收时再将CMOS/TTL信号转换为LVDS信号。传统的方法是在发送端采用DS90CR286/288芯片将LVDS信号转换为CMOS/TTL信号,在接收端采用DS90CR285/287芯片将CMOS/TTL信号转换为LVDS信号[7]。采用芯片进行信号转换虽然比较方便,但是在设计电路板时需要考虑芯片的设计,在使用时若存在电磁干扰会影响信号的传输,甚至有时存在芯片损坏的情况,影响调试的进度。因此,为了方便开发者使用,Xilinx公司提供了一个SelectIO IP核用于Cameralink协议发送和接收信号的相互转换。采用SelectIO IP核直接对信号进行转换,避免了因芯片带来的上述问题。使用SelectIO IP核作为Cameralink图像接口对图像数据进行处理的框图如图2所示。发送端的输入为4对Cameralink差分串行数据流、1倍频Cameralink时钟和7倍频Cameralink时钟,在时钟作用下将4对串行数据按照解串比为1∶7的比例转换为28位的并行Cameralink数据[8-9]。接收端主要将28位的Cameralink数据在时钟作用下转换为4对Cameralink数据。

图2 Cameralink图像接口框图

2.2 2 Meiudm图像数据流处理模块

8×12 bit的2 Medium图像模式每次传输的数据量为96 bit,但是系统用于万兆以太网传输的AXI4-stream数据宽度为64 bit。因此,需对2 Meiudm图像数据流进行处理。2 Medium图像数据流处理框图如图3所示。

图3 2 Medium图像数据流处理框图

在发送端首先使用一个同步时钟FIFO模块对图像数据进行缓存,随后将96 bit的2 Medium图像数据拆分成2个48 bit的图像数据,依次写入一个异步时钟FIFO模块。经过异步时钟FIFO模块后,时钟变为AXI4-stream数据流传输的时钟,读出的48 bit图像数据添加16 bit的0转换成64 bit的数据。最后将数据转换为AXI4-stream数据流送入10G Ethernet发送模块进行发送。在接收端首先使用10G Ethernet接收模块对AXI4-stream数据流进行接收。然后根据时钟节拍分别写入2个异步时钟FIFO模块,将64 bit的数据转换为2个48 bit的图像数据。最后将2个48 bit的图像数据组合成96 bit的2 Medium图像数据,进而转换成标准的Cameralink的图像数据格式。

2.3 万兆以太网光纤传输模块

万兆以太网光纤传输模块采用AXI4-stream总线协议,该协议的数据宽度为32位或64位。系统选用64位的数据宽度进行传输,其传输时序图如图4所示。64位AXI4-stream数据流的组成主要包括tready(准备传输)信号、tdata(数据)、tvalid(传输有效)信号、tlast(传输结尾)信号等。其中,tdata数据头部需插入源地址和目的地址。当发送帧时,需要将tvalid信号置高来表示数据有效周期,tlast信号被置高一个时钟周期,用于指示数据包的结束。当接收到有效数据时,tready信号被置为有效。

图4 AXI4-stream 64位传输时序图

3 实验验证

实验首先对图像的发送端和接收端进行时序验证。发送端使用红外相机进行图像传输,相机帧频为1 kHz,分辨率为640×512,工作模式为8×12 bit的2 Medium模式,数字图像的传输带宽为3.93 Gbit/s。通过FPGA逻辑分析仪观测的发送端时序图如图5所示,接收端时序图如图6所示。从图中可看出,通过光纤传输的万兆以太网AXI4-stream数据流时序是正确的。

接收端接收到的测试图像如图7所示,图7(a)为接收端恢复的横向渐变测试图,图7(b)为接收端恢复的纵向渐变测试图。经验证,系统工作稳定,接收端还原的测试图像与发送端发送的图像数据完全一致。综上,可证明经系统实时传输后的图像数据是稳定、可靠的。

图5 FPGA观测发送端时序图

图6 FPGA观测接收端时序图

(a)横向渐变测试图

4 结束语

系统采用万兆以太网对数字图像数据进行光纤传输,减少了对接口芯片的使用,解决了工业相机在传输高分辨率和高帧频图像时传输困难的问题。实验结果表明,系统可将工业相机高帧频2 Medium模式的Cameralink图像数据转化为AXI4-stream数据流进行高速、稳定的光纤传输。