FPGA和以太网的实时视频图像传输系统

2022-07-23福州大学物理与信息工程学院徐志辉

福州大学物理与信息工程学院 徐志辉

为了实现对高清视频图像的实时稳定的传输,基于当前成熟高速可靠稳定的以太网,结合具有强大并行处理能力的FPGA设计了一种基于FPGA和以太网的实时视频传输系统。该系统主要采用了Altera公司的Cyclone IV系列FPGA开发板,OV5640摄像头作为视频图像数据采集口,数据通过SDRAM读写FIFO,写入读出SDRAM,以太网数据通信模块读出数据后进行数据格式封装,经过RJ45以太网接口,最终视频图像在显示器上显示。系统具有传输距离远,延时低,速率高的特点。

近年来,随着电子技术,信息技术,计算机网络技术的高速发展,网络信息数据的传输量级指数级增长,特别是视频图像这类大容量数据的传输对于传输技术提出了越来越高的求。以太网(Ethernet)是诞生于20世纪70年代的一种局域网技术,具有成本低,传输速率快,抗干扰性强的特点。其数据传输速率从早期10MBPS,快速发展到如今最高可达100GBPS的超高传输能力,以太网已经可以满足目前大容量超清视频图像数据传输的用途,在普通消费级与工业领域主要以百兆,千兆以太网为主。以太网在视频监控领域相比于传统的USB传输方案传输距离可达20倍,优势非常明显。而FPGA具备非常强大的数据并行处理能力,结合千兆以太网可以实现实时传输大量的高清图像数据,具有效率高低延时的特点。通过使用FPGA与以太网能够实时高速视频图像数据传输。

1 系统的总体硬件架构

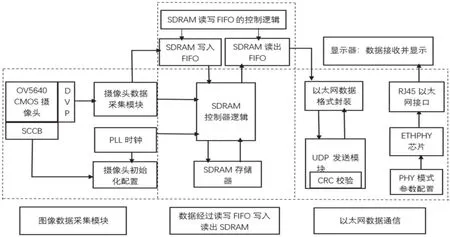

本系统总体上来看需要用到三大主要模块,分别是CMOS图像传感器OV5640模块,DDR2-sdram读写控制模块,以太网数据格式封装模块,以太网UDP协议发送模块,以太网CRC32校验模块。在数据经过三大模块的处理以后,最终图像显示在显示器上。CMOS图像传感器OV5640主要用于实时采集所要传输的视频图像数据,采集到的图像数据通过OV5640内置的一些基础的图像处理步骤后,数据将在SDRAM读写控制模块的控制下写入到SDRAM存储器中,之后以太网数据格式封装模块将经过SDRAM读写控制模块从SDRAM中读取数据,经过UDP,IP,MAC层协议层层封装后发送给PHY芯片,以太网CRC32校验模块计算经由MAC层发送的数据的CRC值并附加在MAC结尾发送。系统的总体架构图如图1所示。

图1 系统的总体架构图

2 CMOS视频图像采集传感器模块

系统的CMOS视频图像采集传感器采用了OV5640传感器,支持标准的SCCB接口以及I2C接口,支持RGB,YUV格式,支持数字视频接口。OV5640 CMOS传感器外部是一个10x2共20针的引脚。除了基础电源引脚以外,重要的的引脚包括OV_SCL引脚,这是用于SCCB通信的时钟信号,其效果等价于I2C总线的SCLK时钟信号。OV-SDA引脚,这是用于SCCB通信的数据信号引脚,其效果等价于I2C总线的时钟SDAT信号。XCLK引脚是OV5640的基本工作时钟引脚,默认24MHZ,可以利用片上PLL将该时钟倍频到一定频率后供片上其他功能电路使用。

OV_VSYNV,OV_HREF分别是帧同步信号与行同步信号,前者用于每一幅新图像输出前产生一个高脉冲,后者用于输出一行图像数据的过程中保持高电平。在场同步信号VSYNC期间,传输完成一幅图像所有行的数据。之后就可以开始下一帧图像数据的传输,不断重复就可以传输视频图像数据。图2为RAW图像格式下分辨率设置为640*480的图像采集时序示意图。

图2 RAW图像格式分辨率设置为640*480的图像采集时序示意图

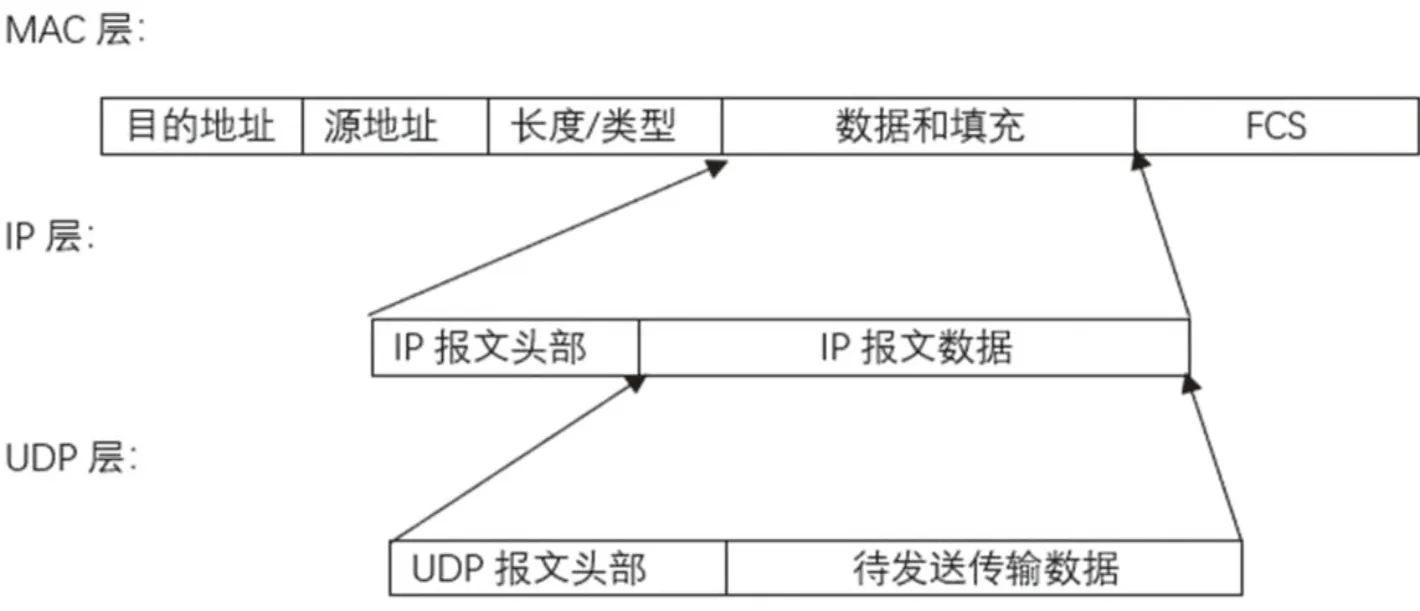

图3 UDP层,IP层,MAC层数据之间的关系

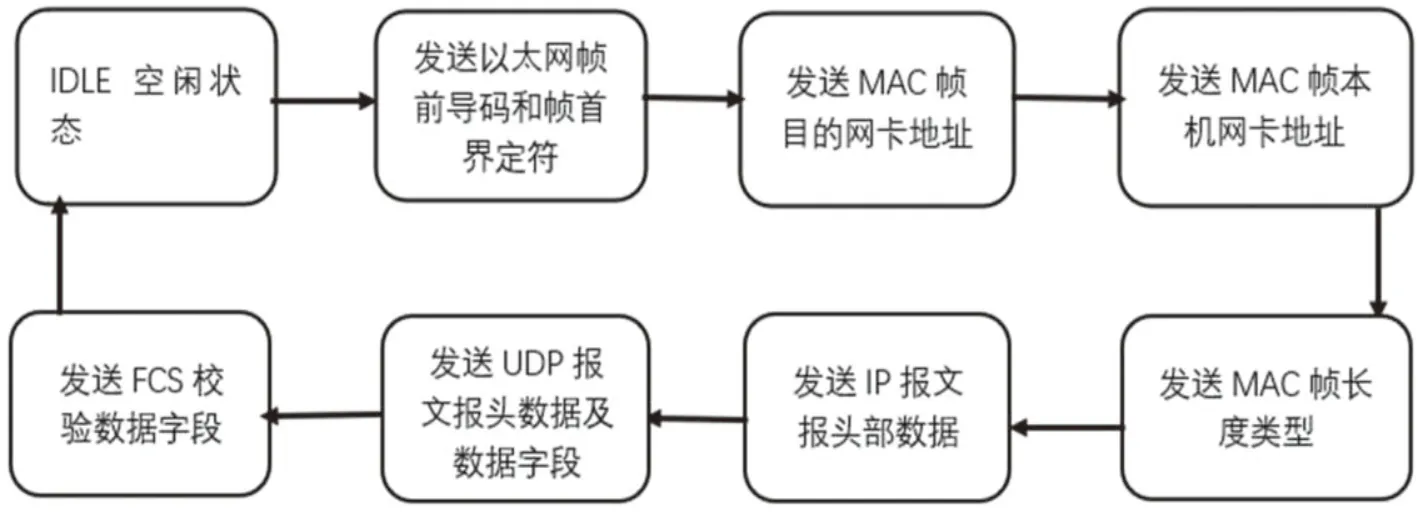

图4 以太网模块数据发送状态机

3 SDRAM控制模块

SDRAM结构实际上可以看成是由多个存储单元构成的矩阵阵列,每一个存储单元包含了,行地址线,列地址线,电容,刷新放大器,数据线。确定了行地址线与列地址线就可以确定存储位置。每一个存储阵列是1个BANK,通常1个SDRAM有4个BANK.由于CMOS传感器采集的是视频图像数据,数据的输入输出具有顺序性。对于这种类型的数据,只用SDRAM控制器模块控制数据的写入与读出时可能会出现在一些特殊时刻,读写会被忽略掉,从而导致数据的写入或者存储出现丢失,无法顺利完成连续性数据的存储。FIFO(先入先出)存储器可以作为一种短暂缓冲型数据存储器,可以在CMOS图像数据写入到SDRAM之前加入一个SDRAM写FIFO,数据经过这个FIFO作为缓冲输入SDRAM,在以太网模块从SDRAM中读出数据中间加入一个SDRAM读FIFO,该FIFO作为数据读出缓冲。当SDRAM写FIFO模块中的存储数据量大于一次突发写长度时则将SDRAM控制器模块的写使能信号WR拉高,将从OV5640传感器采集写入FIFO中缓存的数据写入进SDRAM。当SDRAM读FIFO模块中的存储数据量小于整个FIFO能存放的数据量的一半时则将SDRAM的读使能信号RD拉高,从SDRAM中读数据。当以太网数据格式封装模块发出读请求时,则将从此读数据。

4 以太网通信模块

该以太网传输系统基于UDP协议。UDP协议的主要功能是将待传输数据封装成特定格式。每个UDP数据包的报头信息前8个字节包含了端口,数据包长度等信息,其他的字节则是待传输数据。待传输数据经过UDP协议打包,UDP协议又是一个基于IP协议的,因此在UDP数据基础上加上IP报头信息,即可得到IP层的数据内容。IP层经MAC层发送,因此加其基础上加上MAC帧头以及校验字段,即可得到MAC层数据内容。UDP层数据,IP层数据,MAC层数据之间的关系如图3所示。

实现以太网的通信除了需要以太网接口(RJ45接口)以外,还需要专用的转换芯片PHY,实现TTL电平和高速串行数据收发模式的转换,并行以太网数据到符合以太网物理层链路数据传输格式的电平信号之间的转换。PHY芯片与MAC层连接有3种方式:百兆速率采用MII接口,千兆速率采用GMII接口,以及GMII的简化版RGMII接口。以太网数据格式封装模块从SDRAM读FIFO中提取出16位的数据并转换成32位的数据,添加数据帧头避免丢包,之后按行发送数据。数据发送状态机应该为以下几个状态的转换迁移:1)空闲状态IDLE;2)送前导码和帧首定界符的状态;3)发送MAC帧的目的网卡地址字段;4)发送MAC帧的本机网卡地址字段;5)MAC帧的长度类型字段;6)IP报文报头部数据字段;7)UDP报文报头部数据字段及UDP数据字段;8)发送FCS校验数据字段。发送的数据将经过CRC校验模块的校验,校验结果值放在以太网帧的FCS段,校验错误将不会接收该帧数据。图4所示为发送状态机示意图。

结语:本系统主要由OV5640摄像头初始化及数据采集模块,SDRAM读写FIFO及SDRAM太网的视频数据传输,距离远,速率高,稳定性强,可以在复杂环境下实现稳定高速的传输高清视频图像数据,具有一定的实际意义。