多功能车辆总线实时监控与时序分析

2022-07-15蒋红果王业泰

蒋红果,王业泰

(1 中车南京浦镇车辆有限公司, 南京 210031;2 南京中车浦镇海泰制动设备有限公司, 南京 211800)

我国高速铁路近年来蓬勃发展,而列车通信网络(TCN)作为动车组核心技术之一成为了研究的热门问题。TCN 的层次结构被IEC 61375 标准分成了绞线式列车总线(WTB)和多功能车辆总线(MVB)两级总线,MVB 用于连接车辆内部各种设备,是将位于车辆中的标准设备连接到TCN 上的一种总线[1]。对于列车系统运行的可靠性和实时控制等要求MVB 均可满足,是标准数据的传输载体,无论是控制信息还是乘客服务信息,均能可靠地在列车上交换数据和传输数据[2]。

目前,对MVB 数据帧的采集、解码和分析方面的研究,都是在MVB 数据的基础上实现总线分析,其分析的都是MVB 数据帧信息,并未将MVB数据进行实时性的存储,对设备的线下维护和检修造成诸多不便[3-6]。因此,建立一个既能实时对MVB 数据进行存储又能将MVB 数据实时且可靠地传送到上位机的系统,实现司机室对数据实时监视的同时为数据的安全性提供保障,且可为线下检修维护提供大量的数据基础具有重要意义。

文中在深入理解嵌入式系统原理、MVB 总线和IEC 61375 协议的基础上,分析了MVB 的通信协议,提出了一种基于嵌入式系统MVB 数据实时监控程序和数据时序分析程序的设计方案,测试了MVB 数据采集、过程数据主帧与基本周期的识别以及MVB 周期轮询表的解析等模块功能的实现情况,验证了设计方案的正确性。

1 MVB 概述

MVB 是将位于同一或不同车辆中的各种标准内设备连接到TCN 上的一种总线,MVB 总线协议主要分为2 个部分:过程变量协议与消息协议。变量服务主要传输具有固定传输周期和传输延迟的终端数据,其包括应用层接口(AVI)和数据链路层接口(LPA);消息服务主要传输长度不定、不紧迫、不频繁、发送时延必须短但允许变化的数据,其包括应用层接口(AMI)和数据链路层接口(LMA)。

MVB 报文主要由主帧和从帧2 部分构成,并分为消息数据报文、过程数据报文和监视数据报文3 种类型[7]。MVB 的控制方式为单一的总线主控制,规定可以存在多个主设备,但在同一时刻只能有1 个主设备拥有控制权,其遵循确定的机制在能够成为主设备的设备间轮流给予控制权[8]。主设备将1 个轮回周期划分4 个时间片,该轮回周期称为“基本周期”,由周期相、监视相、事件相和保护相组成。主设备在周期相内轮询周期数据。周期轮询表的构成有如下几点规则:通过特征周期对周期数据进行分类;在1 个循环中,把具有相同特征周期的周期性数据编成1 组,其组名用其特征周期为基本周期的倍数表示;1 个宏循环是由1 个宏周期内的所有循环组成,如果特征周期为1 ms时,则其为1 024 个基本周期[9]。在1 个基本周期中也可将监视相、事件相和保护相称作偶发相,偶发相传送的是监视数据和消息数据,处于2 个周期相之间。

2 MVB 数据实时监控和时序分析设计

2.1 MVB 数据实时采集功能

MVB 数据监控程序完成的功能主要为:嵌入式系统通过USB 读取FPGA 解析好的MVB 数据,并转换为十六进制,为后续存储数据、处理数据和上位机观察数据提供方便;嵌入式系统将转码后的MVB 数据存储到以系统时间命名的文本文件中,方便后续数据时序分析程序进行数据分析以及停车离线检修维护时的数据收集统计;将嵌入式系统和上位机设置为同一网段,嵌入式系统建立UDP 服务器端,将转换后的MVB 链路层数据通过以太网接口发送至上位机;将数据读取模块、数据存储模块、数据转发模块设置为多线程,并通过信号量控制线程的运行顺序以及线程间数据的同步与互斥问题。具体系统架构如图1 所示。

图1 系统架构

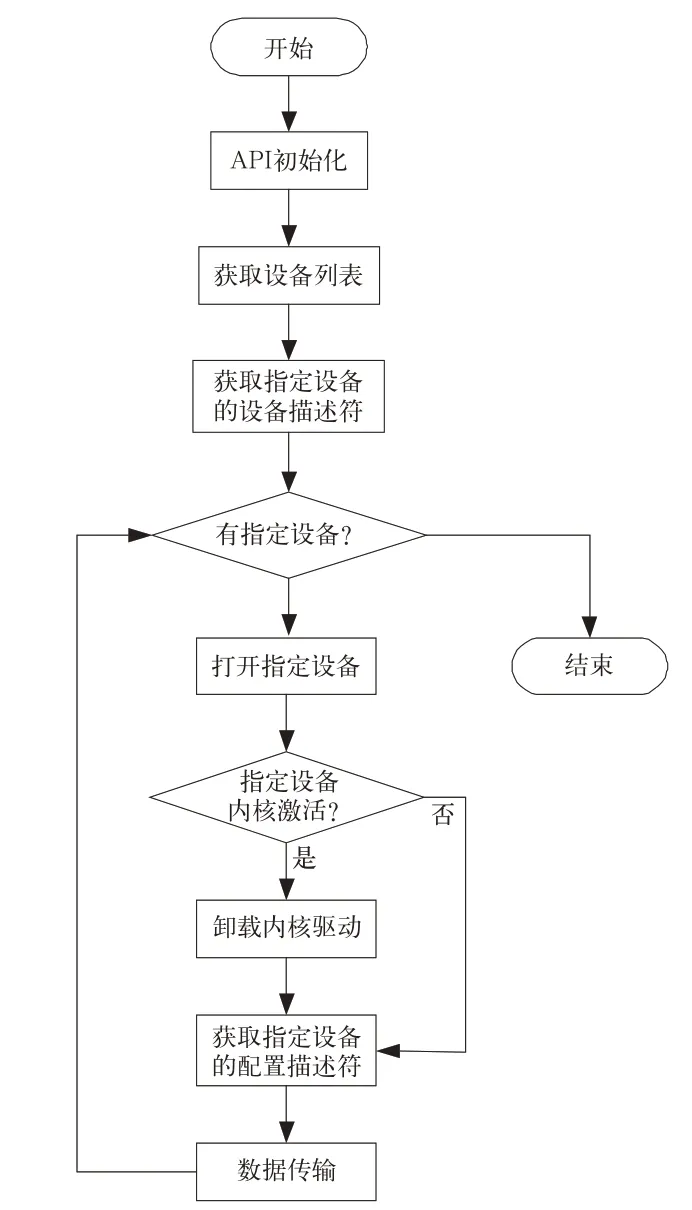

使用Linux 系统中基于libusb 库的USB 文件系统的驱动开发,并将其应用到嵌入式系统中以提高程序开发效率。文中结合设备描述符、配置描述符、接口描述符和端点描述符的结构体,使用libusb 的API 函数,实现数据采集的功能。使用libusb 的API 接口函数从USB 读出数据的流程如图2 所示。

图2 使用libusb 的API 函数读取数据流程

另外,嵌入式系统通过USB 接口与FPGA 通信,传输链路层数据,为保证数据传输的实时性,对链路层数据传输时间进行分析计算。

通过分析计算,MVB 相邻2 组主帧传输最短时间间隔为47 μs。因为在FPGA 端用于暂存1 组主从帧数据的RAM 容量为320 bits,为保证帧数据通过USB 传输的实时性,必须在47 μs 内将320 bits的数据传输完毕,则满足要求的MVB 最小传输速率为6.8 Mbps。对文中设计的USB 模块进行数据采集速率测试,经试验测试求得数据采集模块最大传输速率为26.7 Mbps,则该模块满足实时性要求。

2.2 MVB 链路层数据时序分析

MVB 数据时序分析程序完成的功能主要为:将存储在文件中的MVB 数据读出并进行整理;通过FPGA 封装后的MVB 数据格式,进行MVB 帧数据的识别,通过F 代码来判断过程数据和基本周期,并跳过从帧数据;使用KMP 算法解析出MVB周期轮询表,并将其保存到新的文件中。

(1)MVB 帧数据筛选和周期识别

MVB 报文经过FPGA 将其重新封装后传送至USB,其数据传输格式如图3 所示。

图3 USB 数据传输格式

由于数据在重新封装过后具有固定的识别码帧头,所以程序对一维数组read_buffer 使用strstr()函数检测“55AADD”字符串首次出现的地址,将其值赋给指针p。可以根据主帧的第1 位数据F 代码,即指针(p+8)的值来判断其数据类型。另外,为防止从帧数据中也含有连续的“55AADD”的数据导致strstr()函数误识别为帧头数据,程序在识别完一条报文并进行处理后会根据数据类型将指针p 跳过其从帧数据。而不同F 代码的MVB 报文长度又不相同[10],所以必须针对不同的F 代码来判断指针p 需要跳过的字符数。

本程序使用switch()选择语句,针对过程数据,对其主帧进行存储后再跳过相应的字符数,反之不进行存储直接跳过相应字符数。在跳过相应的字符数后,从指针p 的位置继续使用strstr()函数,来查找后续的帧头,直到其返回为空值说明报文识别完毕。

此外,利用一维数组counter 记录出现偶发相即非过程数据前的MVB 主帧的位置,以此来记录不同的基本周期中存在的主帧数目。识别过程数据主帧和MVB 基本周期的流程如图4 所示。

图4 识别过程数据主帧和基本周期流程

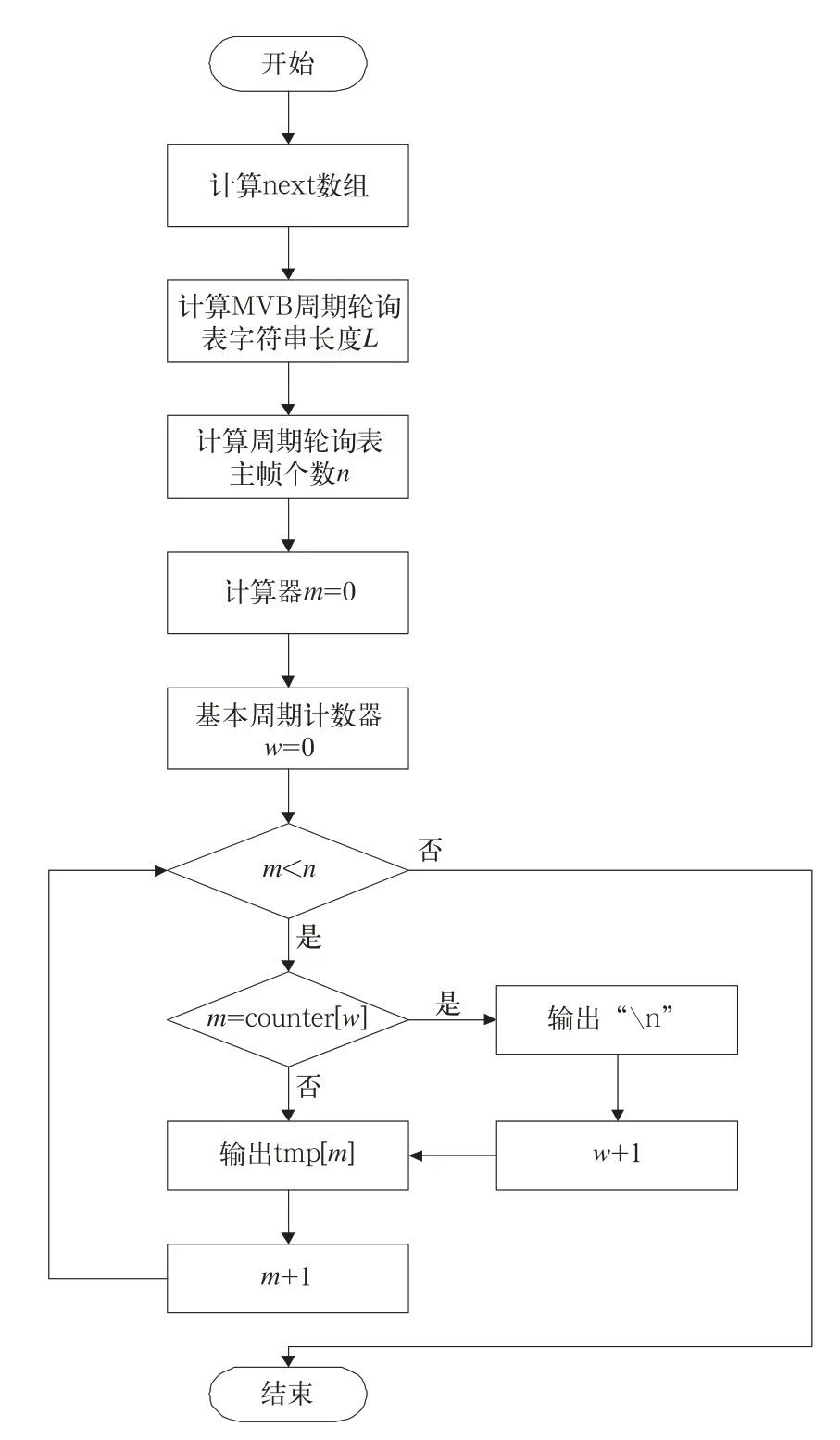

(2)基于KMP 算法的周期轮询表的解析

通过比较KMP 算法和暴风算法,文中选择效率更高的KMP 算法。对于KMP 算法的应用,其可以延伸到计算一组字符串的最小循环节的问题。而计算MVB 周期轮询表的本质就是计算MVB 过程数据的主帧数据的最小循环节。解析周期轮询表流程如图5 所示。

图5 解析MVB 周期轮询表流程

其中,通过将储存在二维数组tmp 中的MVB过程数据的主帧数据依次存储在1 个一维数组S中,对数组S 中的所有主帧数据进行一次遍历,来生成1 个关于数组S 的next 数组;并利用关于next数组的KMP 算法定理来计算一维数组S 最小循环节长度,即一维的MVB 周期轮询表的字符长度。

2.3 MVB 网络链路状态监视

由于列车运行环境复杂,导致网络故障原因很多,为了确定故障原因,首先应该对网络链路层数据进行采集和深度分析。文中选择丢包率和链路利用率作为反映MVB 网络链路状态的参数。丢包率是指测试中所丢失数据包数量占所传输的总数据量比值。链路利用率是指特定时间间隔内链路利用时长占总时长的百分比,反映信道平均被占用程度。MVB 链路状态量统计结构框图如图6所示,包括A 路解码模块、B 路解码模块和状态统计模块组成,根据不同的触发信号对1.5 s 内的不同状态量进行统计并保存。

图6 MVB 链路状态量统计

3 测试和验证

为验证MVB 数据实时采集功能能够正常稳定运行,以及链路层数据时序分析程序功能的正确性,在实验室环境下搭建测试平台,并通过实车采集的数据进行了测试试验。

3.1 MVB 数据实时采集功能验证

该程序功能验证试验是在实验室环境下,使用1 个主设备来发送主帧以及1 个从设备来响应该主帧,以此来模拟实际列车运行环境中MVB 总线上的数据情况。在总线上连接示波器观察其主帧数据,与嵌入式系统读到的数据和上位机接收到的数据做对比,以验证该程序功能正确实现。

该试验平台的实际搭建图如图7 所示。其中,主设备使用中央控制单元CCU,从设备为标准UIC 网关,嵌入式板卡镶嵌在MVB 协议分析装置上,嵌入式的宿主机和其上位机为同一台个人电脑。

图7 实际测试平台

从示波器中收到的MVB 波形数据如图8 所示,通过该波形可以读出主帧为“44 45”,而从帧数据为“00 01 00 01 01 69 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00”,其经过FPGA 封装过后为的数据为“55 AA DD 22 44 45 00 01 00 01 01 69 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00”。

图8 MVB 物理波形

(1)MVB 数据采集功能验证

为了验证程序通过USB 接口正确的采集到FPGA 封装好的数据,在程序中添加打印语句,在每次转码后都打印出转码后的数据,与FPGA 中读到的数据做比对,即验证该程序数据采集功能能否成功采集数据。嵌入式系统打印出读到的数据并显示在超级终端上如图9 所示,与上述示波器中显示的主帧数据和从帧数据一致。

图9 读取的数据

(2)数据流实时性验证

对于数据流实时性的验证,通过在上位机系统中使用Wireshark 软件对嵌入式系统发送的数据进行抓包,并对这些数据的时间进行分析,计算出其具体时延,以确定整个数据流的实时性。将整个数据读取、存储和转发设置为有限的50 次循环,查看Wireshark 抓包的时间与上次抓包的时间间隔,统计该时间间隔的平均值,以验证其符合实时性要求。使用Wireshark 软件抓包的结果如图10 所示,其总共抓取了50 次。

图1 0 Wireshark 软件抓包

3.2 链路层数据时序分析功能验证

试验使用列车实际运行过程中采集并经过FPGA 封装后的一段数据来对该程序功能进行验证。首先我们先人工分析该段数据中主帧、基本周期和周期轮询表,之后与程序分析出的各数据进行比较,以验证该程序各功能的正确性。

该数据中1 个宏周期的MVB 链路层数据如图11 所示,其中蓝色标注为每个数据帧的帧头,波浪下划线的部分为过程数据报文;红色标注为过程数据的主帧,双下划线的部分为非过程数据报文。

算例所形成的MVB 周期轮询表如图12所示。

图1 2 周期轮询表结果

图1 1 宏周期数据分析

(1)过程数据主帧与基本周期的识别功能验证

该功能的验证方法是对读取到主帧数据的二维数组tmp 进行打印,以及计数器counter 记录到基本周期数据之间的断点时,在超级终端中的换行输出。运行数据分析程序后超级终端的打印信息如图13 所示,由图13 可知该程序成功识别了6 个宏周期中所有过程数据的主帧,且基本周期的拆分也完全正确,此试验验证了该功能的可实现性。

图1 3 过程数据主帧和基本周期识别

(2)MVB 网络链路状态监视功能

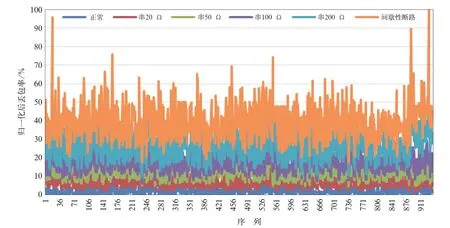

选取丢包率作为反映链路状态指标,取正常通信,串联阻抗20、50、100、200 Ω,间歇性断路等6种工况下1 000 组丢包率特征量指标,取均值后做归一化处理。随着串联阻抗增大,物理层波形恶化愈加严重,丢包率也有明显的增大趋势如图14所示。由此表明,该功能能够准确反映MVB 网络链路状态,为MVB 故障排查提供依据。

图1 4 不同工况丢包率统计图

4 结 论

为保障MVB 数据传输的可靠性和实时性,文中设计了对总线信号不会造成影响的基于嵌入式的MVB 数据监视软件及数据分析软件,实现了对总线数据的实时监控以及时序分析。文中所设计的程序能够为故障分析提供直观可靠的支持,对相关故障预测与诊断具有一定借鉴意义。