64G PCIe6.0产品设计挑战及实现

2022-06-28李明

李 明

(立讯技术有限公司,广东东莞,523808)

1 引言

PCI Express技术经过二十多年的发展,已经成为一种普及的I/O技术。PCI Express®(PCIe®)6.0利用PAM-4编码技术,包括低延迟前向纠错(FEC)和其他机制,将使数据速率加倍,达到64 GT/s,同时保持与前几代产品的向后兼容性,并提供能效和经济高效的性能,PCIe 6.0将在2021年发布。PCIe 6.0主要应用于满足人工智能、机器学习、网络、通信系统、存储、高性能计算等热门市场的需求。

2 PCIe协议介绍

在过去的几十年里,系统性能的增长与半导体技术的发展密切相关。随着半导体制造特征尺寸接近其极限,封装级集成对于未来系统扩展变得越来越重要,而系统扩展又高度依赖于I/O带宽的扩展。

图1 PCIe协议发展历程及行业带宽需求

自2003年首次推出以来,PCI Express(PCIe)经历了五代发展,从2.5Gbps/通道发展到5Gbps(v2.0)和8Gbps(v3.0),再到16Gbps(v4.0),以及2019年发布的32Gbps(v5.0)。最近,业界一直在寻求解决方案,以进一步将PCIe I/O标准扩展到64Gbps(v6.0)的第六代,以满足不断增长的系统带宽需求。而在32Gbps及以上时,信号完整性成为一个主要障碍,尤其是PCIe连接器是为前几代较低的运行速度而设计的,标准PCIe连接器沿信号路径会产生阻抗变化,而且由于连接器结构内的阻抗不连续性也会产生谐振;随着信号数据速率的提高,这些问题变得非常重要。因此,业界正在探索替代性的连接器设计解决方案,但是这些替代解决方案与现有的封装外形和子卡设计不能向后兼容,往往会提高PCIe连接器的成本,因此我司将致力于在原基础结构上进一步探索,把CEM连接器平滑升级到PCIe6.0。

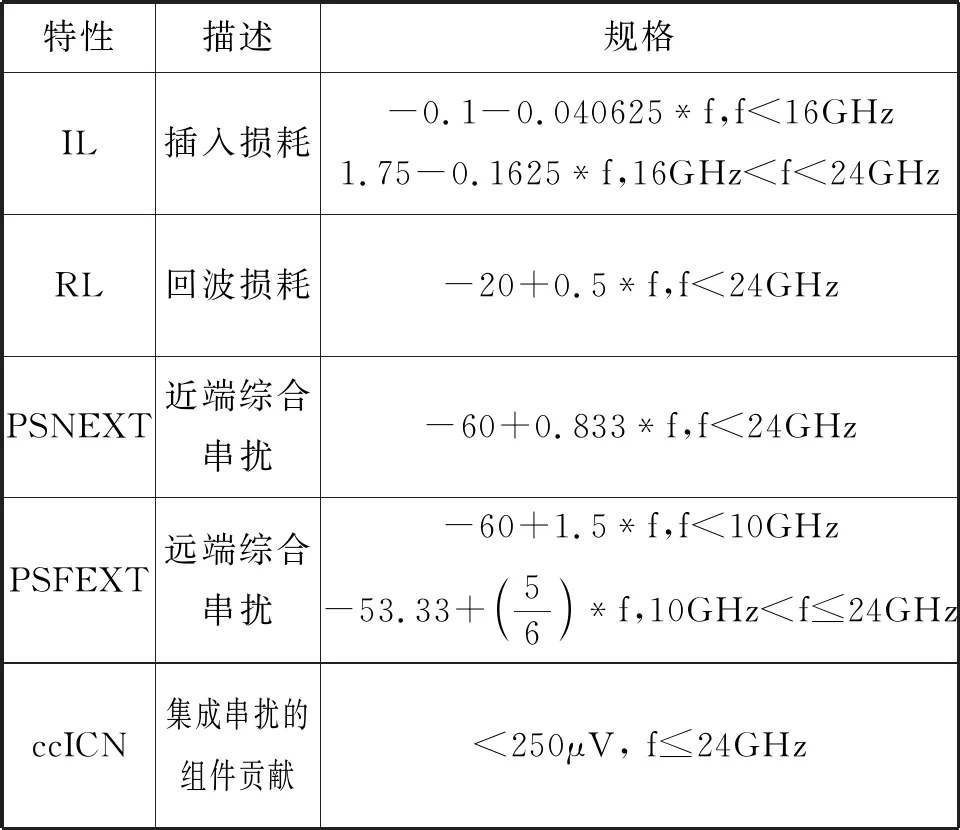

现阶段PCIe6.0完整版规范尚未编写完成,此处简要解析于2021年8月发布的0.5版草案,对应的CEM规格线如下:

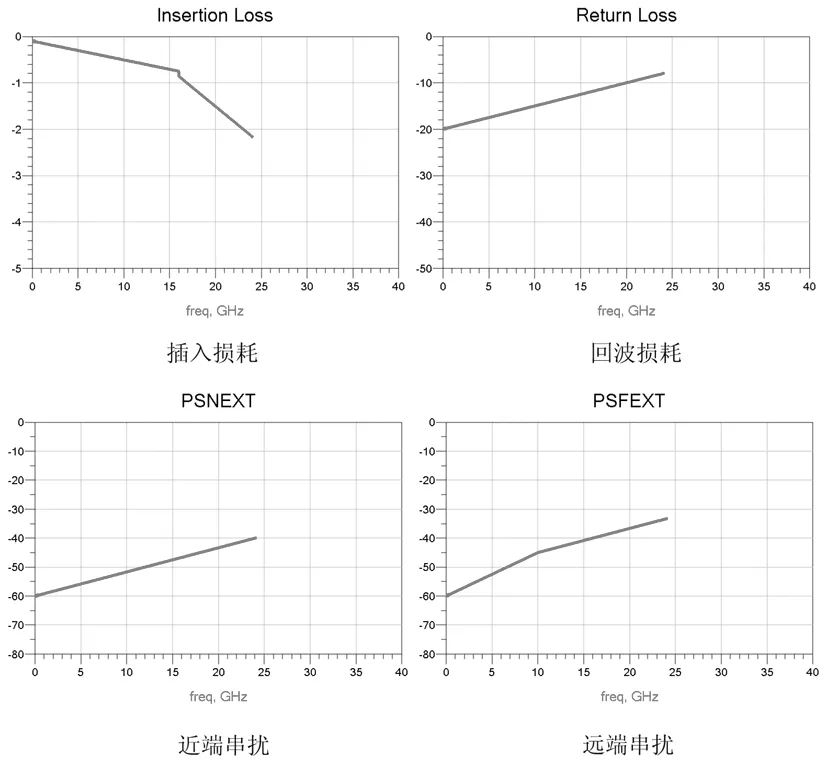

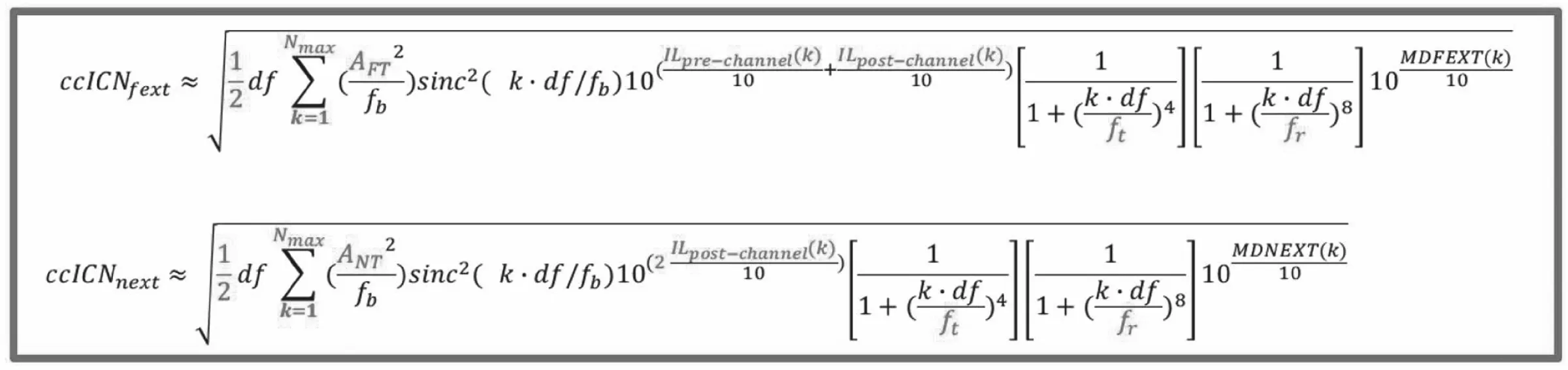

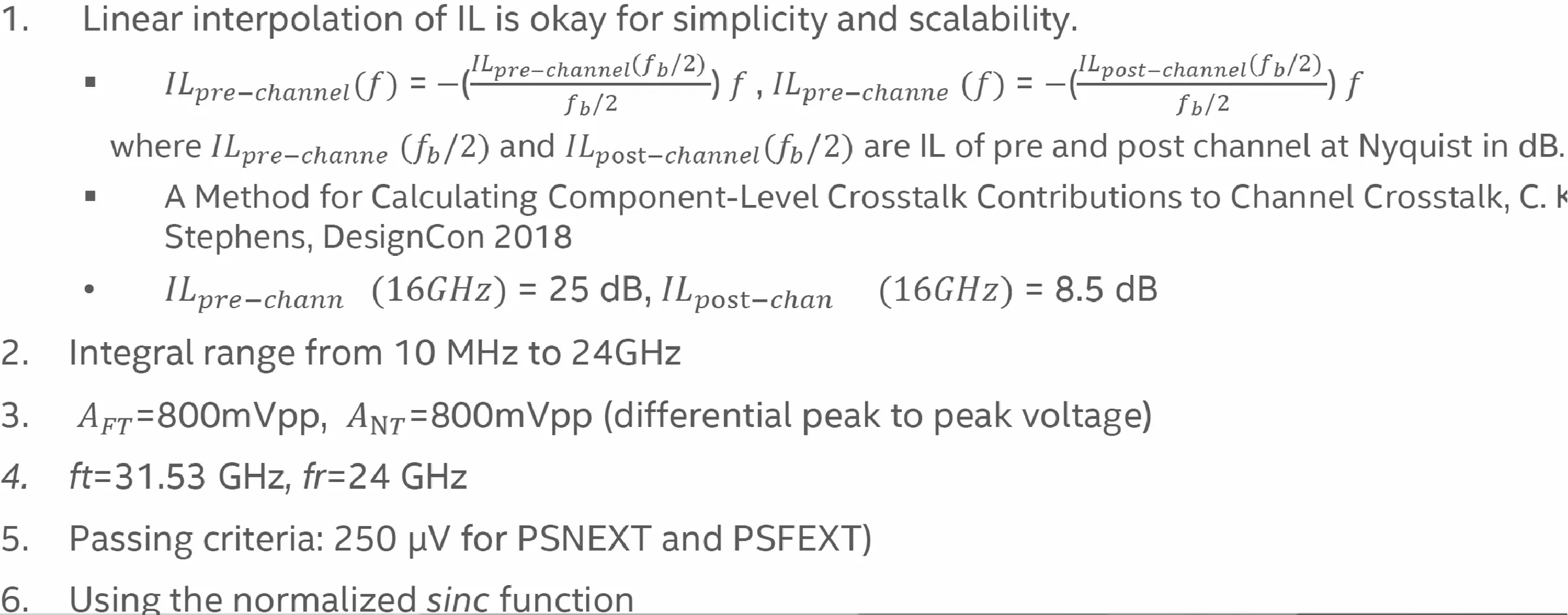

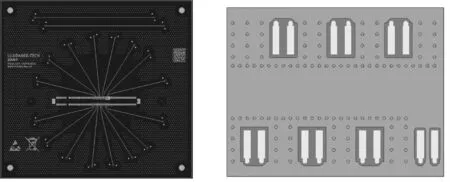

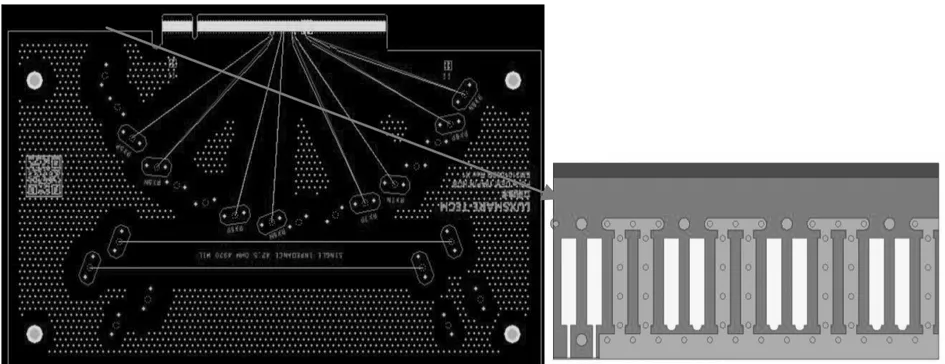

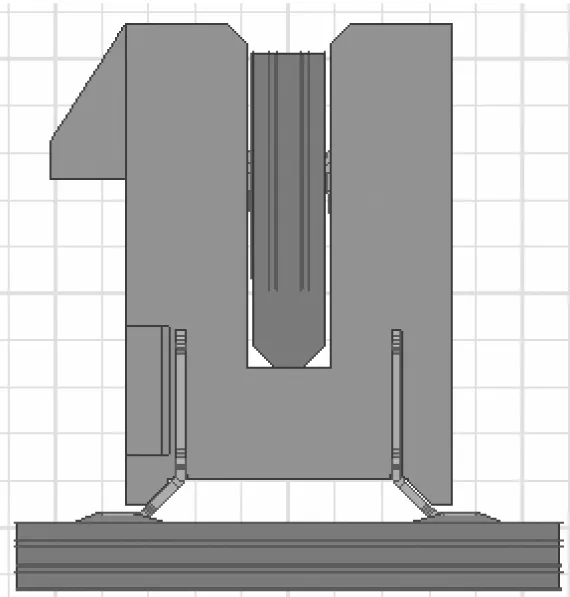

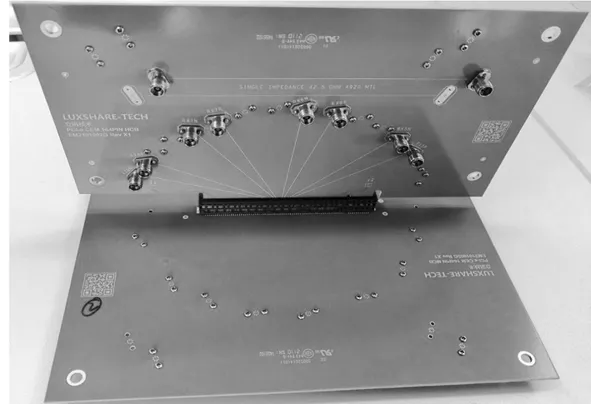

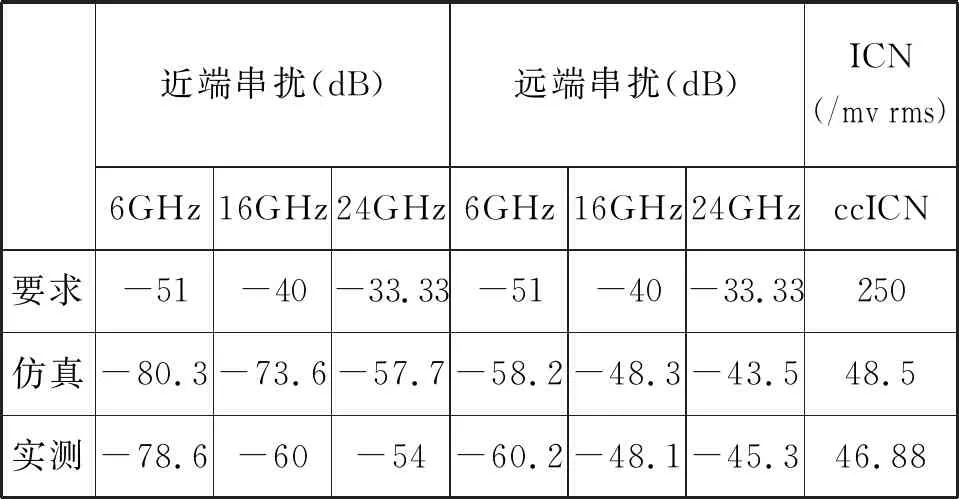

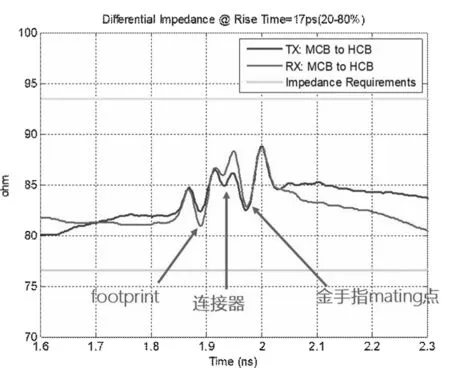

特性描述规格IL插入损耗-0.1-0.040625*f,f<16GHz1.75-0.1625*f,16GHz 图2 PCIe 6.0 V0.5草案规范 ccICN计算公式: 条件设置如下: 其中,ccICN是新的指标规范。ccICN全称是Component Contribution with Integrated Crosstalk Noise,通常单独用频域指标来定义元件的串扰是不够的,在元器件不能完全满足频域指标的情况下,引入ccICN指标可以更好地在系统全链路中评估元器件的影响。 连接器作为链路中的关键部件,它的好坏往往直接决定了无源通道的性能,连接器的结构决定了它处于一个相对开放的空间,要想在芯片到芯片通道上实现一个阻抗受控、串扰较小的通道,连接器无论是设计还是验证都非常复杂。 连接器的开发与验证需处于整个产品开发过程的前期阶段,确保在源端就解决掉潜在的风险:1.插损要求在16GHz前小于0.75dB,24GHz前小于2.16dB;2.CEM连接器的阻抗设计目标为85+/-5ohm,其重点在于控制力臂和端子在housing里面的尺寸;3.串扰方面的要求也很高,需要使用桥接抑制谐振。最终经过使用电磁仿真软件HFSS进行仿真设计优化,使所有电性能满足PCIe6.0规范推荐的mated连接器测试要求。 PCIe6.0对于插损和串扰的要求都更高,对连接器的阻抗一致性和串扰性能提出了更高的要求,随着速率的提高,高速链路的前仿真变得尤为必要,通过前仿真得到电路设计的约束规则,在约束的驱动下进行PCB的布局布线,同步进行的后仿真验证设计的可行性,可大大降低产品设计失效的风险,节约产品开发时间。 首先,需确定PCB板材的选用和层叠的设计,根据自身设计能力和经验选择性能最高的设计方案,进一步对测试板进行SI性能的仿真优化。连接器与测试板直接接触的地方存在两个最大的阻抗不匹配点,一是连接器footprint点,二是金手指同连接器端子mated点。由于系统阻抗按85ohm设计,通过仿真将footprint点和mated点的阻抗都优化到80ohm以上(上升沿17ps)。 首先,PCB材料采用稳定的松下Megtron7G,铜箔类型选用HVLP,8层板设计,层叠如下: 图3 层叠设计 其次,在玻璃布选择类型上,选用1078和3313等类型扁平玻璃布,避免产生玻纤效应,造成skew不良,进而影响测试出来的结果,下面是玻璃布的示意图: 1078扁平玻璃布 1080非扁平玻璃布 接下来是板子的具体设计部分,主板差分阻抗设计为85ohm,走线2.5inch。在设计方面,需要在footprint的GND pad部分打孔,以减小板子引入的串扰。如下是主板的整体设计图和footprint细部仿真放大图: 图5 主板设计 子卡差分阻抗设计为85ohm,走线2.5inch。在设计上,需要在金手指头部打孔,减少金手指引入的串扰。如下是子卡整体设计图和金手指部分细部仿真放大图: 图6 子卡设计 最后通过电磁场协同仿真,将各单点仿真参数和线材实测参数级联成完整的链路进行仿真验证。 图7 立讯 PCIe6.0 CEM连接器仿真示意图 下面是仿真出来的插损、回损和串扰的结果。 图8 立讯 PCIe6.0 CEM连接器仿真性能 图9 立讯 PCIe6.0 CEM连接器测试夹具 插入损耗 在PCB回板后,焊上连接器进行配对测试(见下图)。在测试方面,PCIe6.0需要采用4端口的高带宽网分进行测试,我司采用是德的4端口67G带宽网络分析仪N5247B进行测试,结果显示立讯技术设计的CEM连接器满足PCIe6.0的草案规范要求。 ccICN计算结果,满足250μV的指标要求: 图11 立讯 PCIe6.0 CEM连接器测试性能 仿真和测试对比结果: 表1 立讯连接器仿真和实测1 表2 立讯连接器仿真和实测2 阻抗测试图,整体满足85+/-5ohm的设计要求: 图12 阻抗测试图 本文通过介绍PCIe6.0最新的发展路标和草案规范,了解业界的最新发展方向,并通过介绍CEM连接器的产品仿真设计和验证过程,对于如何优化连接器进行了可行性探讨。在64Gbps的速率下,插损和串扰都比PCIe5.0连接器有一个很大的提升,希望能给设计工程师提供参考和优化的方向。

3 64G PCIe6.0产品设计挑战及实现

3.1 CEM连接器设计

3.2 测试板仿真设计

3.3 连接器+测试板仿真设计

3.4 测试验证

4 结语