DRAM的现状及发展方向

2022-06-18任智源杨伦柴凯中

任智源,杨伦,柴凯中

湖北师范大学先进材料研究院,湖北黄石,074000

0 引言

动态随机存取存储器(dynamic random access memory, DRAM)广泛应用于云服务器、电脑、手机等电子设备,在内存计算领域展现出延迟低、带宽高、运算速度快、集成密度大和生产工艺成熟等特点[1-2]。过去几十年中,依靠生产工艺的不断微缩和集成度的持续提高,内存芯片上存储单元的数量呈指数式增长。现在,20nm是业界比较成熟的节点,而基于技术节点1x(16~19nm)和1y(14~16nm)的产品已在各大DRAM制造商中投入生产。DRAM的进一步发展需要克服10 nm以及更高技术节点带来的限制,科技创新变得比以往任何时候都更为关键[3]。目前,三星(Samsung)、美光(Micron)和海力士(SK Hynix)三家主要厂商已经发布了D1z(13~15nm)和D1a(11~13nm)技术,并应用于DDR4、DDR5和LPDDR5产品中。在D1z中,三星采用了EUV光刻技术,而美光和海力士引入了基于ArF-i的双图案技术(DPT)工艺。预计到2030年,这些厂家将推出1δ、0α和0β等制程更小的DRAM[4]。

基于德国DRAM制造商奇梦达(Qimonda)的技术和专利,长鑫存储(CXMT)在合肥建成一座12英寸晶圆厂,开启了DRAM芯片的研发之路。2019年9月,长鑫正式投产8GB DDR4 DRAM模块,成为中国第一个自主研发DRAM芯片的厂家,并能够与国际主流技术相媲美[5]。目前,长鑫正在开发D1x和D1y制程的产品。

1 工作原理

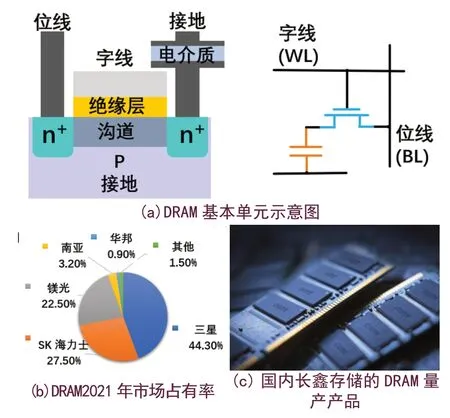

典型的DRAM结构单元由1个场效应晶体管和1个存取电容器(1T-1C)组成,如图1(a)所示。接入晶体管的栅极端连接到字线(WL),漏极端通过位线触点(BLC)连接到位线(BL),另一端通过存储节点(SNC)连接到电容器。将接入晶体管作为开关,可以使电容器存储正/负电荷,从而存储比特数据。当晶体管关闭时,会向电容器上施加工作偏压。当晶体管被接通时,存储的电荷流入位线,产生一个电位变化,可以被连接到位线的放大器放大和检测,实现存储器数据信息的读取。

图1 DRAM结构单元

这种基本结构简单小巧,理论上可以无限扩展,但由于实际中存在多种漏电电流,限制了DRAM的数据单元规模。主要漏电电流源有以下几个:①来自存储节点的漏电电流;②接入晶体管中栅极导致的漏电电流;③存储节点和位线间截止电流带来的漏电电流;④存储节点中氧化物和电容器带来的漏电电流。所以DRAM电容器上的电荷并不稳定,随着时间推移会逐渐失去明确的电荷状态,令数据无法永久保留。因此,DRAM被认为是易失性存储器。为了解决这个问题,DRAM的内存会被周期性刷新(根据JEDEC规范,典型刷新时间为64ms),然后读取内存内容并将其重新写回。在动态随机存取存储器中,名词“动态”(Dynamic)就是这个意思。

2 解决短沟道效应

从电学角度来看,单元尺寸缩小导致沟道长度减小,进而减小阈值电压,出现短沟道效应,越来越严重地影响了DRAM的性能。带来的问题有以下几点:①漏致势垒降低效应,在较高漏极电压下,晶体管的源漏端耗尽层接,电场穿通,降低势垒致使阈值电压下降;②载流子迁移速率逐渐饱和导致漏端饱和电流降低;③强电场下载流子在散射过程中获得高能量,成为热载流子并有可能被捕获在MOS晶体管的栅极电介质中,可以永久改变晶体管的开关特性。

然而DRAM需要较高的ION/IOFF比[3],其技术规格与高性能逻辑器件不同,要求低泄漏率以防止电容器放电、高导通电流以在短时间内完成数据读写。截止电流由于短沟道效应而增加,而导通电流则受限于有效宽度而减少。此外,沟道掺杂浓度随尺寸缩小而增大,电场和漏电电流增加,引起保留时间减少。

克服短沟道效应的一个简单而有效的方法是增加沟道长度。为了实现这一目标,从平面结构转向了更复杂的三维结构,未来可能实现完全的垂直集成。

(1)平面非对称结构:120nm技术节点引入的关键创新是不对称连接[10]。此时,接入的晶体管仍是平面型,源极和漏极结剖面被独立优化、分级设计,以减少电场,将漏电电流降至最低,增加数据保留时间,抑制短沟道效应。

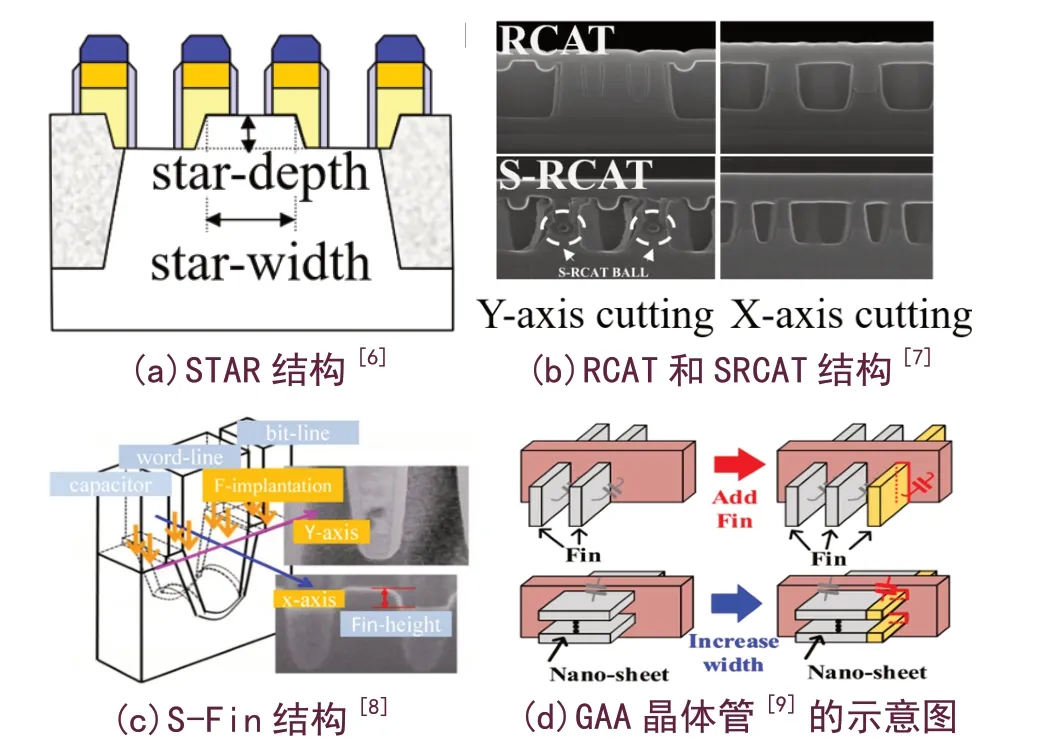

(2)阶梯式栅极不对称结构(step gated asymmetric cell transistors, STAR):在利用三维结构向更长沟道发展的过程中,2005年,一种新型的STAR结构被提出[6]。其沟道长度的增加是通过将沟道的一半凹陷并形成非对称结构来实现(如图2(a)所示)。与传统平面晶体管相比,STAR表现出了经过明显改善的电学特性,如击穿电压BVDS、结泄漏和字线电容(CWL)。

图2 创新的DRAM结构

(3)凹槽沟道栅晶体管(Recess-Channel-Array-Transistor, RCAT):RCAT是通过在刻蚀的Si表面上生成氧化物获得凹沟道,以增加有效沟道长度,同时不影响横向封装,如图2(b)所示。在此基础上引入球形凹槽沟道阵列晶体管(S-RCAT),进一步增加了沟道长度[7]。

(4)鞍形鳍片晶体管(Saddle Fin, S-Fin):S-Fin是将鳍式场效应晶体管(FinFET)与凹槽沟道阵列晶体管(RCAT)相结合得到的,如图2(c)所示)。通过干法蚀刻技术简单集成,从而获得更理想的阈值电压。与RCAT相比,S-Fin显示出了更优秀的电学性能,改进了短沟道效应、驱动电流和刷新特性。

(5)全包围栅(Gate-All-Around, GAA)晶体管:GAA晶体管提供了一个在栅极下形成的四面通道,而构成沟道的纳米片在垂直方向上堆叠,如图2(d)所示。与Fin相比,GAA在同等体积下却能拥有更大的有效沟道长度,从而在系统层面上获得更高的集成度[9]。

3 无电容结构发展

对于10nm和更高级别的DRAM设计,需要从提高性能、减小体积、降低成本三个方面持续改进,而DRAM单元仍然面临着诸多难题。

(1)刷新时间不足:即便是在正常工作期间,由于电容器上的电压通过寄生电阻泄漏,DRAM单元也会定期丢失其信息。这意味着单元格中的数据需要平均每64ms刷新一次,未来目标是设计刷新时间更长的DRAM。

(2)存在破坏性读取机制:传统设计中遵循的读取机制涉及电容器对位线的充电。由于尺寸越来越小,邻近的单元之间很容易产生电磁干扰,导致电磁耦合效应,在读取数据时有概率丢失数据。这意味着如果没有某种刷新机制,将无法在多个周期中从单元读取数据,使得架构复杂化。

(3)电容器可靠性低:更小的电容器可存储的电量更为有限,而漏电电流更高,所以整个系统需要更频繁地刷新来维持数据的正确性与完整性。如此一来,存储系统的性能、功耗与稳定性势必有所降低[11]。

针对这些问题,DRAM的设计前景可分为工艺、材料、电路设计等方向,比如对EUV技术的大规模应用、柱状电容器、超薄的高介电常数材料的研究、Row Hammer效应的改善以及无电容1T DRAM的开发等。为了减少DRAM单元的体积,使集成度进一步提升,无电容结构的DRAM设计受到科研人员和产业界越来越多的关注。

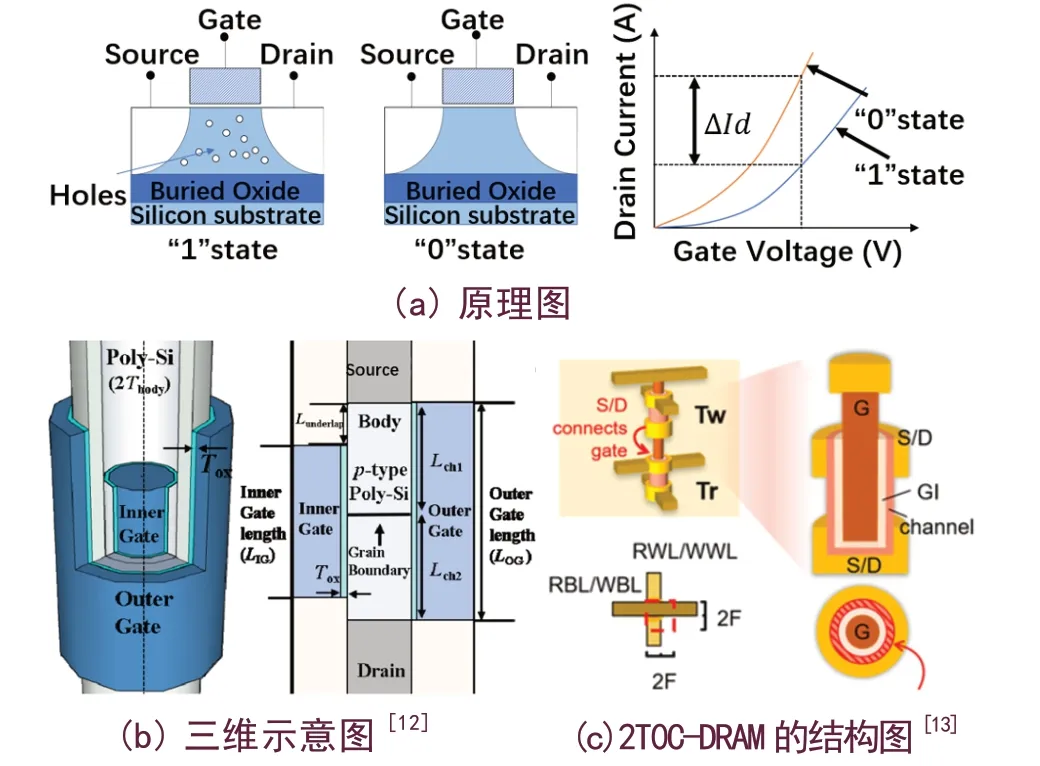

图3(a)展示了含有1个晶体管的无电容DRAM(1T-DRAM)单元的工作原理。源极设置为0V,漏极连接到位线,栅极连接到字线。随着阈值电压的变化,DRAM单元通过检测漏极电流,来分析出多数载流子(空穴)是否聚集在浮体中。若浮体漏结上的正向偏压将多余的空穴扫出体外,阈值电压变高,单元状态可以看作是“0”;另一方面,若浮体中存在多余的空穴,阈值电压下降,单元状态可视为“1”[12]。这样,在线性电流区域就可以检测到“1”和“0”状态之间的漏极电流差,信息就被存储在浮体中。在刷新间隔期间,1T-DRAM单元能够实现无损读取操作,不会因为电离碰撞电流而改变空穴的数量。

图3 1T-DRAM单元

Jin Park[12]等人采用计算机辅助设计(TCAD)模拟技术,模拟设计了一种基于晶界多晶硅纳米管结构的1T-DRAM,如图4(b)所示。该DRAM结构单元由外栅极(OG)和内栅极(IG)包围了整个沟道区域,能有效地控制沟道和浮体区的电荷,展示出经过改进的电学性能。内栅极有一个不对称结构,带有一个underlap(Lunderlap)区域,以降低间接复合(Shockley-Read-Hall, SRH)的复合速率。在1T-DRAM中,写入“1”操作通过OG和IG之间的带间隧穿来执行。与传统的纳米线器件相比,OG和IG可以施加不同的电压,有利于作为存储器使用。

Duan[13]等人首次提出了一种用于高集成度和长保留时间的2T0C DRAM,该器件具有新型的垂直沟道环绕(CAA)结构,由InGaZnO(IGZO)FET组成,如图4(c)所示。水平方向上,栅极被栅极绝缘体和IGZO沟道依次包围。源极和漏极由绝缘层垂直分隔,形成金属/绝缘体/金属(MIM)结构,其中下部读取晶体管的栅极直接连接到上部写入晶体管的源极/漏极。VDS=1V时的测试结果表明,50nm沟道长度的CAA-IGZO FET实现了ION>30μA/μm以及IOFF低于1.8×1017μA/μm。该结构单元的保留时间长达300s,为设计超低刷新频率的低功耗DRAM提供了新的技术方向。

4 结语

本文回顾了DRAM的传统结构,介绍了行业为解决工艺制程微缩所带来的各种各样的问题,特别是针对短沟道效应所提出的各种增加有效沟道长度、提高结构集成度的方案。值得注意的是,无电容设计中的读取机制都比传统设计的读取机制更为复杂。迄今为止,综合考虑生产工艺、良品率、成本等多方面因素,使用最为广泛的仍然是传统的1晶体管1电容器的DRAM单元。