基于薄膜IPD 工艺的N77 频段多零点带通滤波器设计

2022-06-14王浩威傅肃磊王为标吴浩东

王浩威 ,郭 瑜 ,傅肃磊 ,王为标 ,吴浩东

(1.江南大学 物联网工程学院,江苏 无锡 214122;2.无锡市好达电子股份有限公司,江苏 无锡 214124;3.南京大学 物理学院,江苏 南京 210093)

无源微波器件是微波模块的重要组成部分,而滤波器作为无源微波器件的关键部分,对整个微波收发系统的性能与体积有决定性影响。在3G/4G 时代,基于声表面波和体声波原理的声学滤波器由于其高选择性、价格低廉、尺寸小等优点在移动终端市场中占主导地位。随着5G 通讯时代的到来,高频宽带滤波器的市场需求迅速上升,而传统的声学滤波器受器件压电材料声速小、机电耦合系数低的限制,难以满足需求[1]。目前,基于薄膜IPD 工艺的滤波器因具有高频、大带宽、体积小、易于集成等特点[2-4],成为当前研究的热门方向。

薄膜IPD 工艺具有加工精度高、均一性好等优点,使得滤波器能在满足带宽需求的同时极大地缩小尺寸。然而,IPD 器件的膜层通常很薄,并且受半导体衬底的导电性影响,滤波器电感Q值较低,整体损耗较大。因此,许多学者针对如何降低IPD 器件损耗在材料、工艺、电路结构等方面进行了探索。Zuo 等[5]提出将IPD 电路与声学谐振器相结合,通过使用更少的LC 元件来增大带宽、降低损耗,但实验模型过于理想化,并且损耗性能改善不显著。Wu 等[6]应用高Q值非对称差分电感和空气桥增强电容来提升电路性能,但器件制备流程复杂、加工难度大。Chen 等[7-8]采用GaAs 作为衬底材料,器件损耗有所改善,但GaAs IPD 工艺通常采用Au 或Au/Cu 作为金属材料,工艺成本太高。因此,如何获得低损耗、低成本的大带宽薄膜IPD 滤波器,仍是一个亟待解决的问题。

针对上述问题,本文利用PCB 基板中金属膜较厚、层数多、便于设计高Q值电感的优点,将以往IPD 滤波器的主谐振回路平面螺旋电感改为三维结构电感形式放置在PCB 基板内,大幅提高电感Q值,降低器件损耗。将薄膜IPD 技术与PCB 技术二者优势相结合,还能减小电路面积,降低器件成本。此外,通过引入外部串联电路和源负载耦合结构拓宽了通带带宽,并产生了三个带外零点来提升带外抑制。最终制备了一款工作在N77 频段的大带宽、多零点带通滤波器,并进行了实际测试。

1 理论与设计

1.1 电路结构分析

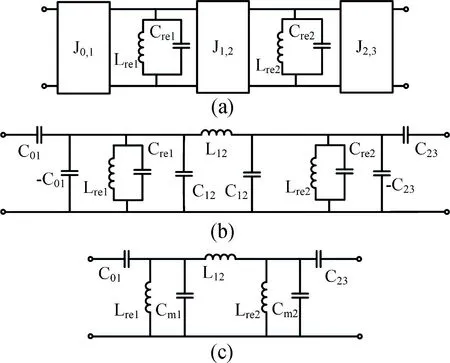

为得到高性能滤波器,本文在二阶带通滤波器电路基础上进行结构变换,具体变换过程如图1 所示。图1(a)为由两个谐振回路、三个导纳逆变器组成的二阶带通滤波器等效电路。根据导纳逆变器原理[9],在窄带近似的情况下,使用电容电感网络对逆变器进行等效变换,得到图1(b)所示电路。针对此时出现理论负值电容的情况,可通过相邻的正值电容并联消除,得到图1(c)所示电路。值得注意的是,在窄带近似的情况下,图1(a)~(c)电路结构是等效的,图1(c)等效电路局限于窄带滤波器。

图1 带通滤波器等效电路。(a)采用导纳逆变器;(b)使用等效电路替换逆变器;(c)合并并联电容Fig.1 Equivalent circuit of the bandpass filter.(a) A bandpass filter circuit with admittance inverters;(b) A bandpass filter circuit with admittance inverters replaced by equivalent circuit;(c) A bandpass filter circuit after combining shunt capacitors

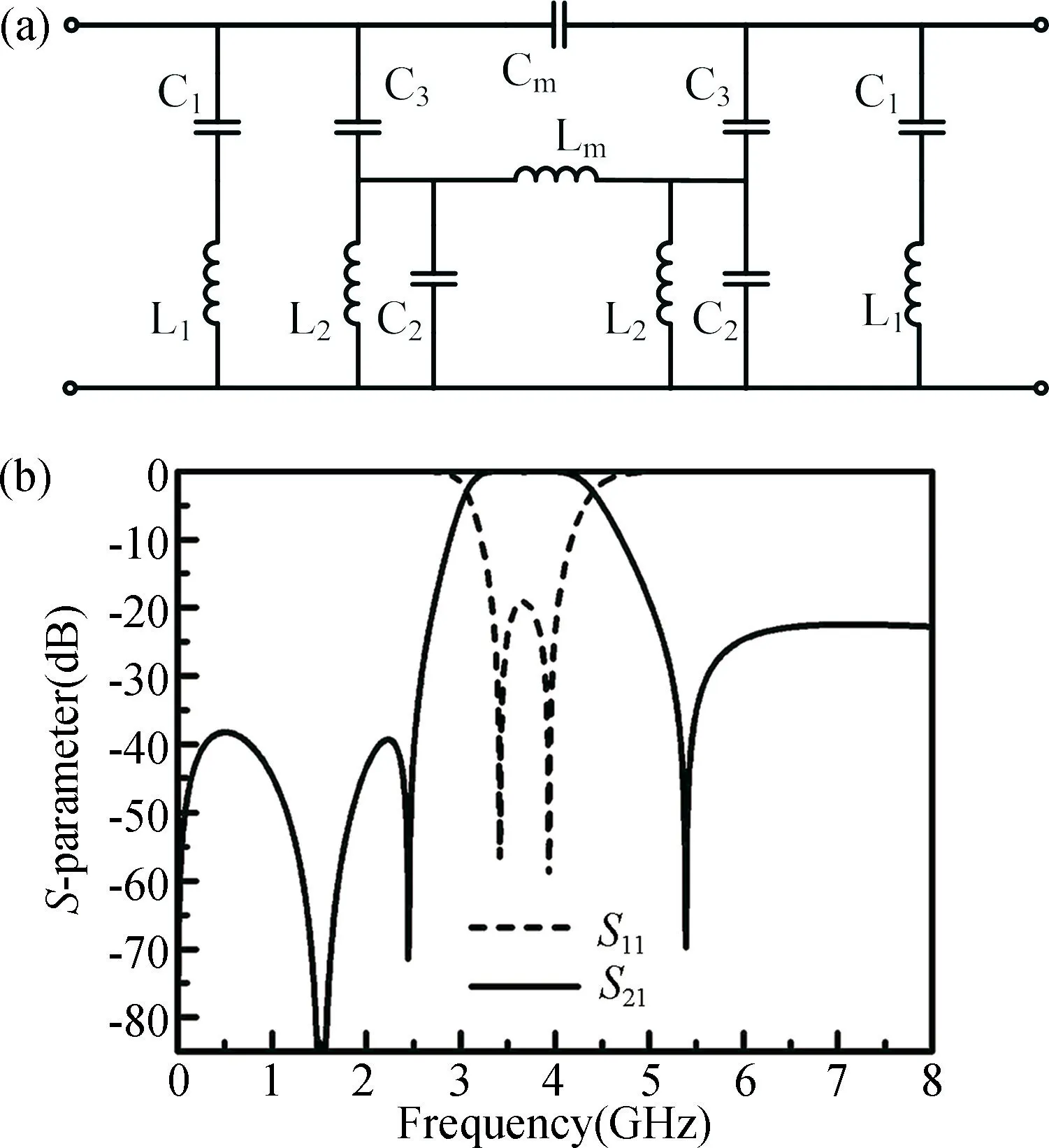

为了实现大带宽滤波器,本文在电路两侧各级联一个串联电路L1和C1,起到拓宽通带、调节带内平坦度的作用。同时,级联串联电路在通带左侧位置形成了一个传输零点。此外,为提高滤波器选择性,本设计通过引入源负载耦合电容Cm,在通带两侧各增加了一个传输零点。最终带通滤波器等效电路结构如图2(a)所示,元件参数如下:L1=2.95 nH,L2=0.47 nH,Lm=1.6 nH,C1=3.7 pF,C2=4.22 pF,C3=0.93 pF,Cm=0.01 pF。计算的电路频率响应如图2(b)所示。

图2 (a) 带通滤波器原理图;(b) 频率响应Fig.2 (a) Schematic of the proposed bandpass filter;(b) Frequency response of the bandpass filter

1.2 高Q 值电感和电容设计

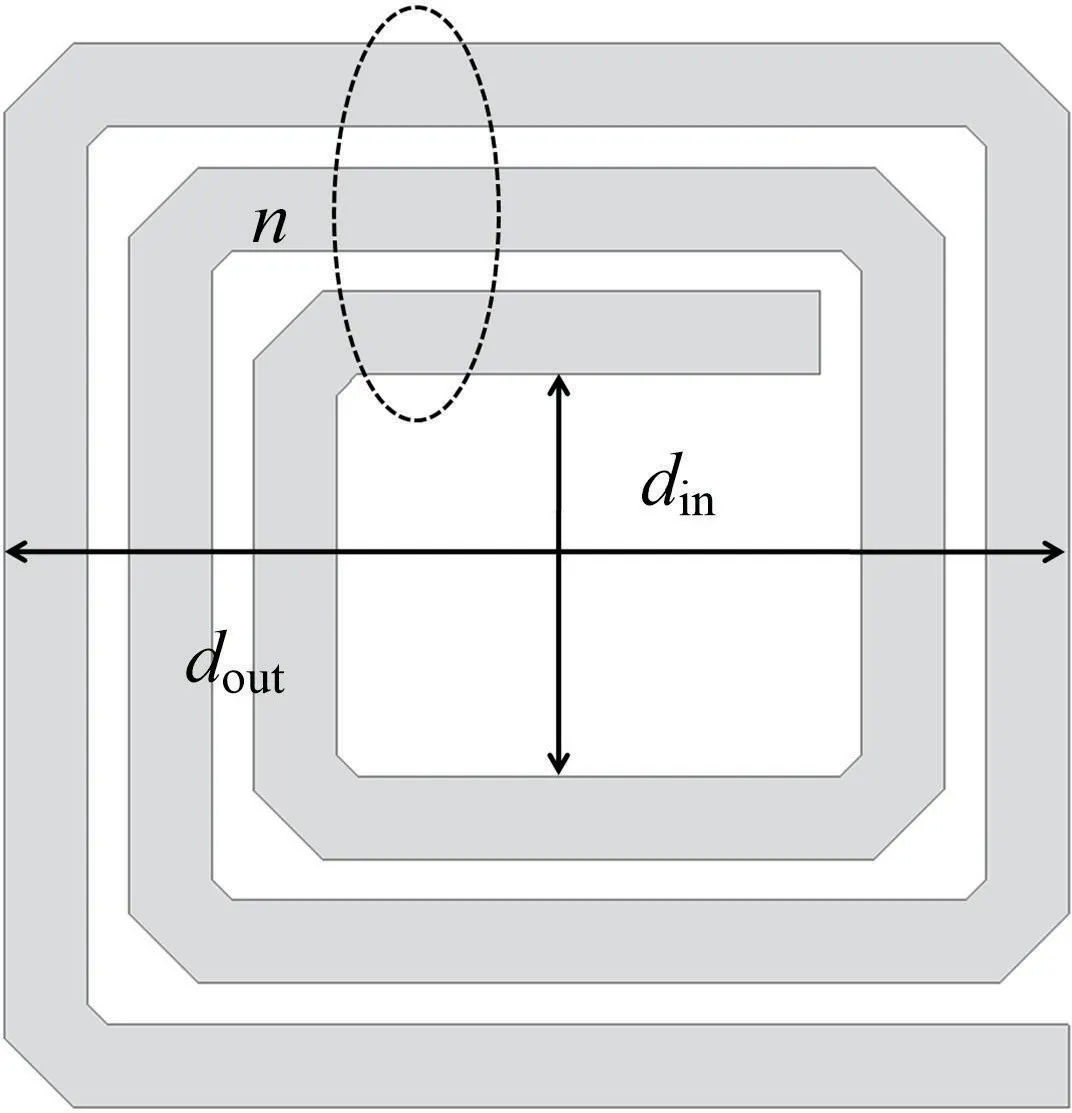

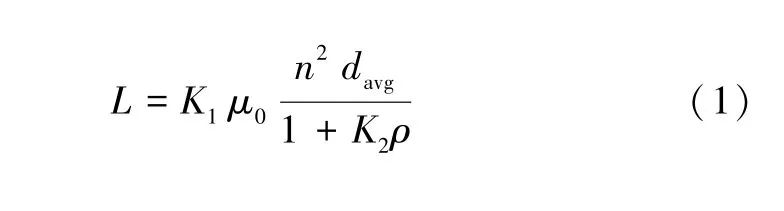

与传统LC 滤波器不同,IPD 工艺集总滤波器的电感大多为平面螺旋电感,其电感值与其几何形状相关,如图3 所示。对于四边形平面螺旋电感,可运用下述公式大致计算[10]:

图3 平面电感结构Fig.3 Structure of the planar inductor

式中:K1和K2为固定系数;n为匝数;ρ为填充率;davg代表的是内径din和外径dout的算术平均值。

其中,填充率ρ的计算公式为:

方形电感器的固定系数为K1=2.34 和K2=2.75。平面电感的品质因数一般只能达到30 左右,且自谐振频率较低。当平面电感作为主谐振电感时,将严重影响高频波段滤波器的带内特性和带外抑制。

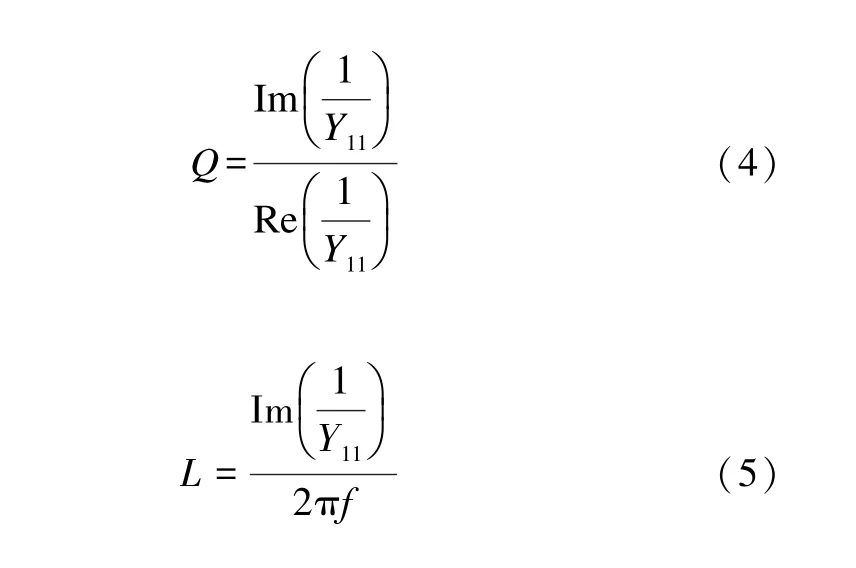

为提升电路损耗性能,本文将主谐振电路的电感与其余电感分开设计。鉴于PCB 基板金属厚、层数多、成本低,提出将主谐振电感以三维电感的形式设计在基板内,以提高电感Q值。如图4(a)和图(b)所示,两个三维电感同向放置,并在电感四周设置一圈金属柱,以避免引入板间寄生电容影响滤波器的整体性能。进一步地,腔体式的结构设计能将磁场能量束缚在金属柱范围内,也起到屏蔽的作用,避免外部电路带来不必要的耦合。其余旁路电感以平面电感形式集成在硅基芯片上,硅片阻值为5000 Ω·cm,金属厚度为4.5 μm,具体电感尺寸可通过公式(1)~(3)进行计算。

使用电磁仿真软件进行建模仿真,可以得到准确电感值,电感特性可以通过Y参数计算获得:

仿真得到的三维电感特性如图4(c)所示,该电感在3.7 GHz 时Q值大于100,自谐振频率大于20 GHz,比传统的平面螺旋电感具有更高的Q值和更宽的频率使用范围。

图4 (a) 电感三维图;(b) 俯视图,单位:mm;(c) 电感值与Q 值随频率变化曲线Fig.4 (a) 3-D view of inductor;(b) Top view of inductor;(c) Dependence of inductance and quality factor on frequency

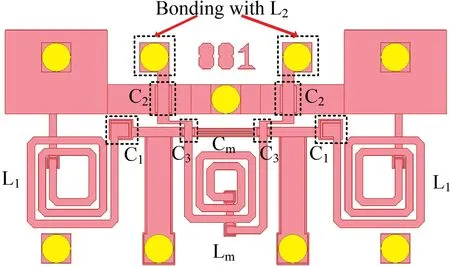

使用薄膜IPD 工艺加工薄膜介质,能够提高单位电容密度,在小区域内满足电路需求。如使用SiNx作为MIM 电容的介质材料,当介质厚度为0.1 μm 时,单位电容密度可以达到600 pF/mm2,电容Q值高于500。然而,由于介质厚度过薄,MIM 结构难以满足0.1 pF 量级电容的精度需求。故采用叉指电容的结构进行小电容设计。叉指电容的指条宽度为5 μm,指间间隙为5 μm,金属厚度为2 μm,可以通过改变指条对数精准控制电容大小。如图5 所示,电路结构与图2(a)电路相对应,C1、C2、C01和C23采用MIM 电容结构,Cm采用叉指电容结构。

图5 滤波器芯片结构Fig.5 Configuration of the proposed filter chip

1.3 基板与芯片的实现与结合

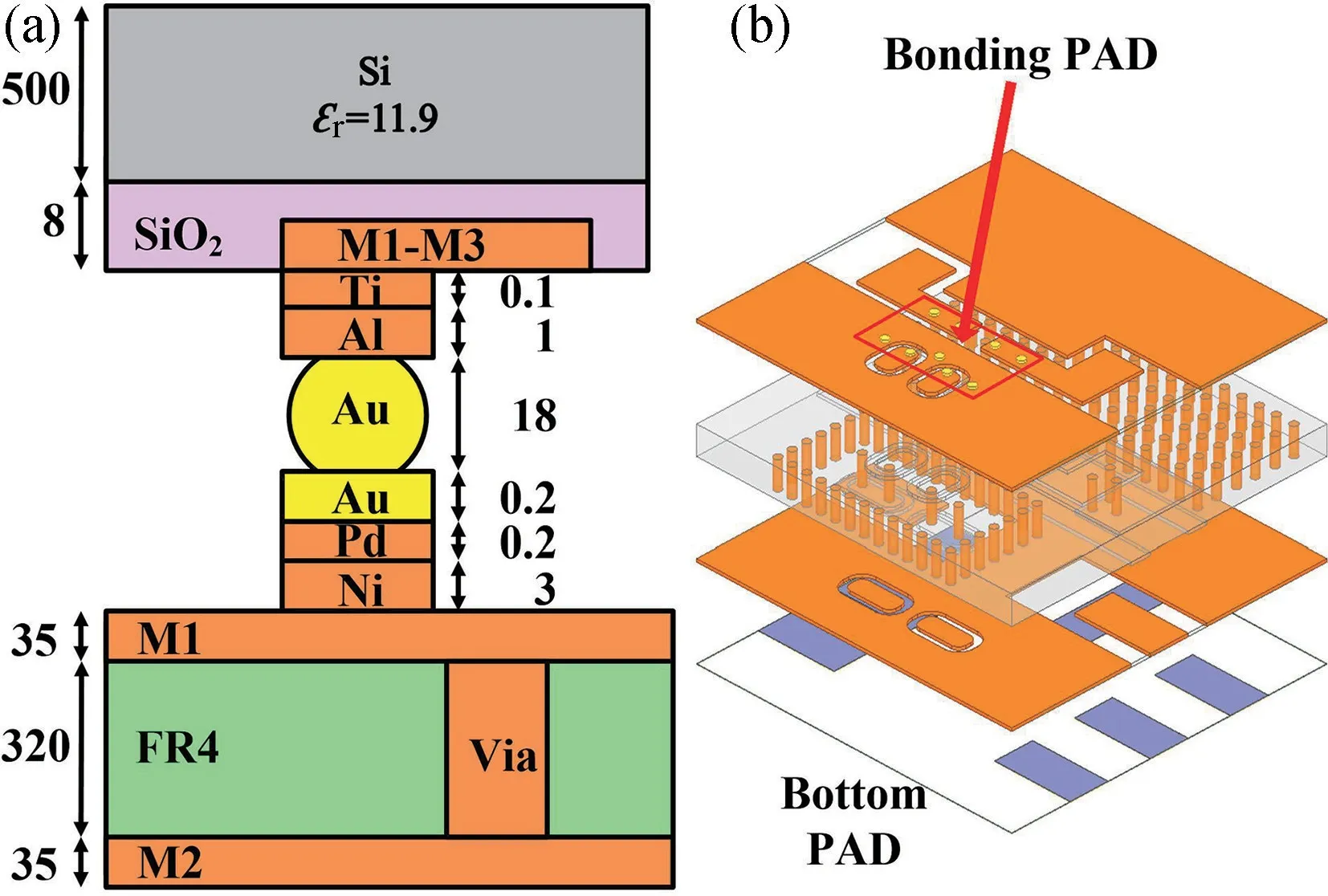

通过金球倒装工艺将芯片键合到基板上。如图6(a)所示,金球上方为倒置的IPD 芯片,下方为包含高Q值电感和输入输出端口的基板。金球上下层键合区域的材料为Al 或Au,以保证上下层有足够的结合力。芯片表面使用Ti/Al 金属材料,基板表面使用Ni、Pd 和Au 镀层。

图6 (a) 键合结构剖面图,单位:μm;(b) 基板整体结构Fig.6 (a) Cross-sectional views of the bonding structure(Unit:μm);(b) Overall structure of the proposed PCB

采用金球倒装键合工艺主要起到三个作用:(1)用于上下层的信号互联;(2)用于上下两层的共地;(3)为基板上层的滤波器提供电磁屏蔽,防止其干扰外界以及外界对其产生干扰。输入输出端口皆位于下层基板,因此下层基板尺寸大于上层芯片。为方便后续滤波器测试,将电感放置在5 mm×5 mm 的基板内,使用CPW 结构将输入输出端引到基板底层,如图6(b)所示。

2 工艺实现步骤

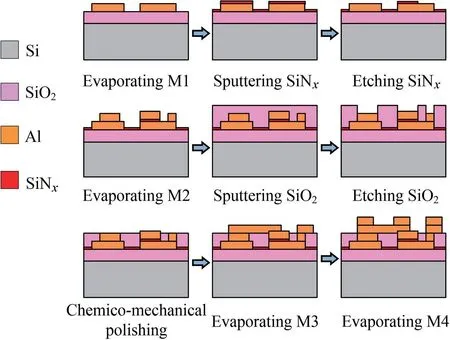

图7 展示了本文滤波器硅基芯片的加工工艺。采用电阻率为5000 Ω·cm 的高阻硅片作为衬底,以提高平面电感的Q值。首先,在硅衬底上溅射3 μm 厚的SiO2,用于实现硅片与平面螺旋电感的隔离。在SiO2上通过剥离工艺得到厚度为2 μm 的铝图案(M1)作为MIM 电容器的下电极板。溅射0.1 μm 厚的SiNx作为电容器介质,并对非电容位置进行光刻开窗。蒸发1 μm 厚的金属层(M2),部分作为MIM 电容的上极板,其余起到连接柱作用。进行SiO2的溅射,将金属完全覆盖在SiO2内,并使用CMP 与刻蚀工艺进行磨平开窗。

图7 IPD 工艺流程步骤Fig.7 Process flow of IPD technology

通过反溅工艺对M2 开窗位置进行表面处理,去除残留SiO2等氧化物后,再通过剥离工艺制作一层3 μm 厚的金属铝(M3)。最终在M3 层上制作一层1.1 μm 厚的Ti/Al 金属PAD。后续将金球植在芯片表面,再将芯片倒装在基板上,使用热压超声的方式将二者键合。

3 实验结果与测量

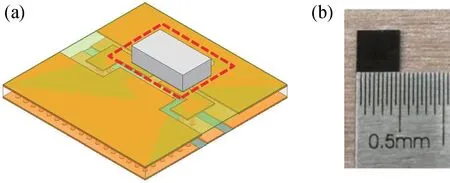

基于上述分析,本文设计了一款N77 频段的带通滤波器。为验证设计方案的准确性,结合IPD 工艺和PCB 工艺加工得到了N77 频段滤波器。所制作的滤波器整体结构如图8(a)所示,倒装完成后通过覆膜将滤波器完全密封,如图8(b)所示。图8(a)中红框所示为该BPF 的实际大小(不包含额外引出的输入输出PAD),尺寸为2.2 mm × 3.0 mm,即0.027λ0×0.037λ0,其中λ0为3.7 GHz 的波长。

图8 (a) 滤波器仿真结构;(b) 滤波器实物图Fig.8 (a) 3-D view of the proposed filter;(b) Photograph of the fabricated filter

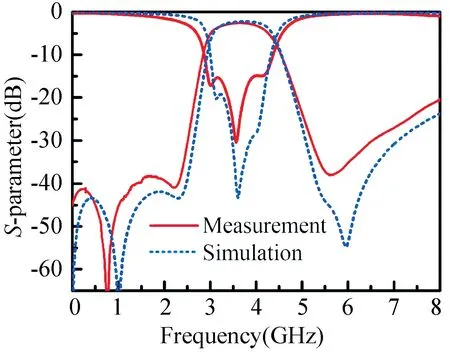

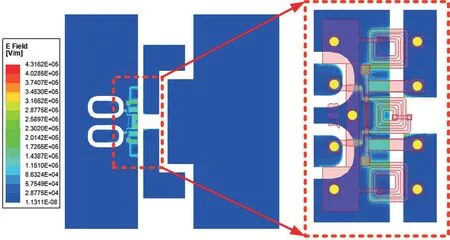

将滤波器元件焊接在评估板(EVB,Evaluation Board)上,使用矢量网络分析仪(是德科技,E5071C)进行测试,测量结果与仿真结果对比如图9 所示。实测损耗为-2.58 dB,上阻带存在两个零点,带外抑制大于30 dB,下阻带存在一个零点,带外抑制大于20 dB。需要注意的是,测试结果比图2(b)理想频率响应多一个传输极点,这是由于测试结果中包含了基板和测试板的影响。经仿真探究发现,该额外极点是由基板和芯片间的寄生电容效应导致的。如图10 所示,基板电场强度最大的区域与芯片轮廓基本吻合,二者间确实存在较强的电容效应。

图9 滤波器仿真及测试结果Fig.9 Simulated and measured results of the proposed filter

图10 基板电场分布图Fig.10 Electric field distribution of PCB

此外,本文使用铝作为主要金属材料,后续可以使用导电性更好的金属材料如铜、金等,以进一步降低欧姆损耗,提升带内性能。测试结果与仿真结果整体吻合较好,带外区域存在较小偏差,这是由于EVB板与器件之间存在耦合,并且EVB 板和测试接头存在一定插损。

表1 展示了本研究滤波器与已有文献中IPD 滤波器的性能对比。可以发现,本文所设计的滤波器拥有多个零点,且在使用低成本的铝作为主金属材料的情况下,器件损耗依然相对较好。

表1 与文献中现有IPD 工艺滤波器对比Tab.1 Comparisons with some related IPD filters

4 结论

本文将IPD 工艺和PCB 工艺相结合,设计并制备出了一款小尺寸(2.2 mm×3.0 mm)的大带宽、低损耗、低成本滤波器。基于PCB 基板的成本较低、内置电感Q值较高的特性,最终制备的滤波器最低损耗为-2.58 dB,1 dB 带宽为918 MHz。相较于其他已有的IPD 电路器件,本文基于低成本的铝材料器件仍在损耗性能方面占有优势,证明了该工艺结合的优越性。基于上述优点,本滤波器有望应用于5G/6G 毫米波通信系统中。