高增益差分无源N 通道带通滤波器的设计

2022-02-08盛艳婷蒋品群宋树祥岑明灿蔡超波

盛艳婷,蒋品群,宋树祥,岑明灿,蔡超波

(广西师范大学 电子工程学院,广西 桂林 541004)

近年来,随着无线传感器节点的大规模部署和可用无线电频谱的减少,使传感器网络中的接收机更易受相邻无线电设备的干扰。滤波器的主要作用是滤除干扰信号、提高接收机的性能,因此滤波器为接收机不可或缺的一部分[1~6]。传统的接收机前端滤波器采用体声波或表面波滤波器,具有较好的通频带宽和选频特性,但中心频率不可调、不易集成,特别是在多频段接收机中,需要外接多个滤波器,因此,使用传统滤波器的接收机,通常面积较大、成本较高。与传统滤波器相比,N通道滤波器的中心频率可调,所以不需要外接多个滤波器,减小了滤波器的体积。此外,N通道滤波器还具有品质因数较高且易于集成等优点,因此被广泛应用于射频接收机前端。因为射频接收机前端对滤波器的增益和线性度要求较高[7~11],所以高增益、高线性度的N通道滤波器具有较大的研究意义与实用价值。

高增益N通道带通滤波器的设计难点在于既要保持良好的线性度,又要提高增益。2019 年,Song等[12]提出了一种基于滤波器合成方法的无源射频N通道滤波器,采用多个无源耦合结构,实现了具有传输零点的N通道带通滤波器。该滤波器的优点是线性度和品质因数都较好,缺点是增益很低、中心频率的可调谐范围较窄。2022 年,Shao 等[13]设计了一款应用于低功耗多通带Blocker-Tolerant 接收机的N通道带通滤波器,通过在电路中嵌入低噪声放大器,增加通带信号的增益,但该滤波器电路结构复杂,对电路工作原理的分析也变得困难。2020 年,Tiwari 等[14]设计了一款增益提高型N通道带通滤波器,采用两级滤波器级联结构,使N通道滤波器达到较高的增益,缺点是线性度较低。2021 年,吕芸芸等[15]设计了一款带有传输零点的增益提高型N通道带通滤波器,采用传输零点技术和增益提高技术实现了较高的增益,优点是增益较高,缺点是线性度较低。

针对上述问题,本文采用差分结构、隐式电容叠加技术和底板开关技术,设计了一款高增益、高线性度的差分无源N通道带通滤波器,在保持无源N通道带通滤波器高线性度的同时,提高了增益。

1 N 通道带通滤波器

1.1 传统电路设计

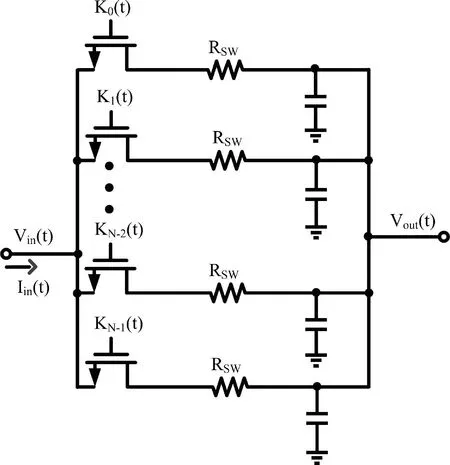

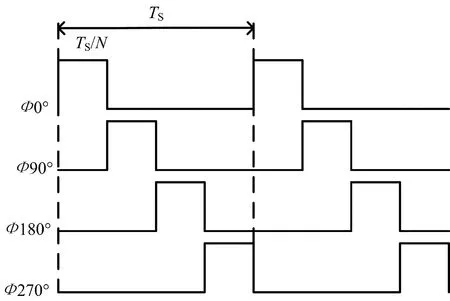

传统的单端N通道带通滤波器如图1 所示,由多相不交叠时钟控制的N个开关依次接通N个并联的无源低通滤波器,且任意特定时刻仅有一条通道导通。第i个开关的时钟控制信号Ki(t)频域函数表达式为:

图1 传统单端N 通道带通滤波器Fig.1 Traditional single-ended N-path band-pass filter

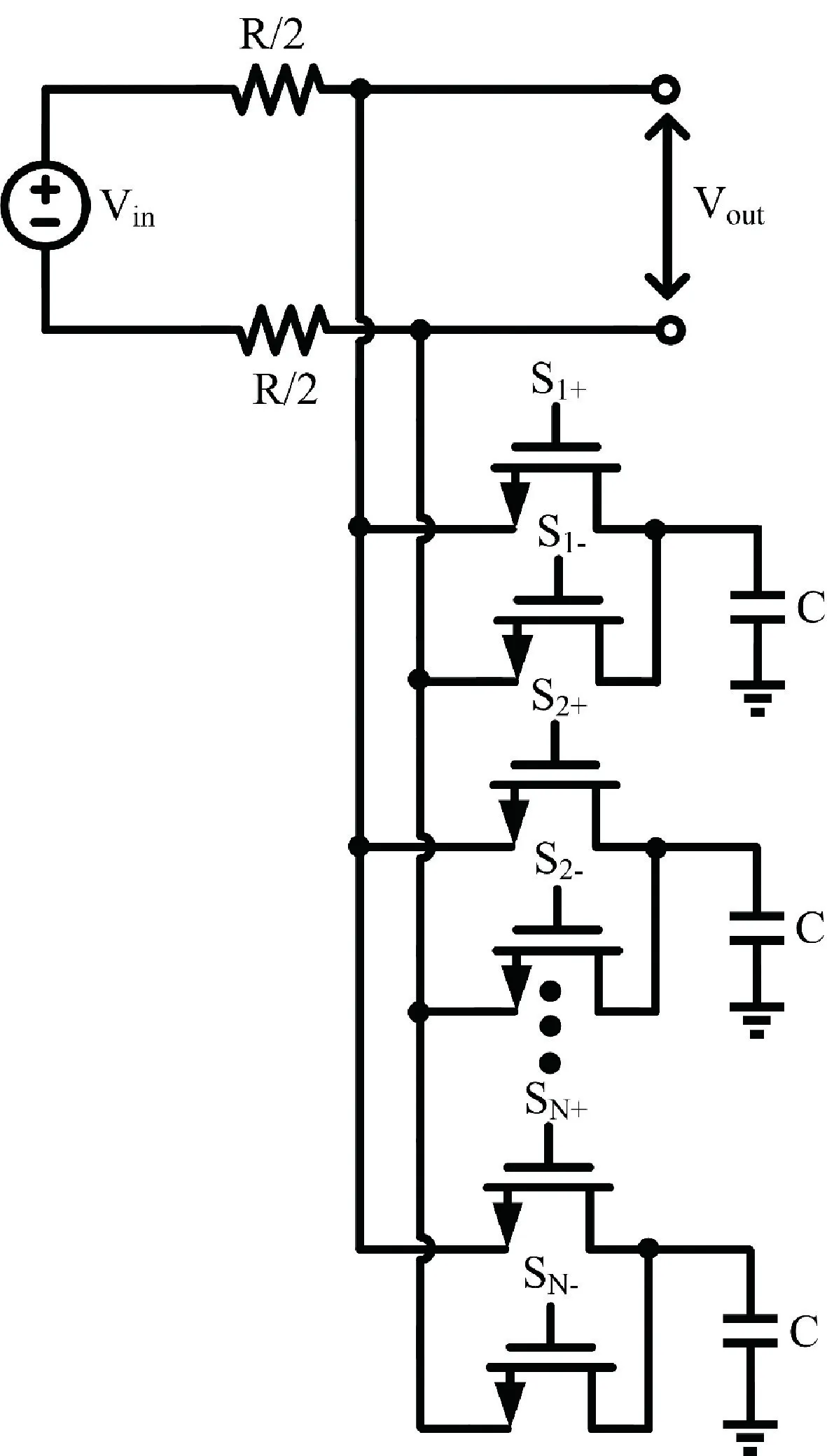

由式(1) 可知,在中心频率fSW及其谐波处,Ki(ω)不为零,因此,可将N通道滤波器视为低通滤波器以fSW为单位的频移,具有带通功能,但对通带信号不具有放大作用。差分结构的N通道带通滤波器如图2 所示,它能有效抑制偶次谐波。

图2 传统差分N 通道带通滤波器Fig.2 Traditional differential N-path band-pass filter

1.2 本文电路设计

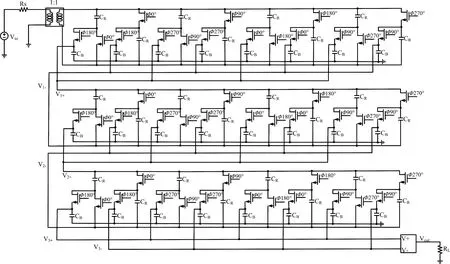

针对传统差分N通道带通滤波器无法放大通带信号的不足,本文基于隐式电容叠加技术设计了一款高增益差分无源N通道带通滤波器,电路结构如图3 所示。图中每级电路均为4 通道差分带通滤波器,且每个通道采用电容开关和开关电容网络的并行组合(CS‖SC)结构,输入信号Vin为正弦波。通过1 ∶1 的片外变压器将单端信号转换为差分输入信号后,N通道带通滤波器对输入信号进行处理,并转化为单端输出。

图3 本文设计的完整电路Fig.3 The complete circuit designed in this paper

为了提高电路的增益,本文所设计的差分无源N通道带通滤波器采用三级级联结构。将第一级的输出差分信号作为第二级的输入信号,同时把第二级的输出差分信号作为第三级的输入信号。当第三级进行信号输出时,把输出差分信号转换为单端信号加载到负载,实现增益提高的功能。

1.3 高增益隐式电容叠加电路

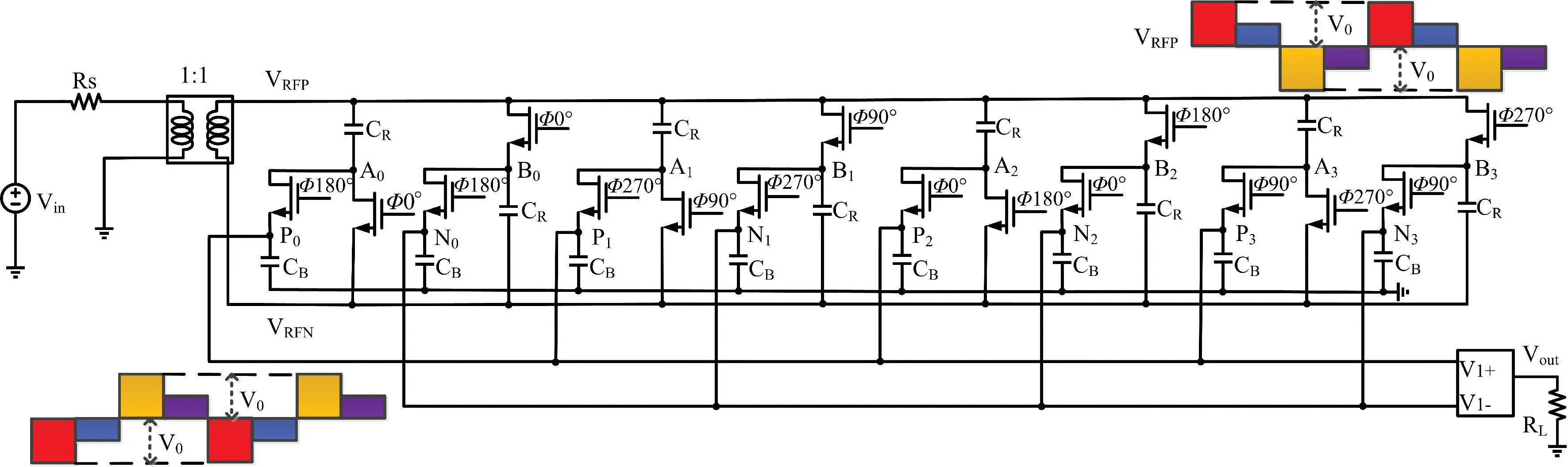

以电路的单级结构为例,推导其增益表达式,电路结构如图4 所示。图中每个CS‖SC 网络由电容CR、开关和4 相不交叠时钟信号组成,时钟信号如图5 所示,并且电容CR的极板(AX、BX)使用开关连接到基带电容CB。

图4 本文设计电路的一级结构Fig.4 The primary structure of the circuit designed in this paper

图5 开关时钟信号Fig.5 Switch the clock signal

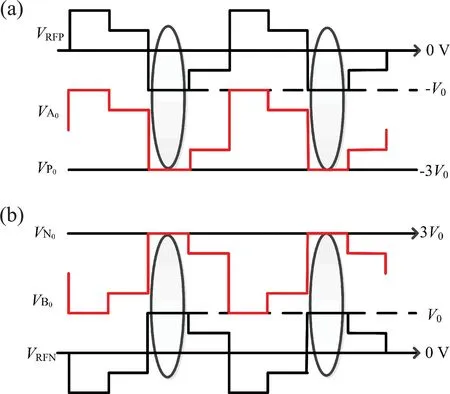

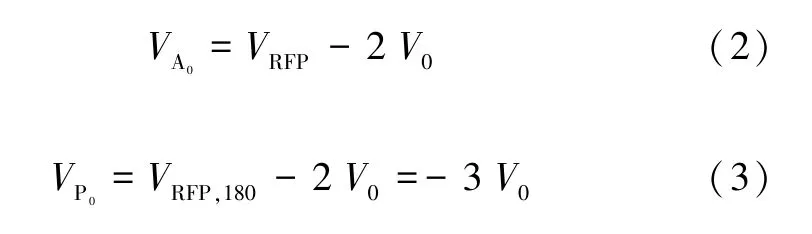

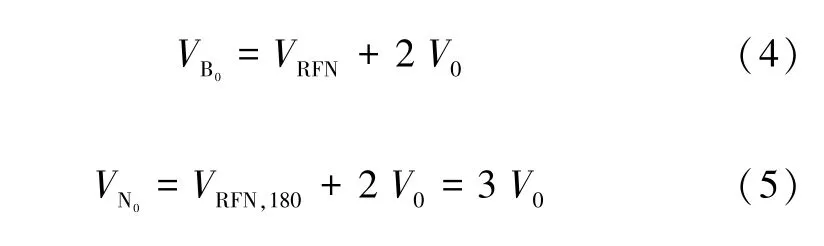

以第一级的第一组CS‖SC 结构为例对电路进行分析,因为电路工作在混频模式下,时间常数RC>>Ts/N,所以输入电压VRFP遵循正弦波Vin/2 的阶梯近似[16]。第一个通道电容的上下极板电压变化如图6所示,VRFP和VRFN为一组差分信号。当相位为Φ0°~90°时,VRFP为+V0,VRFN为-V0,由于CS‖SC 组合的每个电容CR上的压降为差分输入的全摆幅电压,所以电容CR上存在2V0的压降。当相位为Φ180°~270°时,A0处的电压为:

图6 (a) 第一个通道电容下极板的电压变化;(b) 第一个通道电容上极板的电压变化Fig.6 (a) The voltage change of the lower plate of the capacitor of the first path;(b) The voltage change of the upper plate of the capacitor of the first path

因为VRFP,180等于-V0,所以A0处的电压为-3V0。同时,Φ180°~270°时的B0处电压为:

因为VRFP,180等于V0,所以B0处的电压为3V0。A0和B0处的电压信号通过开关(时钟为Φ180°)向下混频到基带电容CB上,即当相位为Φ180°~270°时,P0处的电压为VRFP的3 倍,N0处的电压为VRFP的-3倍。在Φ270°~360°期间,P1处的电压为VRFP的3 倍,N1处的电压为VRFP的-3 倍。以此类推,当相位为Φ0°~90°,Φ90°~180°时,P2、P3处的电压为VRFP的3 倍,N2、N3处的电压为VRFP的-3 倍。将P0、P1、P2、P3连接在一起,即可在整个时域实现VRFP的3 倍的放大,将N0、N1、N2、N3连接在一起,即可在整个时域实现VRFP的-3 倍的放大。

使用差分输出,将V1+作为差分输出的正极,V1-作为差分输出的负极,输出信号为VRFP的6 倍,因为输入信号VRFP遵循正弦波Vin/2 的传统阶梯近似,所以最终能够实现3 倍的信号放大。

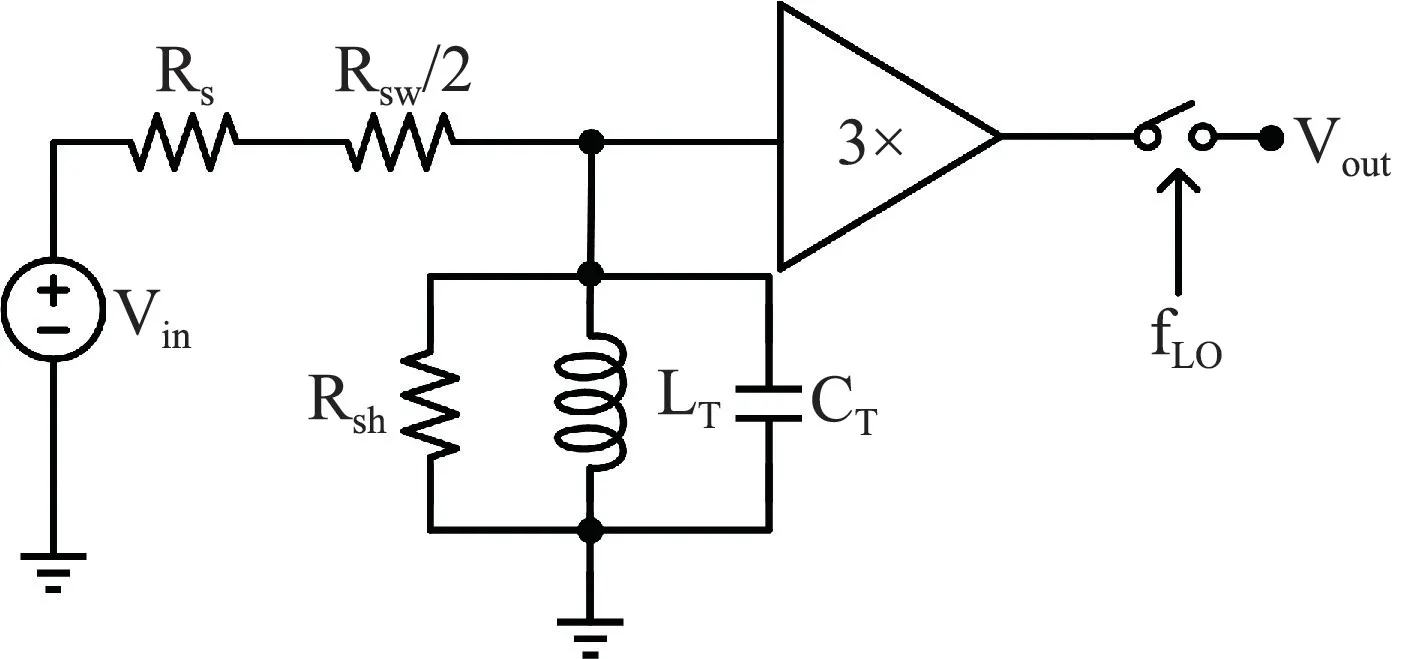

单级4 通道差分带通滤波器的等效模型可近似为RLC 网络、线性放大器和NMOS 管开关的级联,如图7 所示。

图7 单级结构等效模型Fig.7 Single-level structure equivalent model

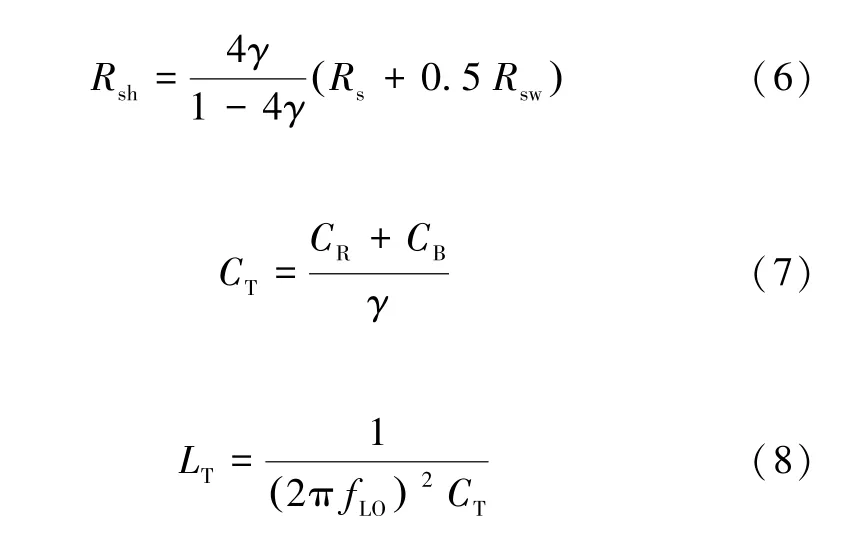

其中Rsh、CT和LT的表达式为:

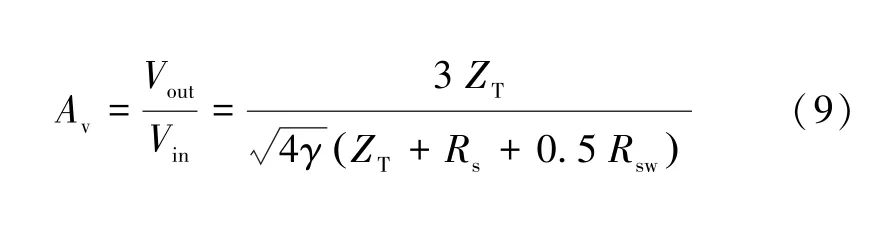

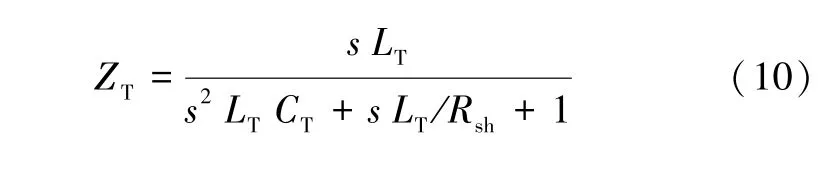

RLC 网络仅在数值上模拟CS‖SC 结构,其中,Rs表示理想电压源的内阻,Rsw表示开关的电阻,Rsh表示滤波器通道的电阻,CT表示滤波器通道的电容,LT表示滤波器通道的电感,γ=2/π2。线性放大器表示隐式电容叠加技术产生的电压增益。由于在滤波器通道中Rsw的阻值较小,因此与滤波器的工作频段相比,由Rsw和CB产生的零点位于较高的频率,为简化分析,图4 单级结构的等效模型忽略该零点。单级4通道差分带通滤波器在中心频率处的电压增益表达式为:

式中,ZT为Rsh、LT和CT的并联电阻,其表达式为:

由式(9)可知,在负载匹配时,单级结构能够实现通带信号3 倍的放大。本文对一级结构进行级联,实现3 级4 通道差分无源带通滤波器。使用NMOS管代替理想开关,每个NMOS 管做开关使用时都存在导通电阻和寄生电容,因此对电路的性能造成影响,最终实现26 dB 的信号放大。

1.4 高线性度电容开关电路

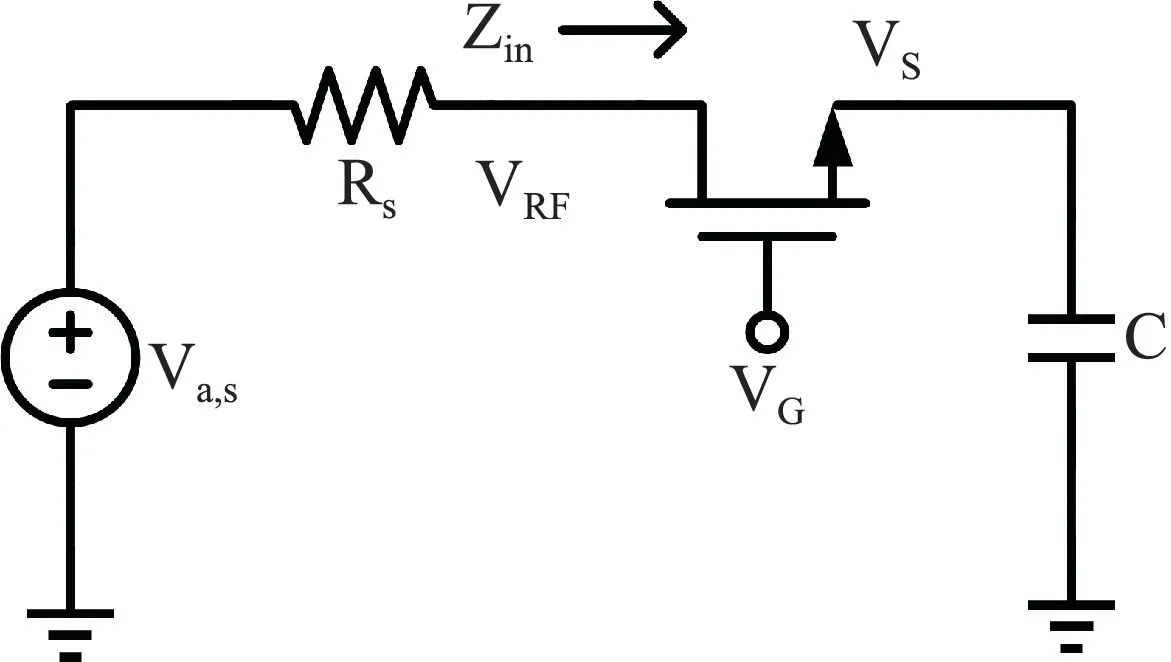

传统N通道滤波器中常采用电容顶板开关电路结构,如图8 所示。当NMOS 管开关闭合时,由于栅极电位VG固定,源极电压VS发生改变,因此其栅源电压VGS会发生很大的变化,这会影响NMOS 管的开关电阻阻值并减少电路的线性度。

图8 电容顶板开关电路Fig.8 Capacitive top plate switching circuit

为了减少NMOS 管开关的VGS和VDS对电路线性度的影响,本次设计采用了一种电容底板开关电路,将RF 节点连接至电容顶板,同时底板通过NMOS 管开关连接到地,如图9 所示。

图9 电容底板开关电路Fig.9 Capacitive backplane plate switching circuit

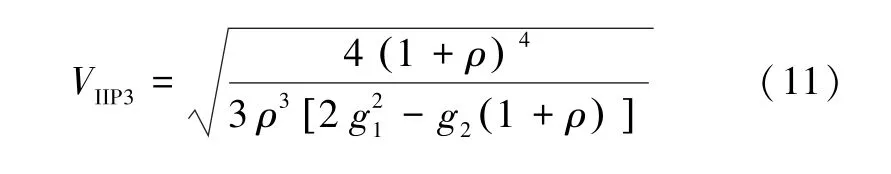

与传统的电容顶板开关电路相比,电容底板开关电路的主要目的是改善由于NMOS 管开关电阻引起的电路非线性,从而实现更高的线性度。在电容底板开关电路中,当NMOS 管开关闭合时,其栅源电压VGS恒定,避免了VGS对电路线性度的影响。同时,由于Zin为高阻抗,NMOS 管的漏源电压VDS对电路线性度的影响也随之减小。因此,与电容顶板开关电路相比,本次设计采用的电容底板开关电路能使电路获得更高的线性度。电路输入三阶交调点(IIP3)的表达式为:

其中,ρ、g1和g2的表达式分别为:

式中:VOD表示NMOS 管的过驱动电压;VSAT表示NMOS 管的饱和电压。

2 电路仿真与分析

本文设计的N通道带通滤波器采用TSMC 40 nm CMOS 工艺设计,在进行版图绘制时,左右对称的布局和布线可以减少器件失配对电路性能造成的影响,为了提高电路的匹配性,在版图中添加dummy 管。N通道带通滤波器的版图如图10 所示。

图10 N 通道带通滤波器版图Fig.10 N-path band-pass filter layout

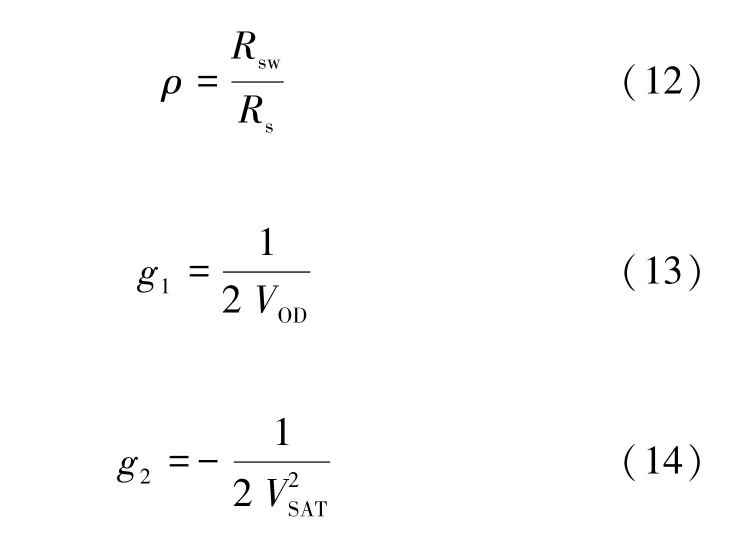

N通道带通滤波器频率特性仿真结果如图11 所示。由于采用差分结构,因此电路对于偶次谐波有较好的抑制效果。同时,通过隐式电容叠加技术使无源N通道带通滤波器在通带内实现了信号的放大,当中心频率fs=2 GHz 时,电路的增益达到26 dB。

图11 N 通道带通滤波器的频率特性(fs=2 GHz)Fig.11 Frequency characteristics of N-path band-pass filters (fs=2 GHz)

N通道带通滤波器的中心频率可调范围仿真结果如图12 所示,其中心频率可调范围为1.6~2.4 GHz。在整个频率可调范围内,带宽为3.4~7 MHz,增益均大于24 dB,这说明该滤波器适用频率范围相对较广,有较好的频率选择性,同时,对通带信号有较高的增益提高。

图12 N 通道带通滤波器的中心频率可调范围Fig.12 The center frequency adjustable range of the N-path band-pass filter

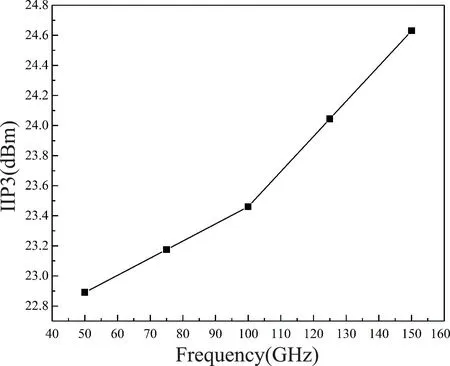

当中心频率fs=2 GHz 时,N通道带通滤波器输入三阶交调点(IIP3)的仿真结果如图13 所示。由图13 可知,本文所设计电路的输入三阶交调点大于22.8 dBm,因此,本文设计的带通滤波器具有很好的线性度。

图13 N 通道带通滤波器的IIP3Fig.13 The IIP3 of the N-path band-pass filter

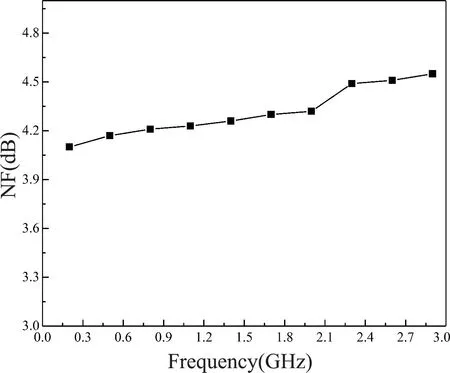

本文设计的N通道带通滤波器的噪声系数(NF)如图14 所示。由图14 可知,在整个频率可调范围内,噪声系数小于4.6 dB。因此,本文所设计的滤波器噪声系数相对稳定,具有较好且稳定的抑制噪声的能力。

图14 N 通道带通滤波器的NFFig.14 The NF of the N-path band-pass filter

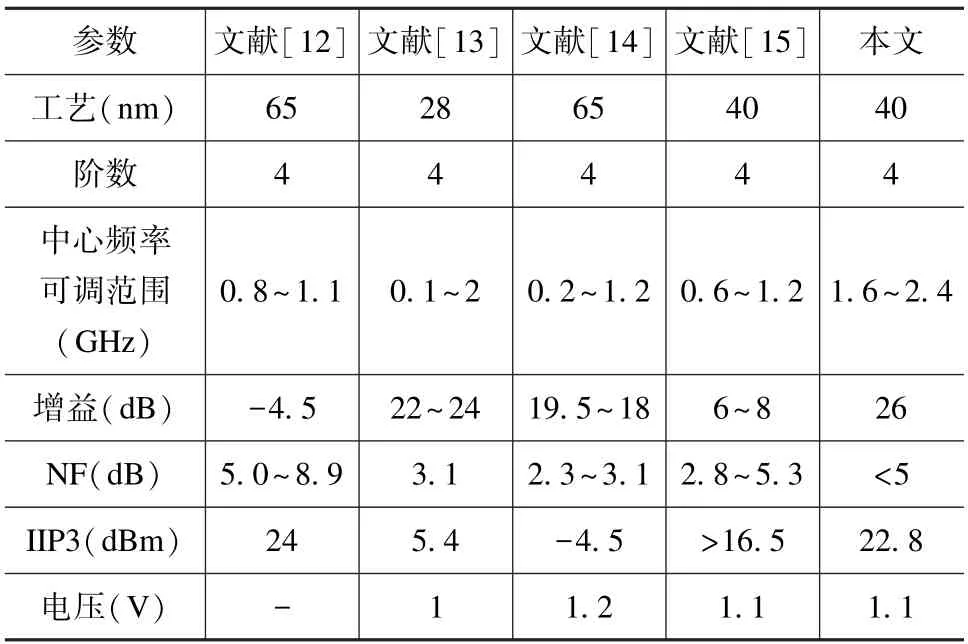

将本文与近几年发表文献电路参数进行比较,如表1 所示。文献[12]为无源N通道带通滤波器,该电路的线性度较高,但是无法放大通带信号,同时噪声相对较高。文献[13-15]在N通道带通滤波器中引入低噪声放大器,使滤波器在实现滤波功能的同时,放大了通带信号,但是,由于引入运放,电路的线性度较低。本文所设计的带通滤波器不仅具有较高的增益,而且线性度较好。

表1 与其他文献电路参数的对比Tab.1 Comparison of circuit parameters with other literatures

3 结论

本文设计的高增益差分无源N通道带通滤波器使用隐式电容叠加技术,利用电容下极板的电位在不同时刻进行叠加,在理想情况下实现单级结构3 倍的信号放大。电路将3 个单级结构进行级联,在理想情况下能够实现27 倍的信号放大。此外,采用电容底板开关电路使滤波器具有较高的线性度。电路基于TSMC 40 nm CMOS 工艺设计,使用Cadence Spectre RF 软件对其进行仿真验证。后端仿真结果表明: 当电源电压为1.1 V,滤波器中心频率可调范围为1.6~2.4 GHz,当中心频率fs=2 GHz 时,N通道带通滤波器的增益达到26 dB,输入三阶交调点(IIP3)大于22.8 dB,在射频接收机前端有重要的应用。