基于FPGA+DSP架构的RapidIO接口硬件技术与实现

2022-01-25余晖冬龚昊龑王书磊

余晖冬,龚昊龑,王书磊

应用研究

基于FPGA+DSP架构的RapidIO接口硬件技术与实现

余晖冬,龚昊龑,王书磊

(中国人民解放军92145部队,上海 200080)

RapidIO传输效率高、系统成本低、系统稳定性好,在高性能嵌入式系统中得到了广泛的应用。传统的RapidIO总线致力于解决器件间、板间和子系统间等同一机箱内或同一系统内的背板互连问题。为使多个嵌入式系统互联保持总线的一致性,并能在机箱间使用RapidIO总线,需要对RapidIO总线的使用范围进行扩展。本文提出了基于FPGA+DSP架构的通用RapidIO接口硬件实现方案。通过引入光电模块,将RapidIO的LVDS信号转换成光信号,在机箱间传输信号,成功拓展了RapidIO传输距离,解决了RapidIO传输距离局限于一个机箱内的问题主要从硬件方面对RapidIO接口实现方案进行阐述。最后搭建实验平台对所实现的RapidIO总线进行了连通性测试,证明了此种方案的可行性。

RapidIO 嵌入式互连 FPGA DSP

0 引言

嵌入式总线的总体发展迅猛,新的总线不断推出,其中具有代表性的总线有:Hyper Transport、PCI Express、InfiniBand、RapidIO等[1]。经过不断地发展,RapidIO已经成为嵌入式互连技术方面唯一一个得到授权的标准。RapidIO己经成为电信、通信行业以及高性能嵌入式系统中的芯片与芯片之间、板间、背板间互连技术的主要手段,几乎所有嵌入式系统芯片设备供应商都加入了RapidIO行业协会[2]。RapidIO总线被最广泛地应用于嵌入式系统中[3]。

随着嵌入式系统的不断发展,所支持的系统不再局限于一个机箱内,如何扩展RapidIO,使之适应较远距离嵌入式系统的互联,是亟待解决的问题。对于如何扩展RapidIO的传输距离,我们将RapidIO底层的差分电信号转换成光信号,成功地延伸了RapidIO的传输距离,并解决了RapidIO仅能在一个机箱内使用的问题。至今,人们对如何实现RapidIO软件协议研究较多,对RapidIO的硬件平台的实现研究较少。对于希望使用RapidIO接口的设备来说,硬件实现具有一定的灵活性,使用FPGA+DSP结构是现代嵌入式系统的流行框架,在该框架上实现RapidIO接口具有重大的现实意义。

1 RapidIO接口模块硬件设计

RapidIO接口分为两大部分,第一部分由FPGA、DSP得到实现RapidIO接口的高速串口,FPGA通过其本身的引脚加相应的外接耦合电路构成物理接口,DSP与FPGA通过EMIF接口互联,DSP使用FPGA中的逻辑资源实现RapidIO的软件协议;第二部分为光电电路,通过引入光电转换器将高速串口的差分电信号转换成可以远程高速稳定传输的光信号,实现RapidIO接口的传输距离的扩展。

由FPGA和DSP协同实现的RapidIO接口硬件设计原理如图1所示。

图1 RapidIO接口硬件设计原理

DSP通过EMIF接口对FPGA内部逻辑资源及硬核进行控制,灵活实现RapidIO物理层以上的协议,并能根据需要灵活扩展多个其他类型接口。FPGA提供丰富的硬件资源,如高速串口、逻辑资源、布线资源、硬核资源等。二者配合起来实现RapidIO数据到电信号的转换,提供高速串口接口。光电电路负责解决高速串口与其他接口连接时的匹配问题,使电路的设计符合高速串口规范要求,实现稳定的通信,并最终将电信号转换成光信号,实现远距离传输。

2 FPGA和DSP选型

该系统采用Altera公司的StratixⅡ GX系列芯片[4]。Altera公司的StratixⅡ GX系列芯片内嵌专用硬核[5]能极大提高工程效率。并且在相同的成本下能提供更多的逻辑容量及更好的稳定性。StratixⅡ GX系列FPGA采用先进的90 nm技术构建,与同类产品相比,DSP资源多出4倍,I/O资源多出21%,逻辑资源多出5%,存储资源多出50%。运算速度更快,逻辑占用率降低25%。是市面上主流的FPGA之一。DSP芯片选用TI公司的TMS320C6000系列芯片[6]。TMS320C6000系列DSP采用VelociTI超长指令字的体系结构,可以在单周期内执行多条指令[7]。性能上远远超越传统的DSP。

3 RapidIO接口相关电路的实现

3.1 DSP相关硬件实现

RapidIO接口模块的DSP相关硬件设计主要包括电源设计、时钟设计、复位设计等。

DSP工作电源需要稳定的直流1.2 V和3.3 V,1.2 V是DSP中实现逻辑处理的电压值,而为DSP提供时钟的DSP内部锁相环(PLL)的驱动电压需要3.3 V。

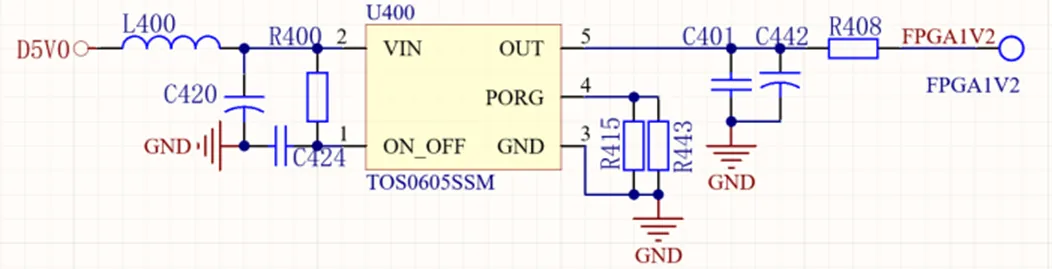

DSP的3.3 V电压供电原理如图2所示。

图2 DSP中3.3 V电压供电设计

由外部电源提供的正5 V电源经过LC电路(由电感和电容组合而成的电路)滤波,再经过电源转换芯片TOS0605SM转换后得到3.3 V电压值输出,输出再经过电容滤波,滤除高频分量,得到稳定的3.3 V电压值。在转换好的3.3 V电压和供给DSP的3.3 V电源之间有一个电阻,阻值为0,当通过该电阻的电流过大时,电阻烧毁,形成断路。这样主要是避免电路中有短路现象时,电流过大而引起DSP损坏,起到保险丝的作用。同时电阻值很小,由电阻上引起的电压的变化也较小,不会影响到正常工作情况下提供给DSP的电压值。

与DSP的3.3 V供电不同,DSP的1.2 V电压由电源转换芯片TPS74901经过转换得到。TPS74901是一款能够提供稳定电压转换的电源芯片[8],具有很好的性能。外部3.3 V电源输入,配置好外部电阻参数后可以得到1.2 V输出电压。TPS74901的说明书中列举了R107和R101的不同电阻值组合对应的输出电压值。理论上R101的阻值为2.49,R107的阻值为4.99。为减少高频干扰,在电源转换芯片的输入和输出端加入对地电容。DSP的1.2 V电源供电原理如图3所示。

图3 DSP中1.2V电压供电设计

DSP的时钟供给硬件设计如图4所示。DSP的时钟由本地晶振产生一个25 MHz的时钟,经过倍频芯片CY2308SI[9]得到DSP需要的三个时钟:BECLKIN、DSPCLK、AECLKIN。CY2308SI的输出经过阻值很小的电阻之后与DSP的输入引脚相连。

图4 DSP中时钟设计

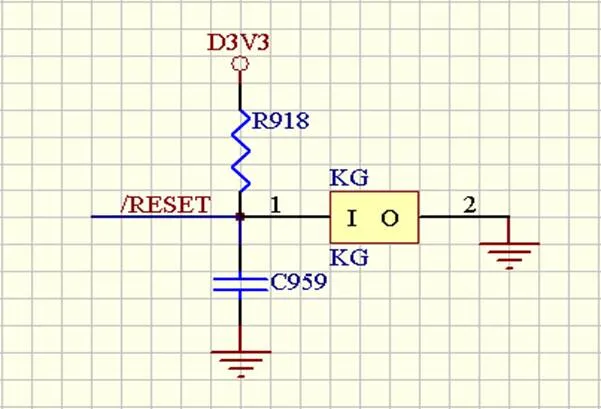

DSP的复位主要有人工复位和软件复位。二者任意一个有效即可对DSP进行复位。复位原理如图5所示:

图5 DSP中复位设计

DSP复位要求低电平持续10个周期,否则不复位,软件复位可以人工编程控制低电平持续时间,无需特殊考虑。而人工复位无法准确控制低电平持续时间,在复位按键和DSP的3.3 V之间加入两个电容,当复位键按下之后,电容放电,复位键松开后,电容充电,使得74HC08的第1个和第2个管脚能保持一定时间的低电平,从而使得低电平持续时间达到要求。通过调整电容的大小来调整低电平持续的时间,不需要人为地长按复位键,更加方便简洁,减少调试过程中不必要的麻烦。

3.2 FPGA相关硬件实现

RapidIO接口模块的FPGA的相关硬件设计主要包括电源设计、时钟设计、复位设计和高速串口设计等。

FPGA工作电源需要稳定的直流1.2 V和3.3 V,1.2 V是FPGA中实现逻辑处理的电压值,而为FPGA提供时钟的FPGA内部锁相环(PLL)[10]的驱动电压以及相关管脚上的逻辑1的电平需要3.3 V。

FPGA的3.3 V电压的设计与DSP相同,均由同一个芯片转换得到,具体设计参考DSP电压设计,此处不再赘述。

FPGA的1.2 V电压供电设计如图6所示。FPGA的功耗相对DSP较大,选用芯片TOS0605SM芯片作为电源转换芯片,该芯片最大输出电流达到6 A,可以满足FPGA工作时对电流的要求。该设计和3.3 V电源设计类似,通过改变外围电路的参数,调整输出电压,得到要求的输出电压值。

图6 FPGA中1.2 V电压供电设计

FPGA内部集成有锁相环,需要外部输入一个差分时钟作为时钟源。FPGA时钟设计如图7所示。

图7 FPGA中时钟设计

外部时钟或者本板晶振产生一个输入时钟,通过时钟芯片MC100EL16 V转化成差分时钟,经过两个电容隔去直流后,再加上一个稳定的直流电压偏置,作为FPGA的输入时钟。FPGA为外部提供了差分时钟输入接口,相应管脚属性设置如表1所示:

表1 FPGA中时钟管脚属性设置

相对DSP复位设计来说,FPGA复位较为简单,FPGA的复位操作是由程序完成,而不是由硬件完成。通过一个普通的输入引脚,将复位信号输入FPGA,程序对输入的电平进行判定,然后对FPGA进行复位。且通过硬件对FPGA复位进行控制的只有人工复位,其余的复位信号直接通过引脚输入FPGA,FPGA在内部编程实现各复位信号的综合控制。FPGA复位外部硬件电路设计如图8所示。

图8 FPGA中复位设计

当按下复位键后,电容不断放电,1点电压不断减小,直至为0,输入有效的复位信号。当松开复位键后,电容不断充电,直至电压为3.3 V。加入电容可以防止按复位键时产生的抖动而使得FPGA中无法正常判断输入复位的逻辑。在抖动的过程中,时间很短,电容来不及充放电,故1点的电压基本保持不变,输入的复位逻辑保持不变。

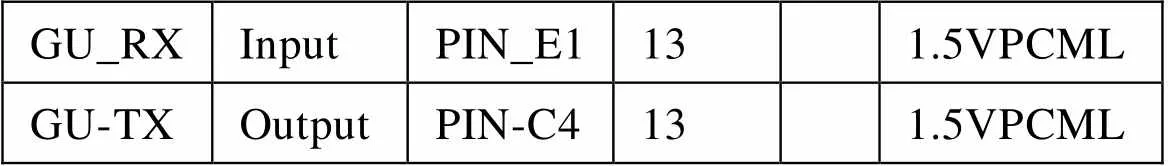

FPGA高速串口的设计主要包括引脚的选择及属性的设置。StratixⅡ GX 系列FPGA为用户提供丰富的高速串口资源。考虑PCB布板的合理性,选用其中一组作为高速串口接口即可。FPGA中高速串口设计如表2所示。

表2 FPGA中高速串口设计

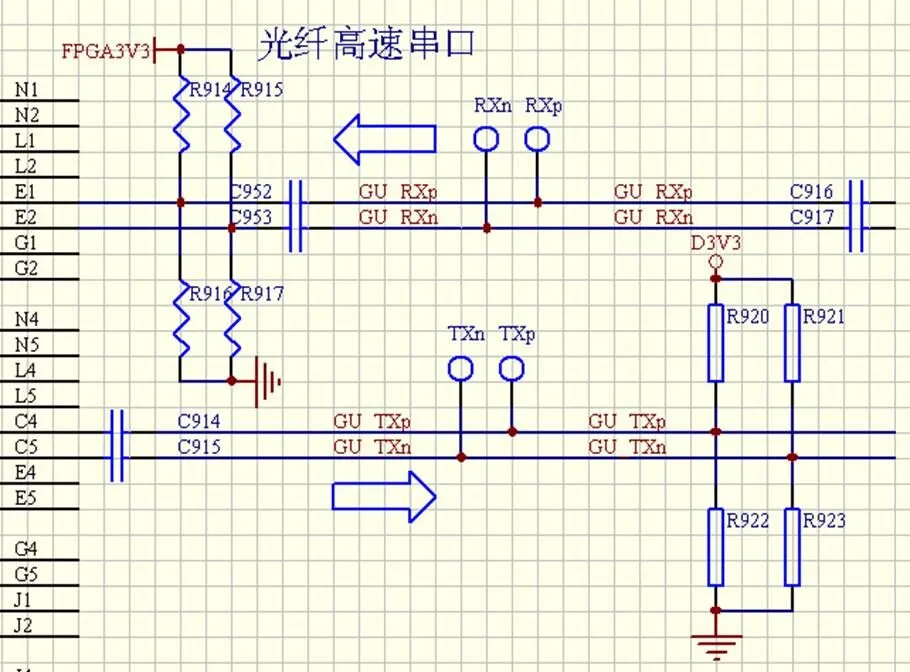

选择E1和E2作为高速串口中接收端,选择C4和C5作为高速串口中的发送端。

3.3 光电电路相关硬件实现

高速串口的外围硬件电路的设计主要包括FPGA高速串口与光电转换器连接的设计以及光电转换器相关硬件设计。

FPGA高速串口与光电转换器连接的电路主要完成光纤接口和FPGA接口之间的信号转化和匹配的问题,通过转化实现信号的正常识别和连通。高速串口和光电转换器的连接如图9所示。

图9 高速串口外围电路设计

电路主要分为两个部分,接收部分和发射部分。对于两部分电路来说,原理相同。从独立的数据通路来看,均是在数据的输出端首先经过一对电容隔去直流影响,再经过较长的布线到达数据的接收端,在接收端再加入隔值电容(阻止直流信号通过),然后通过上拉和下拉电阻,给差分信号一个稳定的直流偏置,将偏置之后的信号送给数据的接收端。从整体来看,发射部分和接收部分不同之处主要在于各通路的信号流向不同。对于发送通路来说,信号是由FPGA流向光电转换器;对于接收通路来说,信号流向是光电转换器流向FPGA。由于信号的流向相反,硬件电路的设计也相反。且在发射部分,省去了光纤接口附近的电容。发射部分和接收部分的另外一个不同点就是供电的电源不同,导致直流偏置的电源也不同。FPGA接口由FPGA的3.3 V供电,故偏置电路中也用FPGA3V3(FPGA的3.3 V电源)来驱动偏置电路,而光纤接口由D3V3(外部电源直接提供的3.3 V电源)供电,故靠近光纤接口的偏置电路由D3.3 V来驱动。

光电转换器的设计主要就是光电转换器型号的选取及外围电路的设计。光电转换器型号选用0EA02-F04-343-313-01Y。

光电转换器的相关电路设计如图10所示。

图10 光电转换器电路设计

光电转换器的电源是由外部提供的3.3 V电源经过LC滤波得到的直流电源。接收和发射分别供电。特别设计一个LED灯指示接收是否出错。

4 RapidIO接口的连通性验证

将该RapidIO接口模块引入到无线电通信系统中,由于发送时功率较大,所以发信系统基带信号处理系统和射频信号处理系统之间物理上相隔较远,必须使用远距离的RapidIO传输信号。

对于发射通路,音频信号源SFG-2104函数信号发生器产生2 K的基带信号,经基带信号处理系统处理完毕后,将基带信号通过RapidIO接口传送到射频信号处理系统。射频模块将信号采用上边带调制方式进行处理,载频为3 M,最终得到3.002 M射频信号。示波器1通道测试基带模块的输入音频测试点,2通道测试射频模块输出射频信号。实验结果如图11所示。

图11 发射通路实验结果图

图11中示波器上方为音频输入信号,下方为射频输出信号。可以证明基带单元到射频单元的数据发送通路正常。

结果证明,信号可以通过RapidIO接口进行传输。

5 小结

文章详细介绍了基于FPGA+DSP架构的RapidIO接口的硬件设计与实现。主要从硬件基础平台、RapidIO接口模块的设计与实现两个方面介绍了RapidIO的硬件设计。硬件的设计所用到的芯片主要有FPGA、DSP、光电转换器、电源芯片、晶振等。而对于每种芯片在硬件实现中的应用都做了详细的说明。最后对该硬件设计的可行性进行了实验验证。该种RapidIO接口的设计思想,将光电转换器的引入到系统中,成功地扩展了RapidIO的传输距离,具有较强的实用性。文章最后对RapidIO的可用性进行了验证,但是对其性能没有系统地验证,有待进一步研究。

[1] Chini P, Giambrene G, Kota S.A Survey on mobile satellite systems[J]. International Journal of Satellite Communications, 2010,28(1): 29-57.

[2] 朱碧伟, 张捷, 田骅. 基于FPGA短波通信发信终端实现[J]. 微型电脑应用, 2011(8): 13-14.

[3] 宋宇飞, 李小平, 周正. 基于DDS芯片AD9852的数字短波通信发射机设计 [J]. 信息技术, 2012(5): 69-70.

[4] 王诚, 蔡海宁, 吴继华. Altera FPGA/CPLD设计[M]. 北京: 人民邮电出版社, 2011.

[5] Altera Corporation.Stratix II GX device handbook, volume 1 [EB/OL]. 12343 Hymeadow, 101 Innovation DriveSan Jose, CA 95134, 2007.

[6] Texas Instruments. TMS320C6455 Fixed-Point Digital Signal Processor [EB/OL]. http://www.ti.com. Oct, 2007.

[7] 汪安民, 张松灿, 常春藤. TMS320C6000实用技术与开发案例 [M]. 北京: 人民邮电出版社, 2008.

[8] TPS74901 EVM-210 User Guide. [EB/OL]. http://www.ti.com. Oct, 2013.

[9] CY2308 3.3 V zero delay buffer. [EB/OL]. http://www.seekdatasheet.com. Oct, 2013.

[10] Altpll megafunction. [EB/OL]. http://www.altera.com/. Oct, 2013.

Design and implementation of Rapidio hardware interface based on FPGA+DSP

Yu Huidong, Gong Haoyan, Wang Shulei

(Navy Troop 92145, PLA, Shanghai 200080, China)

RapidIO Protocol has been widely used in high-performance embedded systems because of its high transmission efficiency, low system cost and good system stability. The traditional RapidIO bus is dedicated to realizing of backplane interconnection such as between devices, between boards or between subsystems in the same chassis or within the same system. In order to maintain the consistency of the bus for the interconnection of multiple embedded systems, and to make RapidIO bus applicable between chassis, The RapidIO bus range needs to be expanded. In this paper, the implementation scheme of general RapidIO interface hardware based on FPGA+DSP architecture is proposed. By introducing the photoelectric module, the RapidIO LVDS signal is converted into an optical signal, and the signal is transmitted between the chassis, which successfully expands the RapidIO transmission distance and solves the problem that the RapidIO transmission distance is limited to in one chassis. The RapidIO interface implementation scheme from the hardware aspect is expounded. Finally, the experimental platform is built to test the connectivity of the implemented RapidIO bus, which proves the feasibility of the scheme.

TP393.0

A

1003-4862(2022)01-0049-05

2021-03-17

余晖冬(1985-),男,研究生,助理工程师,主要从事通信技术。E-mail:yuhuidong1115@163.com