FPGA在数据重排中的跨时钟处理

2021-10-20游斌相廖育富任午龙

游斌相 廖育富 任午龙 马 婕

(四川九洲空管科技有限责任公司 四川绵阳 621000)

0 引言

数据重排算法是雷达信号处理[1]中最常用的算法之一,要实现数据重排,首先需要把数据缓存起来,然后根据重排顺序依次读出数据,这一过程既要求高缓存也要求高速率。DDR3 SDRAM[2]作为一种高速、高带宽缓存器在计算机行业有着广泛应用,正好符合数据重排高速高缓存的要求。FPGA是当前雷达信号处理[3-4]最常用的处理器之一,能很好地满足大带宽、高采样率及多通道信号处理等要求。在FPGA上实现数据重排算法过程中,会遇到跨多时钟域问题,既有逻辑时钟域,也有DDR时钟域,还有传输接口时钟域,处理好跨时钟域问题,也是实现数据重排的关键。

1 数据重排设计

1.1 快时间采样与慢时间采样

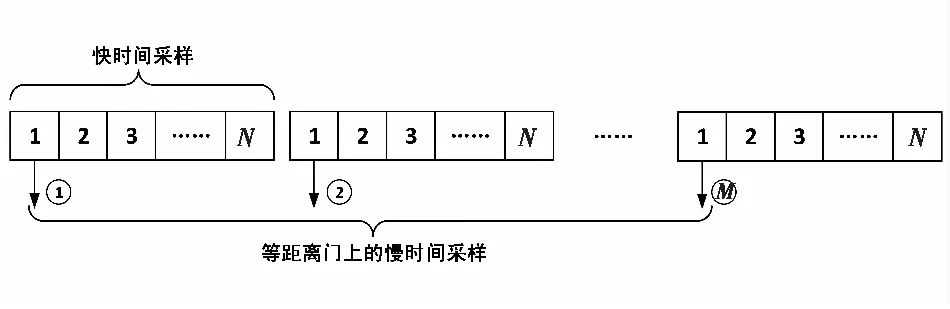

在脉冲体制雷达中[5],通常会连续发射多个脉冲信号构成一个脉冲序列,脉冲之间的时间间隔为PRI(Pulse Repetition Interval),其导数就是脉冲重复频率PRF(Pulse Repetition Frequency)。针对一个脉冲回波的采样称为快时间采样。快时间采样间隔为Ts,是采样率的导数,距离单元间隔为ΔR=cTs/2。针对多个脉冲回波等距离维的采样称为慢时间采样,采集数据所需要的时间为M·PRI,通常称为相参处理时间(CPI:Coherent Processing Interval)。例如以M个脉冲作为一个序列,每个脉冲有N个采样点,其快时间采样和慢时间采样如图1所示。

图1 快时间采样与慢时间采样

1.2 数据重排基本原理

数据重排[6]通常以一个CPI为周期进行处理,假设一个CPI时间段内有M个脉冲,每个脉冲有N个数据点,则数据重排前后顺序关系如图2所示。数据重排前的顺序如图2(a)所示,脉冲内的先后关系同慢时间采样,脉冲间的排序规则与脉冲先后关系有关,先接收到脉冲回波排序靠前,后接收到脉冲回波排序则靠后。数据重排后的顺序如图2(b)所示,其排序规则同慢时间采样,距离单元小的排序靠前,距离单元大的则靠后。

图2 数据重排前后关系

1.3 数据重排实现过程

要实现慢时间采样或数据重排,必须先把所有数据提前缓存好,本设计中使用一片DDR3来做缓存,在FPGA中例化后的地址位宽为25bit,数据位宽为128bit,一个地址刚好存放和差差三个通道的IQ数据。为便于排序操作与地址控制,设计复合地址,将地址划分为行地址和列地址,其中高8bit为列地址,低17bit为行地址。每一列存放一个脉冲数据,最多可存放256个脉冲序列,每个脉冲最多131072个数据。

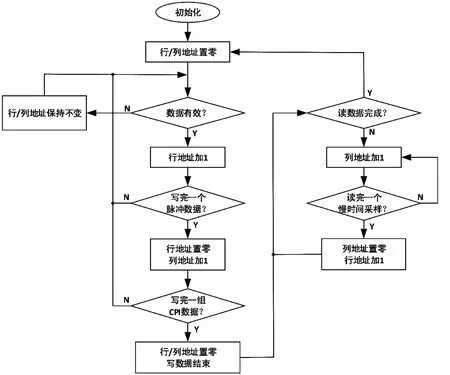

图3给出了数据重排过程中DDR地址控制流程图,输入数据缓存时,从第0行第0列开始写入数据,写入一个数据行地址加一,当写完一个脉冲数据时,列地址加一,行地址清零,接着按照该方法写入第二个脉冲数据,直到一组CPI数据写完,然后开始读出数据。读取数据时,则按照慢时间采样规则依次从DDR3中读出数据,从第0行第0列开始读出数据,保持行不变,列加一依次读取,当完成一次慢时间采样读取时,行加一,列清零,然后接着往后读取数据,直到所有数据读完。

图3 DDR地址控制流程图

2 FPGA跨时钟处理

跨时钟域处理[7-8]是FPGA信号处理的重点和难点,如果处理不当,就会出现亚稳态[9],从而导致数据出错,最终得到一个错误的结果。本方案中涉及了三个不同时钟域,分别是用户逻辑时钟user_clk,DDR时钟ddr_clk以及PCIe时钟pcie_clk。其中,用户逻辑时钟频率高达240MHz,该时钟域主要负责信号处理;DDR时钟频率有200MHz,略小于用户逻辑时钟,该时钟域负责DDR模块的读写操作;PCIe时钟频率最小,仅有125MHz,该时钟域负责PCIe模块的数据传输控制。

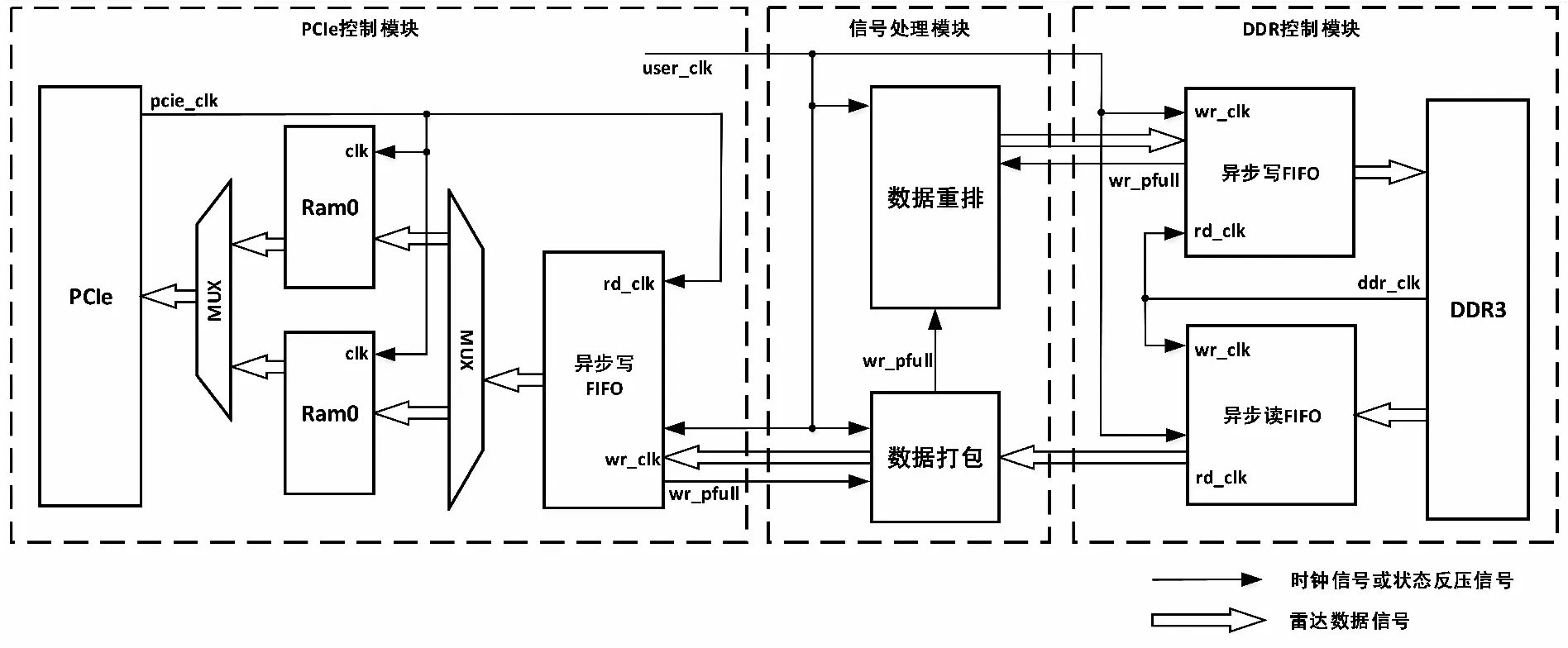

图4给出了跨多时钟域处理的逻辑框架图,共包含三个模块,分别是:PCIe控制模块、信号处理模块及DDR控制模块。整体采用流水线方案设计,极大提高了信号处理及传输效率。

图4 跨多时钟域处理逻辑框架图

信号从信号处理模块出发,首先通过异步FIFO写入到DDR3中。对该异步写FIFO来说,写入时钟大于读取时钟,所以写入数据的速度大于读取数据的速度,为避免丢失数据,需要一个状态反压信号。当该FIFO即将写满时,把wr_pfull信号拉高,并回传给数据重排模块,若数据重排模块检查到该信号为高,则停止往DDR模块写入数据, 等到wr_pfull为低时,再继续写入数据。当所有数据都写入DDR后,再根据数据重排规则,依次从DDR3中读出数据,读出的数据通过异步FIFO做跨时钟域处理后,再传输到信号处理模块做打包处理。

数据打包模块会提前准备好帧头,当接收到数据后,将帧头与数据拼接到一起,然后发送给PCIe模块。PCIe接收端首先是个异步FIFO,该FIFO的读时钟比写时钟慢,为避免丢失数据,同样需要一个反压信号。当数据打包模块接收到PCIe模块回传的反压信号时,暂停发送数据,同时将该信号转发给数据重排模块,让其停止对DDR3的读取控制,直到wr_pull信号拉低时,再接着运行。

PCIe模块接收到打包数据后,首先进行异步FIFO跨时钟处理,然后经过乒乓操作送到PCIe接口,最后发送给上位机。乒乓操作是FPGA开发中常用的一种数据缓冲及控制技术,通过输入、输出选择单元及两个RAM的读写控制,达到数据的缓冲及控制目的。

3 仿真分析

3.1 数据重排仿真

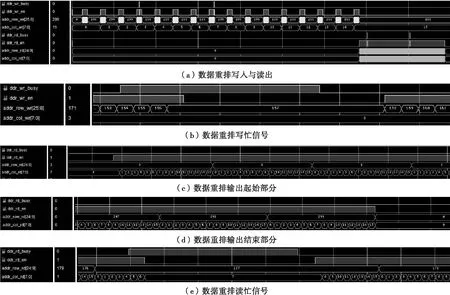

根据前文所述,模拟了一个单通道数据重排、打包及PCIe发送过程。每组CPI有16个PRF,每个PRF有效数据长度均为300。数据重排仿真结果如图5所示,图5(a)为数据重排整体写入与读出的地址控制仿真结果,从图中可以很明显地看出,共输入了16个脉冲信号,第1个脉冲写入第0列,第2个脉冲写入第1列,直到最后一个脉冲写入第15列,完成数据写入操作。图5(b)给出了写忙信号时的DDR地址控制,当忙信号到来时,暂停信号写入,同时保持DDR写入地址不变,直到忙信号结束时,再接着写入信号,DDR写入也跟着地址同步变化。图5(c)和图5(d)给出了数据重排输出地址控制的仿真结果图,按行读取,每一行读取16个数据,直到300行数据读取完成。图5(e)为读取忙信号时的DDR地址控制,当读取忙信号到来时,停止数据读取,保持DDR读取地址不变,直到忙信号结束后,再接着读取相关信号。

图5 数据重排写入与读出

3.2 数据打包仿真

数据打包模块仿真如图6所示,图6(a)给出了数据打包模块的输入与输出信号,输入信号为数据重排后的信号,输出数据为打包后的信号。图6(b)为输入PCIe忙信号时的仿真图,当输入PCIe忙信号拉高时,输出数据保持不变,直到忙信号拉低后,继续输出。图6(c)给出了打包忙信号拉高时的仿真时序图,当打包信号忙时,信号会暂停输入,直到忙信号结束才继续输入信号。

图6 数据打包输入及输出

3.3 乒乓操作仿真

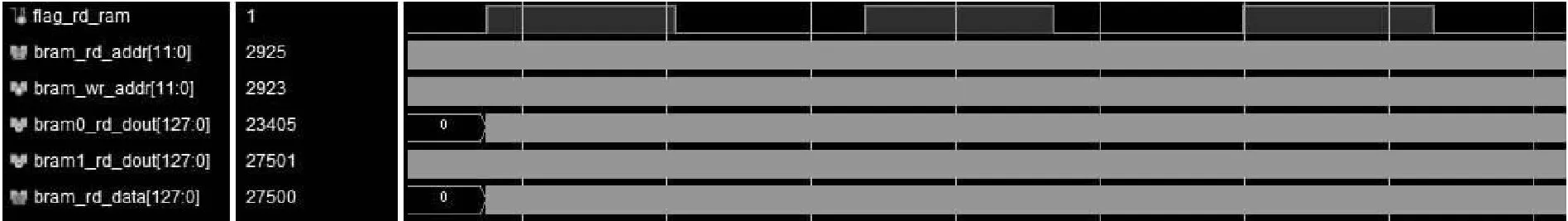

打包后的数据通过异步FIFO和乒乓操作后会传输到PCIe模块,最后通过PCIe接口将数据发送到PC端。图7给出了乒乓读写的仿真结果图,两个ram读写地址相同,当flag_rd_ram为1时,写入数据到ram0,同时输出ram1的结果;当flag_rd_ram为0时,写入数据到ram1,同时输出ram0的结果。

图7 乒乓读写仿真结果

4 结束语

本文结合雷达系统的实际需求,基于FPGA开发平台并利用DDR3实现数据重排算法逻辑架构设计,设计包含:PCIe控制模块、信号处理模块及DDR控制模块。整体采用流水线方案设计,结合信号反压等跨多时钟域处理方法,实现了数据重排算法的逻辑设计,通过仿真分析和板级实测,满足项目实际使用需求。同时,该设计方案有望在类似的雷达系统中推广使用。