芯片级原子钟的研究进展

2021-10-14刘雅丽李维武腾飞李新良

刘雅丽,李维,武腾飞,李新良

(航空工业北京长城计量测试技术研究所 计量与校准技术重点实验室,北京 100095)

0 引言

微型定位导航授时(Micro positioning,navigation and timing,Micro-PNT)系统是确定时间和空间的关键技术,以其体积小、功耗低、精度高的优点在国民经济、军事领域和国家安全等方面具有广泛的应用潜力[1]。传统的全球卫星导航系统(global navigation satellite system,GNSS)存在易受干扰和遮挡的问题,而Micro-PNT系统可以很好地解决上述问题,可应用于GNSS信号不佳的山洞、深渊、森林等极端环境。另外,Micro-PNT系统可以极大地降低惯性导航系统的累积误差,延长其单独工作时长。Micro-PNT系统结合了全球卫星导航系统与惯性导航系统,以低功耗、微体积、高精度的芯片级原子钟(chip scale atomic clock,CSAC)为时钟基础,发播定位导航授时信号[2-3]。同时,芯片级原子钟向接收机、加速度计和陀螺仪等发送高精度的时钟信号,也将大大提升Micro-PNT系统的性能[1]。

芯片级原子钟包括芯片级微波原子钟和芯片级光学原子钟。芯片级微波原子钟是传统相干布居囚禁(Coherent Population Trapping,CPT)原子钟,它基于相干布居囚禁原理,通过微波频率信号来调节两相干光场,使其与原子基态的两超精细能级跃迁至同一激发态能级的频率发生共振,从而获得精度高的标准频率信号的输出[4]。与小型恒温晶振相比,芯片级微波原子钟在体积和功耗上与之相当,但是长期稳定度要比其高3个量级以上。另外,其体积和功耗要比铷原子钟小近2个量级[5-6]。芯片级光学原子钟是一种作为参考标准的原子能级跃迁频率处于光频波段的原子钟,其工作原理与微波原子钟相似,除了跃迁频段不同之外,其频率发生器是稳频激光器而不是微波原子钟的晶体振荡器。因为光学频率比微波频率要高5个量级,故芯片级光学原子钟比芯片级微波原子钟具有更高的理论精度。本文对比了国内外芯片级原子钟的研究现状,阐述了研制的难点及需要突破的关键技术,最后对芯片级原子钟的发展趋势进行了展望。

1 芯片级原子钟研究现状

1.1 国外研究现状

1976年,Alzetta等人[7]通过激光与钠原子的作用研究了气室中钠原子的三能级结构,并且首次观察到了CPT现象。

1993年,加拿大科学家Cyr等人[8]提出了利用CPT原理来研制碱金属原子钟的建议,从此人们展开了对CPT原子钟的广泛研究。

1995年,Westinghouse公司(现在的Northrup-Grumman公司)的一个小组[9-10]率先在CPT原子钟中使用垂直腔面发射激光器(Vertical Cavity Surface-Emitting Lasers,VCSEL)来代替放电灯,减少原子钟的功耗和尺寸。他们使用微型玻璃气室制备微波腔,得到的物理装置体积为16 cm3,功耗为几百毫瓦,时钟的短期稳定性为2×10-11τ-1/2,104s内的长期漂移为3×10-12。

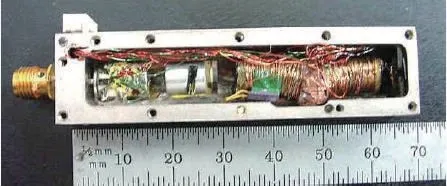

2000年,美国国家标准与技术研究院(National Institute of Standards and Technology,NIST)的Kitching等人[11]提出了芯片级原子钟的构想。他们研究了Cs原子蒸气中的暗线共振,利用VCSEL发出的光激发共振,并且通过直流吸收的变化来检测共振,从而形成了非常简单的物理封装,如图1所示。其体积小于1 cm×1 cm×2 cm,功耗远远小于100 mW,在1 s到10 s的积分时间内显示出3×10-11的频率不稳定度。2001年[12],他们设计了一款简单、紧凑、低功耗的CPT原子钟,物理封装如图2所示。装置体积为6.6 cm×1.6 cm×1.3 cm,在没有热控制的情况下功耗小于30 mW,100 s内的不稳定度为1.3×10-10。

图1 NIST的芯片级原子钟物理封装示意图

图2 NIST的CPT原子钟微型系统

2002年,美国国防部高级研究计划局(DARPA)启动了芯片级原子钟的研制计划,包括NIST在内的多个团队参与了该计划[5]。

2004年,NIST的Knappe等人[13]研制出了首个芯片级原子钟原理样机,结构如图3所示。从下到上依次由激光组件、光学组件、原子气室、光电探测组件垂直堆叠而成,整个物理系统体积为9.5 mm3,系统功耗75 mW,短期稳定度达到了2.4×10-10τ-1/2,长期不稳定性频率漂移约为-2×10-8/天。

图3 首个芯片级原子钟原理样机结构图

2008年,Teledyne Scientific公司[14]成功研制出芯片级原子钟原理样机,如图4所示。其体积小于1 cm3,功耗小于30 mW,积分时间为1 h的Allan偏差小于1×10-11,满足了DARPA目标,但是该原理样机输出的时钟频率并不是标准的10 MHz,不适合量产。

图4 Teledyne Scientific公司研制的芯片级原子钟

芯片级原子钟成为各国竞相研发的、具有战略意义的装置,其中,美国的技术水平处于全球领先地位。此外,据国外公开报道,欧盟、日本也实现了芯片级原子钟原理样机的研制。2010年,欧盟的Schori等人[17]研制出了芯片级原子钟样机,如图5所示。其短期频率稳定度为7×10-11τ-1/2(τ<100 s)。2018年,日本Hara等人[18]将3.5 GHz的薄膜体声谐振器应用到一个压控振荡器上,作为小型化原子频率标准的本端振荡器,研制出了芯片级原子钟样机,1 s内频率稳定度为2.1×10-11。

图5 欧盟研制的移除磁罩的芯片级原子钟样机

2011年1月18日,Symetricom技术研究中心[15]宣布SA.45 s芯片级原子钟(CSAC)全面上市。SA.45s是第一种商用的CSAC,功耗小于125 mW,短期稳定度小于3×10-10τ-1/2,其实物图和物理封装图如图6所示。

图6 Symmetricom的SA.45s芯片级原子钟

过去几十年,美国的DARPA在原子钟技术的进步和微型化方面投入了大量资金,研制出芯片级原子钟并且已上市,具有体积小、重量轻、低功耗等特点,并提供前所未有的授时稳定性。然而,由于物理特性与设计相关,第一代芯片级原子钟的性能从根本上受到了限制,由于它存在上电频差,使得上电后需要6~12 h校准,同时由于存在温漂和频漂,其有效工作时间只能持续3~6 h。校准要求和频率漂移会产生授时误差,因此难以在便携式封装中达到最高程度的准确性和可靠性。DARPA认为稳定性更高的芯片化原子钟将具有更广阔的的应用前景,在此背景下,DARPA在2015年年底启动了“高稳原子钟”(ACES)项目,探索下一代电池供电型芯片级原子钟的开发。ACES项目分为三个阶段:在第一阶段,在实验室内研制出性能优越的关键部件;在第二阶段,将原子钟组件集成并将其封装在一个不超过30 cm3的包中;在第三阶段,将相关电子设备整合到一个体积不超过50 cm3的包中。ACES项目重点关注原子钟频率温度系数、频率漂移、频率复现性,与现有原型相比,关键性能参数提高了1000倍。

2019年8月,DARPA宣布ACES项目取得突破性进展,美国国家航空航天局喷气推进实验室团队开发出的芯片级原子钟受温度和环境因素干扰小,定位精度是之前原子钟的100倍;霍尼韦尔公司成功开发了能够使原子钟小型化的精密原子传感器;NIST开发的芯片级原子钟也比先前的原子钟性能优越。NIST团队展示了一个实验性的光学原子钟[16],如图7所示,它只由三个小芯片构成,可支持电子器件和光学器件。不同于工作在微波频率下跟踪Cs原子振荡的标准原子钟,光学原子钟可运行在更高的频率下并提供更高的精度,因为它们可将时间分成更小的单位。该光钟使用激光跟踪Rb原子振荡,这些Rb原子被限制在一个由微型玻璃容器构成的蒸汽室中,玻璃容器直径3 mm,位于硅片顶部。在时钟芯片的“心脏”内,两个频率梳就像齿轮一样将Rb原子的高频光学“滴答”转换成较低的微波频率。该时钟除了提供更高的准确度(大约比当前基于铯的CSAC高50倍),功耗更低,仅275 mW。

图7 芯片级光学原子钟结构图

1.2 国内研究现状

国内研究芯片级原子钟起步较晚,主要研究机构有中国科学院武汉物理与数学研究所、成都天奥电子股份有限公司、航天科工203所、北京大学等单位[19-23]。

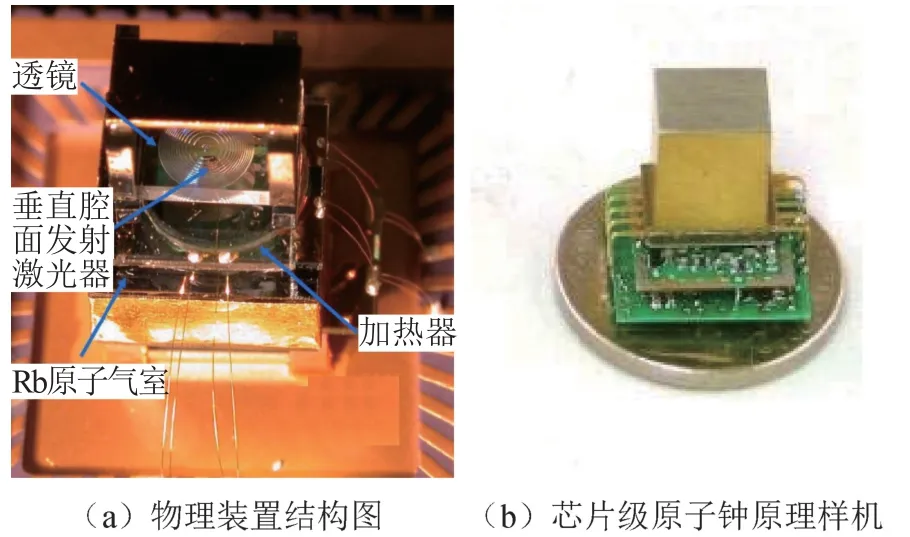

2006年,中国科学院武汉物理与数学研究所的顾思洪小组[19]成功研制出国内首台CPT原子钟原理样机。之后,他们一直致力于研制具有重要应用背景的芯片级原子钟样机,并且于2013年,成功研制出芯片级原子钟样机。2017年,该组研制的CPT原子钟[20]整机体积约为19 cm3,功耗约为210 mW,稳定度约为1.04×10-10τ-1/2,如图8所示。

图8 武汉物数所芯片级原子钟样机

成都天奥电子股份有限公司于2006年开始展开对芯片级原子钟的研究,2014年实现了芯片级原子钟原理样机研制,其外形尺寸45 mm×36 mm×14.5 mm,功耗小于0.6 W,百秒输出频率稳定度为5×10-10[21]。

2015年,航天科工203所研制出第一代芯片级原子钟样机,其功耗为3 W,短期频率稳定度为8×10-11τ-1/2。经优化后,原子钟体积小于20 cm3,功耗小于1 W,短期频率稳定度为3×10-11τ-1/2~5×10-11τ-1/2[22],实现了批量化生产。

此外,北京大学、苏州大学、中国科学院上海微系统与信息技术研究所[24-26]等研究团队都已研制出芯片级原子钟原理样机。

上述国内的研究,主要还是集中在芯片级微波原子钟领域,目前国内还没有芯片级光学原子钟的报道。

2 芯片级原子钟关键技术

芯片级微波原子钟与传统的小型原子钟相比,将铷(或铯)光源换成了微小的VCSEL激光器,将体积较大的微波谐振腔换成了通过稳定的微波信号源来调制的VCSEL激光器,将铷(或铯)的玻璃泡换成了便于集成的微型的MEMS铷(或铯)原子气室。芯片级微波原子钟在保证频率精度和稳定度的情况下,功耗由小型原子钟的大于10 W减小到100 mW以下,体积也由小型原子钟的大于230 cm3缩减到10 cm3以下,应用领域更加广泛,但也面临着新的技术挑战[27]。芯片级原子钟的研制需要突破多项关键技术,主要包括微型原子气室制备技术和微机电系统集成技术等。此外,芯片级光学原子钟中,激光锁定在原子的光学跃迁作为参考,得到光学频率标准。光钟以光学频段作为参考,但是目前只有对微波直接计数的电子元件,还没有对光学频段激光计数的元件。因此,光学原子钟的实现,需要考虑将光学频段的标准转换到能够直接计数的微波频段。而光学频率梳可以将光学频率转换到微波频率。因此,要实现芯片级光钟,还需要芯片级光学频率梳。

2.1 微型原子气室制备技术

芯片级原子钟的核心物理部件是原子气室,原子气室的性能和物理尺寸对于芯片级原子钟的原子物理系统的微型化、低功耗和系统集成化有直接的影响[28]。利用微电子机械系统(MEMS)超精细加工技术来制备原子气室,使原子气室的物理尺寸越来越小,便于微型化和集成化。目前芯片级原子气室的制备技术还存在诸多问题,主要包括定量填充高纯度碱金属、精确控制气体组分、多层结构的键合技术等技术难点。

随着MEMS技术的发展,原子气室的尺寸越来越小,可以增多单批次加工数量,但是由此带来了新的问题,即碱金属原子分装不均匀、填充气体的压强及配比偏离增大。缓冲气体压强及配比对微型原子气室的性能有很大影响,但是在封装过程中,原子气室内的缓冲气体压强很难进行监控。针对原子气室批量加工需求,一方面需要改进碱金属填充方法,解决定量填充高纯度碱金属的问题;另一方面,需要深入研究原子气室内多种气体混合充制的动力学过程,并且通过在线定量分析手段对原子气室封装过程中的气体充制进行实时监测和动态调整,从而实现气体组分的精确控制[29]。

研制微型原子气室的另一个难点是在实施碱金属和缓冲气体的充制过程中保证原子气室的气密性。为解决此问题,需要结合碱金属填充技术,通过优化原子气室的结构和工艺,来提高原子气室的气密性。

2.2 微机电系统集成技术

芯片级原子钟系统主要由物理系统和电路系统两大部分组成。物理系统是芯片级原子钟的核心,主要包括VCSEL激光器、光学元件、碱金属原子气室、磁场和磁屏蔽系统、温控系统以及光电检测器等。采用传统的工艺很难将物理系统的各元件依次叠放成堆叠式结构,因此很难实现微型的物理系统。而MEMS技术的发展,使原子物理系统的各元件可以更好地集成封装,从而实现芯片级原子钟的微型化。物理系统在集成封装过程中,存在的难点是既要实现芯片级原子钟的微型化,又要保证芯片级原子钟的频率稳定度和功耗。因此,在封装过程中,要充分考虑系统的体积、功耗以及频率稳定度。

芯片级原子钟的电路系统集成需要保证对VCSEL激光器输出的激光频率实施稳频,对物理系统实施稳定的温度控制,对微波链前端的晶振输出频率使用微波和CPT信号进行反馈[5],因此,电路系统对芯片级原子钟的稳定工作非常重要。电路系统集成存在的一个难点是微型原子气室和激光器及其各自的温度传感器之间存在温度梯度,通常激光温度是通过附近的温度传感器测量的,原子气室温度由温度传感器(热敏电阻或Pt膜)监控,尽管温度传感器尽可能地靠近要控制的元件,但是不可避免地存在一些空间上的间隔,这导致了它们之间存在有限的热阻。即使传感器温度完全稳定,原子气室和激光器的温度波动仍可能存在,影响芯片级原子钟输出频率的长期稳定性[30]。另外一个难点:电路系统集成过程中,在保证芯片级原子钟信号质量的前提下,减小电路的体积和功耗。

2.3 芯片级光学频率梳技术

光学频率梳在光学原子钟中具有重要作用。光学频率梳在时域上是飞秒量级的脉冲,在频率上是一系列等间隔的频率梳尺。因为探测器响应速度的限制,光学频率无法直接被探测,所以即使有精准的光学频率标准,如果无法将光学频率传递出去,也就不能形成实用化的光学原子钟。光学频率梳链接了微波频率和光学频率,通过光学频率梳可以将光学频率转化成微波频率,实现实用化的光学原子钟。同样的,芯片级光学频率梳可以在芯片尺度上实现光学频率和微波频率的链接,是芯片级光学原子钟的核心组件。

芯片级光学频率梳近几年发展很快,特别是基于克尔效应的微腔光学频率梳发展迅速。2018年,康奈尔大学Lipson课题组报道了在混合III-V/氮化硅平台上采用电池驱动的集成克尔微腔光梳[31],光梳的集成性能大幅提高。2020年6月,在美国加州理工学院、加州大学圣芭芭拉分校以及瑞士洛桑联邦理工学院三方组成的研究团队的共同努力下,成功实现了芯片化微腔孤子光梳“启钥”运行[32]。尽管近两年芯片化光频梳取了得较大进展,但是整体上芯片级光学频率梳技术还不是特别成熟,这在一定程度上阻碍了芯片级光学原子钟的发展。

芯片级光学原子钟受本身的尺寸、功耗等条件限制,迫切需要可在片上集成(通常是在硅片上集成)的芯片级光梳。当前面向平面集成的高品质因子氮化硅微腔制备技术。此外,国外“启钥”运行的光频梳,在自注入锁定下,激光器的频率可以牢牢锁定在微腔的谐振频率上,虽然打开激光器的开关,就能自动寻找锁模状态并保持稳定运行,但是这种装置需要花费较长时间安装,且需要较长时间手动准直激光器和谐振腔,并对系统进行测试和包装,以确保其参数保持稳定。因此,进一步研究性能稳定、可批量生产的芯片级光学频率梳是实现芯片级光学原子钟走向实用化的关键。

3 总结与展望

芯片级原子钟作为一种小型、低功耗、高精度的时间频率设备,具有广阔的应用前景。本文介绍了芯片级原子钟国内外的研究进展及研究现状,国外已规模化生产芯片级原子钟,国内目前多家单位也都已研制出了芯片级原子钟的原理样机,但是与国外还存在一定的差距(主要在性能上,国外已实现商品化)。虽然近年来芯片级原子钟技术取得了长远的发展,但是还有多项关键技术需要突破,包括微型原子气室制备技术、微机电系统集成技术和芯片级光学频率梳技术等,芯片级原子钟的稳定性和可靠性尚有提高的空间。

NIST提出了下一代芯片级原子钟——芯片级光学原子钟。芯片级光学原子钟的频率更高、准确度更高,它们把时间分割成更小的单位,并且有一个高“品质因子”,有望成为未来重新定义秒的基础。NIST的铷原子气室和两个频率梳是用与计算机芯片相同的方法微加工的,这意味着它们可以支持电子和光学的进一步集成,并且可以大规模生产,这是一条通向商业上可行的紧凑光学原子钟的道路。随着技术的进一步发展,芯片级光学原子钟有可能变得足够小,便于手持使用,最终可能会在导航系统和电信网络等应用领域取代传统的振荡器,成为卫星上的备用光学原子钟。