基于新型微组装技术的X 波段高隔离开关的设计

2021-08-29刘博源黄昭宇季鹏飞许庆华张晓发袁乃昌

刘博源 ,黄昭宇 ,江 云 ,季鹏飞 ,许庆华 ,张晓发 ,袁乃昌

(1.国防科技大学 电子科学学院CEMEE 国家重点实验室,湖南 长沙 410003;2.湖北三江航天险峰电子信息有限公司,湖北 孝感 432000)

0 引言

随着现代雷达通信系统对微波有源器件日益增长的需求,经过从21 世纪五六十年代以来的发展,已经逐渐从功耗高、重量大转向小型化、高集成、高性能、多功能新型化器件[1]。同时,工艺水平的提升,也使得器件的加工精度和批量化产品一致性以及高可靠性得到极大程度的保障。这其中,由于对电路不同路径的选通作用,微波开关被广泛应用在收发组件中[2]。

性能优良的微波开关对于提升射频前端集成度的作用是显著的,这是因为开关与接收或发射天线直接关联,其结构直接影响到了天线尺寸以及在相同体积内路径的数量[3]。对于本文中所涉及的多路开关,为使每一路开关和与之相邻的其他路的开关能够避免信号大规模串扰,就需要对模块整体结构进行优化设计。具体而言,在平行路径之间分腔,对于提升电路电磁兼容性是至关重要的[4]。除此之外,在电路层面上,利用高介电常数的新型多层板和微组装设计,可以在每一路的垂直方向上将控制电路和射频电路分离开,这样就可以防止直流信号与射频信号之间的混叠,路径切换受阻,信噪比下降,严重限制微波开关正常工作。

考虑到上述情况,本文设计的开关通道电路需要大体上从电性能和结构两个方面分别进行设计,并在各自发挥最佳性能优势时优化整合,找到可以最大限度满足性能指标的模块设计思路[5]。由于所设计的模块需要进行加工,因而还需要把所使用复合材料的稳定性和工艺设备的加工误差等可实现性方面问题考虑在内[6]。最后,本文设计并制作了X 波段高隔离度射频开关组件,实现了四通道开关组件同时工作的模块化、集成化的全流程设计,有利于提升系统组件的功能化和灵活度。

1 开关通道电路与结构设计

本文所设计的组件由4 个相同且独立的开关电路组合而成。电路设计为两部分,一部分为P 型半导体-本征半导体-N 型半导体(Positive-Intrinsic-Negative,PIN)二极管[7]并联组成开关电路,达到低插损、高隔离、大功率要求;另一部分是开关导通和关断的控制部分,含驱动器和晶体管到晶体管逻辑(Transistor-Transistor Logic,TTL)、电源等。驱动器的电源为+5 V、-28 V。TTL 电平输入,驱动器[8]输出高低电平来控制开关的导通和关断,实现电路开关性能。

1.1 开关通道的微波特性

开关是一种插入损耗(插损)受PIN 管导通或截止情况影响的器件[9],插损(Insertion Loss,IL)的定义为输入功率Pin和导通状态输出功率Pout,on的比值再取对数,即:

通常来讲,导通态插损要小,截止态插损要大。

开关的回波损耗是关于功率沿输入路径返回的量度。回波损耗(Return Loss,RL)定义为输入功率Pin与反射功率Pr的比值再取对数,即:

开关的隔离度(Isolation,ISO)可以认为是在断开条件下的插入损耗[10],对数值为负,即:

1.2 开关通道电性能参数指标

分析4 路开关组件在实际应用中的性能,对其中关键参数进行了指标设定:频率范围为8~12 GHz;插入损耗≤1.5 dB;幅度不平衡≤±0.8 dB;相位不平衡≤±5°(温度25 ℃);关断隔离度≥50 dB(温度25 ℃);切换速度≤500 ns(温度25 ℃);驻波比≤1.8;功率容量≥20 W(连续波,温度25 ℃);电源电压Vcc 为6 V,Vee 为-30 V;控制电压Vc 为6 V;最大输入信号功率(Pinmax)为43 dBm;封腔后尺寸为长(L)≤125 mm,宽(W)≤25 mm;控制信号为TTL(Transistor-Transistor Logic)电平:-0.3~-0.8 V/+5 V。

1.3 开关通道尺寸指标

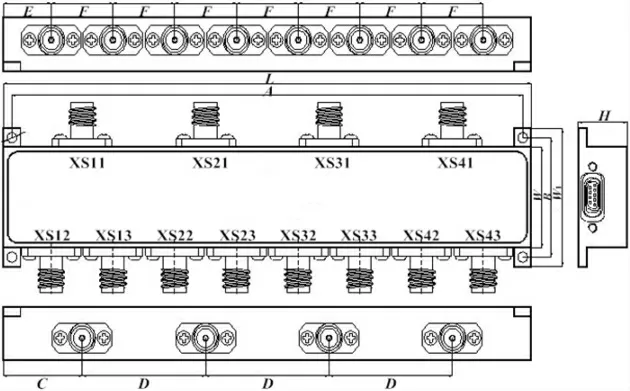

考虑到开关通道组件尺寸设计以达到多方面应用上的使用需求,经过对电磁兼容的定性分析后,对其进行紧凑型设计,采用微组装技术对其进行小型化设计。外形和引出端排列图以及对应尺寸符号长度大小分别如图1 和表1 所示。

图1 开关组件外形和引出端排列图

表1 尺寸符号长度大小

根据四通道开关组件的尺寸,对盒体也做了上述小型化设计,以满足在更为复杂电磁系统中轻量化和紧凑型布局[11]。

1.4 开关通道架构设计

重构开关组件含4 组独立的二选一开关,分别为K1、K2、K3、K44个大功率二选一开关。4个二选一开关受同一个TTL 电平控制联动工作。发射时,均为XS2到XS1 导通,XS3 端指向吸收态并与XS2 为隔离状态;接收时均为XS1 到XS3 导通,XS2 端指向吸收态并与XS3为隔离状态。开关组件电性能工作原理图如图2 所示。

图2 开关组件电性能工作原理图

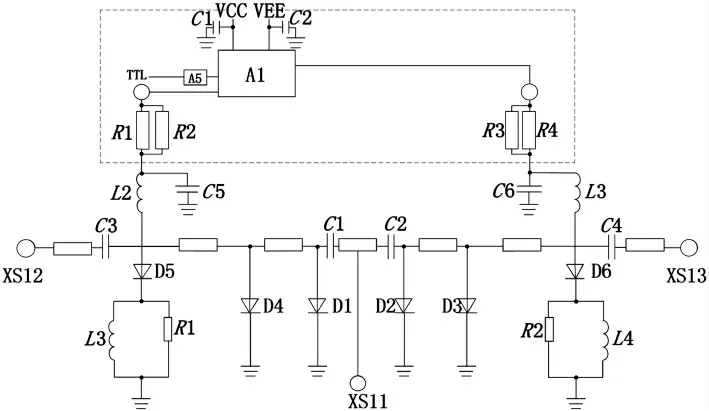

将驱动电路添加入控制模块中,通过高低电平转换实现信号从主路到任一旁路的切换导通。该开关通道架构设计如图3 所示。

图3 开关通道电路原理图

将上述通道进行器件化,首先通过对其中任一通道的主路和支路端加入隔直电容,防止电源中的直流分量流入开关造成功率过大而烧坏器件[12-13]。其次,添加二极管来对电路起到稳压和保护的作用,避免感性负载在通断电过程产生高反压对电路造成伤害。在支路输出端口加入扼流线圈,防止电源的杂波随着有用信号流出[14]。驱动器控制端放置接地电容是为了防止射频信号回流入电源造成损伤。

加电使用前,要使控制输入端为低电平。同时,为保证速度,要求输入TTL 信号:上升沿时间(tr)≤20 ns,下降沿时间(tf)≤20 ns,高电平(Vtop)≥4.0 V。

控制信号的工作频率≤30 MHz,典型工作频率10 MHz。另外,内部所有射频端口均有隔直电容,无需外加。-5 V电源管脚就近外加1 μF 滤波电容。

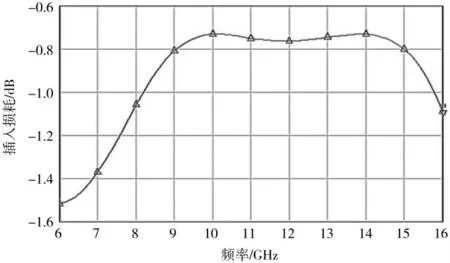

2 开关通道电路建模与仿真

该组件的关键技术为高频开关电路损耗、低反射和散热。由于功率高,因此要求电路损耗小,端口反射小。电路采用三级PIN 二极管级联的方式[15],最后一级为吸收式设计,开关关断隔离高。为满足带宽需要,对电路通过添加有源电感负载来拓展带宽,以达到对全X 频段的覆盖。根据以上要求,在ADS 电路仿真软件对图3 所示的单通道开关电路进行参数化建模和优化设定高频板、频率参数,根据以往优化经验,调整具体参数值,通过优化设计,得到理想的仿真结果。导通损耗曲线如图4 所示,驻波曲线如图5 所示,关断隔离曲线如图6所示。

图4 开关电路导通态插入损耗仿真曲线图

图5 开关电路驻波仿真曲线图

图6 开关电路关断隔离仿真曲线图

经过仿真可以看出,对于导通损耗曲线,在整个X波段可以满足不小于1.5 dB的指标要求;在仿真设计中,输入端口的驻波虽然在8 GHz 处未能满足小于1.8的指标要求,但根据以往设计经验,在低频端对其进行了失配设计,是考虑到ADS 无法对电路寄生参量进行仿真分析,由此可以在实际加工过程中实现驻波比下降到理想值;输出驻波比在设计中各频点也均不大于1.8;由仿真结果可知,关断隔离度远远大于指标要求的35 dB,在新型微组装实现技术下,此项指标要求可以得到充分保证。

3 开关通道电路的加工与测试

3.1 电路版图设计

根据建模和仿真优化后得到的尺寸,利用AutoCAD对每一路开关电路绘制,抽取其中一路作为绘制对象,得到如图7 所示结构图形。

图7 单路开关电路版图

3.2 复合多层板的设计

利用Altium Designer 对内部线路和分立器件排版和布局,为了减少开关通道组件射频与控制端的高度集成和小型化,并极大程度提升电磁兼容性,因而引入了如图8 所示的复合多层板的设计思路。

图8 复合多层板层叠结构

材料用了多层介质材料,顶层铜箔在0.508 mm 厚FR4 芯板的顶面,另一面铜箔全部蚀刻掉;底层铜箔在0.508 mm 厚FR4 芯板的底面,另一面铜箔全部蚀刻掉;微带金属层在上下两层厚FR4 芯板被蚀刻掉铜箔的中间。合板总厚度约1.5 mm。

3.3 开关通道组件的加工和实测

通过全流程的电路加工和盒体封装,得到的开关组件实物外观图如图9 所示。

图9 开关组件实物外观图

组件盒体4 个开关独立分为4 个腔体,每个开关的两路也采用隔墙分别隔开输出,每个单独的开关内部有内盖板固定热电场,进一步减少电磁干扰,提高隔离度,芯片烧结到钼铜片上,然后再烧结到腔体底部,保证接地良好,散热良好,降低热阻,减少热损。以上措施能很好地满足设计需求,是解决该组件低插损、大动态、高隔离的关键技术。

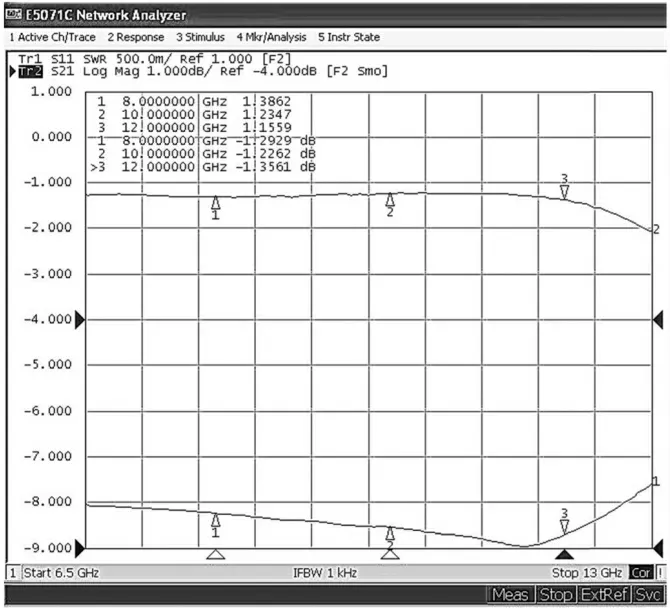

由于受到腔体、带线布局的影响,其仿真结果和实际测试有些差别。切换控制位高低电平,对带线的某部分宽度的进行调试,得到比较满意的指标。实测开关的导通态插损和驻波曲线分别如图10 和图11 所示。

图10 实测导通态插入损耗曲线图

图11 实测驻波曲线图

当通道关断时测试输入输出端口的损耗,并与相邻通道的增益值做差,得到该通道的关断隔离度指标。关断隔离度曲线如图12 所示。

图12 实测关断隔离度曲线图

根据实测曲线可以看出,开关单路插损满足≤1.5 dB的指标要求,关断隔离度在全频段内均大于50 dB。此外,驻波曲线显示,输入输出端口驻波均小于1.8。以上指标均达到了设计要求。

通过调整控制位的高低电平进行通道切换,对四通道中XS1 进行归一化,测试另外三通道XS2、XS3 和XS4的相对归一化通道幅度和相位的差值,得到每个通道的幅相平衡性指标,得到如图13 和图14的测试结果。

图13 实测路间相位一致性结果

图14 实测路间幅度一致性结果

同样地,切换控制位高低电平测试每个通道开关幅度相当于归一化通道值的带内平坦度。

由图14 可知,8~12 GHz 范围内的通道路间相位一致性≤±5°,带内波动≤±0.8 dB,均满足使用要求。

最后,对开关的切换速度进行了实测,如图15 所示。结果显示,在切换支路的瞬时时刻,切换时间被极大限制在200 ns,远达到了指标中不大于500 ns的要求。

图15 实测开关切换时间

3.4 组件与同类产品的性能比较

本文设计的组件是充分利用了微组装工艺,减少了人为因素和精度误差对主要电性能的影响,具有与仿真结果高度一致的优越性。为了突出本文设计产品的优越性,将其与其他X 波段同类产品进行对比,如表2 所示。

表2 本文组件与同类产品性能比较

由表2 可知,本文组件除了可满足四通道同时工作的需要外,在插损、驻波、隔离度、切换速度等指标方面都具备明显优势。在不过多牺牲插损和驻波的前提下,本文设计的产品使高隔离度、高切换速度和大功率容量等性能特点得到了较好展现。

4 结论

针对组件的结构、性能、精度的要求和现有工艺水平、设备仪器条件,该组件确定的微组装工艺方案切实可行,该组件的设计中尽可能地采用标准工艺,既提高组件成熟度,提高可靠性、稳定性,又达到工艺简单易行、降低制造成本的目的。本文设计的开关组件在极大限度满足高隔离度性能前提下,大大缩减了组件尺寸,尺寸仅为123.70 mm×21.20 mm,可以满足复杂多通道系统对逻辑切换控制的紧凑型需求。同时幅相一致性较好,开关响应时间控制在百纳秒范围内,降低了组件多路传输的延迟时间,搭配驱动器输出逻辑信号进行高低电平切换,提升了开关多种组合下同步工作的能力。

另外,盒体与高频电路板采用导电胶贴装,电路板带线与接口采用包金带工艺、芯片采用烧结工艺装配,控制部分的元件采用回流焊工艺烧结到电路板上,组件内部连接件采用绝缘子烧结方式,电路输入输出有隔直电容,上下外盖板采用激光缝焊,有效地避免了电磁干扰,射频泄漏,具有很好的环境适应性。总体来说,所设计的组件可以用于射频前端信号路径同时或分时切换,可广泛适用于微波毫米波军工及民品行业和市场。